TESTI ESERCIZI sulla PRIMA PARTE DI ELETTRONICA 2015-16

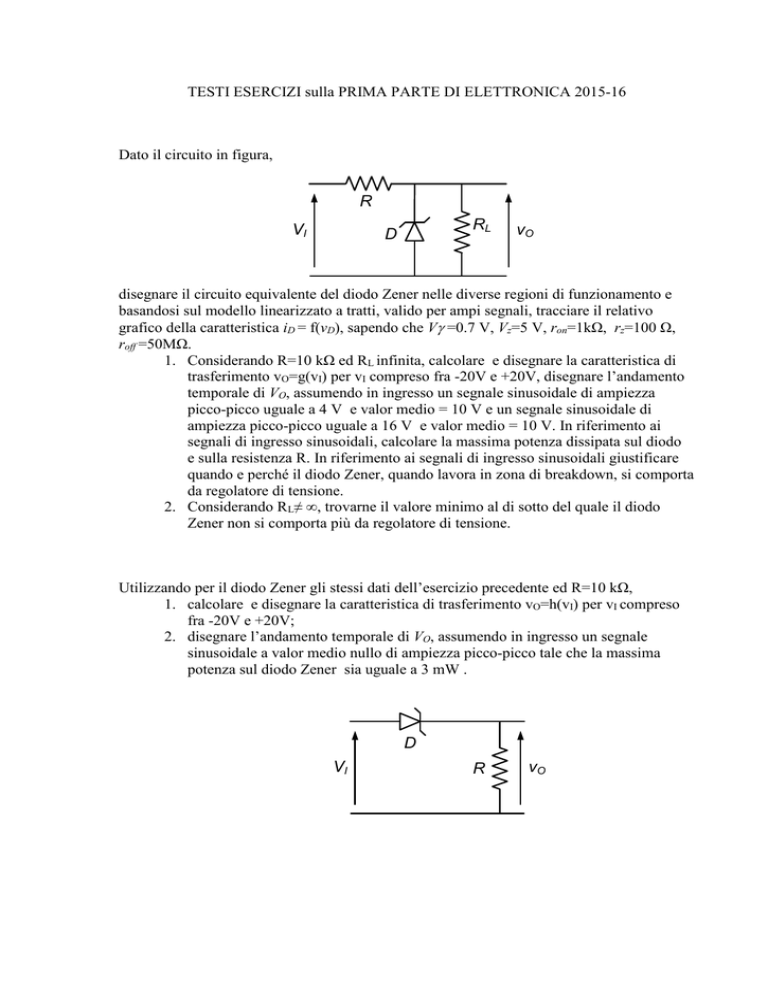

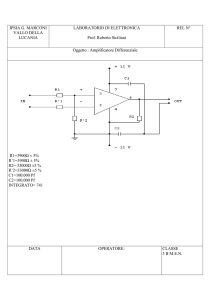

Dato il circuito in figura,

R

VI

RL

D

vO

disegnare il circuito equivalente del diodo Zener nelle diverse regioni di funzionamento e

basandosi sul modello linearizzato a tratti, valido per ampi segnali, tracciare il relativo

grafico della caratteristica iD = f(vD), sapendo che V=0.7 V, Vz=5 V, ron=1kΩ, rz=100 Ω,

roff =50MΩ.

1. Considerando R=10 kΩ ed RL infinita, calcolare e disegnare la caratteristica di

trasferimento vO=g(vI) per vI compreso fra -20V e +20V, disegnare l’andamento

temporale di VO, assumendo in ingresso un segnale sinusoidale di ampiezza

picco-picco uguale a 4 V e valor medio = 10 V e un segnale sinusoidale di

ampiezza picco-picco uguale a 16 V e valor medio = 10 V. In riferimento ai

segnali di ingresso sinusoidali, calcolare la massima potenza dissipata sul diodo

e sulla resistenza R. In riferimento ai segnali di ingresso sinusoidali giustificare

quando e perché il diodo Zener, quando lavora in zona di breakdown, si comporta

da regolatore di tensione.

2. Considerando RL≠ ∞, trovarne il valore minimo al di sotto del quale il diodo

Zener non si comporta più da regolatore di tensione.

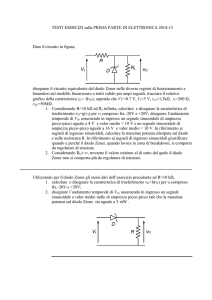

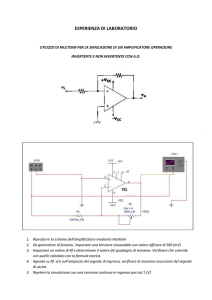

Utilizzando per il diodo Zener gli stessi dati dell’esercizio precedente ed R=10 kΩ,

1. calcolare e disegnare la caratteristica di trasferimento vO=h(vI) per vI compreso

fra -20V e +20V;

2. disegnare l’andamento temporale di VO, assumendo in ingresso un segnale

sinusoidale a valor medio nullo di ampiezza picco-picco tale che la massima

potenza sul diodo Zener sia uguale a 3 mW .

D

VI

R

vO

Dati i seguenti circuiti, sapendo che: K n 100 A V 2 , 0,01V 1 , VT 1V , VDD = 3V, vBS=0V ,

la corrente IDS uguale a 50 μA.

Quando non è già specificato applicare il segnale di ingresso e prelevare quello di uscita in modo

che, se possibile, vengano realizzate le tre configurazioni: CS, CD, CG

Dopo aver polarizzato i dispositivi, per le varie configurazioni date ed individuate, calcolare il

guadagno di tensione, la resistenza di ingresso e quella di uscita, la massima ampiezza della

tensione di ingresso che consente la linearizzazione del MOSFET, la tensione di uscita totale e la

sensibilità del guadagno di tensione o corrente in seguito a variazioni del 10% di VTn.

VDD

VDD

VDD

RD

RD

RD

M1

M1

M1

VS

REQ

Rs

Rs

-VDD

VDD

VDD

RD

RD

vo

RG

M1

M1

vo

vi

R2

Rs

Ro

Rs

-VDD

-VDD

R1

RO

vi

VG

Rs

-VDD

-VDD

VO

_______________________________________________________________________

Disegnare un amplificatore CS con resistenza di source RS, dimensionare opportunamente RS

e RD al fine di soddisfare le seguenti specifiche:

M1 in zona di saturazione

corrente ID pari a 60A

utilizzando i seguenti dati

M1 è un MOSFET ad arricchimento a canale n con caratteristiche

K n 120 A V 2 , 0V 1 , VT 1V

VDD = 3 V.

(ricavare per prima cosa il valore di RS che consente di avere la corrente ID richiesta,

successivamente determinare il valore massimo di RD che garantisce con un margine

del 20% il funzionamento di M1 in saturazione; si trascuri il contributo di λ in

polarizzazione). Calcolare la potenza erogata dall’alimentatore (-VDD e +VDD), la

potenza dissipata sul MOSFET e sulla resistenza RD in assenza di segnale di

ingresso, cioè solo in polarizzazione.

Calcolare il guadagno di tensione vo/vi. Stimare, commentando i passaggi, il

massimo (valore assoluto) guadagno di tensione raggiungibile dalla configurazione

CS al variare di RS e di RD.

Disegnare il modello del MOSFET in condizioni di alta frequenza, cioè considerando

gli elementi capacitivi nel modello lineare. Quindi calcolare la frequenza di taglio

dell’amplificatore, sapendo che la capacità Gate-Source è 10 volte più grande della

capacità Gate-Drain (trascurare le capacità fra Drain e Body e fra Source e Body)e

supponendo in ingresso un generatore di segnali di tensione sinusoidale con resistenza

uguale a 800Ω. ( Utilizzare il metodo delle costanti di tempo).

n

a1 Ri0 Ci

i 1

n 1

a2 Ri0 Ci

i 1

n

R

j i 1

ij

C j

Dato il circuito in figura con il MOSFET a canale n ad arricchimento con kn1=kn2=120 µA/V2,

λ=0.01 V-1,VT = 1 V, VDD = 3 V, VBS=0 V, VG=1 V identificare la topologia e progettare

opportunamente kn3 ,RR e RD al fine di soddisfare le seguenti specifiche:

VDD

RD

RR

M1

Ro

VG

vo

vi

M2

M3

-VDD

corrente ID1= ID2 pari a 60 µA, VDS1 pari a 3 volte la tensione limite tra la regione

di triodo e quella di saturazione del MOSFET, potenza erogata dall’alimentatore

VDD e -VDD al ramo che contiene RD uguale a 5 volte quella al ramo contenente

RR.. Si trascuri il contributo di λ in polarizzazione.

Calcolare il guadagno di tensione ed il valore totale della tensione di uscita.

Disegnare un amplificatore CS con carico attivo, valutarne il guadagno di tensione e la

potenza richiesta dagli alimentatori. Dimensionare i Kp dei 2 MOSFET a canale p con il

vincolo che l’inserimento del ramo di riferimento pesi in termini di potenza (in

polarizzazione) meno del 10% della potenza totale del circuito. I dati sono: tensione di

alimentazione VDD = 3 V, ׀VTp =׀VTn= 1 V; kn=120 µA/V2.

Dato l’amplificatore differenziale in figura, si valuti il punto di

polarizzazione (tensioni e correnti) e si calcoli l’ampiezza del segnale

di uscita vo1 con ingresso differenziale e di modo comune sapendo che

VDD

vi1 103 3 sin w1t sin w2t

RD

RD

vo1 vo2

vi 2 10 3 sin w1t sin w2t

3

M1

M2

vi1

kn=500 µA/V2

RS=800 kΩ

RD=8 kΩ

IS=500 µA

vi2

VDD=VSS=3 V

VT=1 V

IS

Si trascuri il contributo di RS nella valutazione del punto di

polarizzazione. Realizzare il generatore di corrente reale (IS e RS) con

-VSS

uno specchio di corrente in modo tale che l’incremento di potenza

richiesta dagli alimentatori sia il 20% rispetto alla potenza richiesta in polarizzazione dal

circuito in figura.

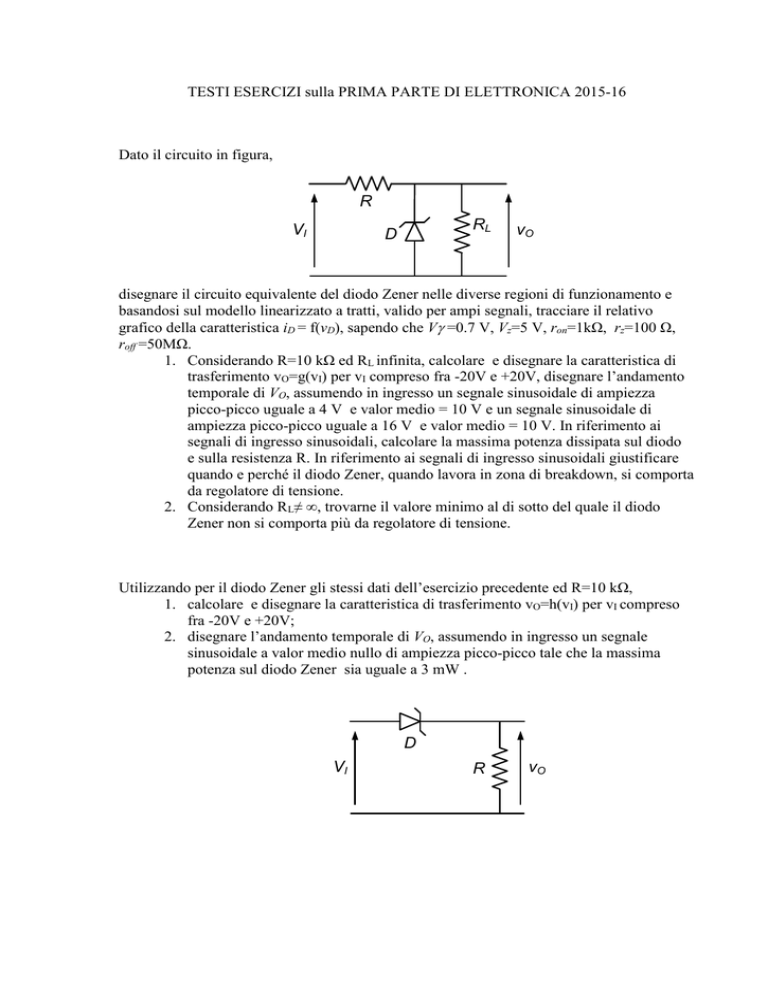

Definire e calcolare la frequenza di taglio (fH) e la frequenza di transizione (fT ) di un

amplificatore in generale e considerando il seguente modello di un amplificatore

operazionale (A.O.) ad un polo,

RO

out

A·VI

VI

CO

calcolare la relativa fH , fT .

Ro Co =0.015s

A= 105 ±25%,

Utilizzando detto A.O. , progettare un amplificatore non invertente con guadagno=30 e

progettare un amplificatore invertente con guadagno=-10. Calcolare la frequenza di taglio

degli amplificatori retroazionati. Calcolare per entrambi gli amplificatori la frequenza oltre

la quale l’errore relativo del guadagno rispetto a quello ottenuto considerando

l’amplificatore ideale , sia minore del 10%. Calcolare per entrambi gli amplificatori la

sensibilità del guadagno di tensione dell’amplificatore retroazionato rispetto alle variazioni

di A e la variazione percentuale del guadagno di tensione del sistema retroazionato.

RS

Progettare un circuito basato su amplificatori operazionali, che realizzi la seguente funzione:

Vo(t)=10V1(t) -10V2(t) ed abbia resistenza di ingresso ai morsetti in cui sono applicati V1(t)

e V2(t) uguali e maggiori di 10 MΩ.

Supponendo che l’amplificatore operazionale utilizzato sia ‘rail to rail’, sia alimentato tra

±12V ed abbia uno ‘slew rate’ di 0,8V/μs, determinare la banda a piena potenza del

circuito. Calcolare la frequenza di taglio dell’intero circuito.

Gli A.O. sono uguali e modellati come di seguito disegnato:

fH=10Hz

RO

out

A·VI

VI

CO

A= 105 ±20%,