ESERCIZIO 15

Si consideri un inverter con fan-out unitario e transistori minimi, e se ne valuti

mediante simulazione l’andamento del ritardo di propagazione (v. esercizio n.5) e

della energia dissipata (v. esercizio n. 14) al variare della tensione di

alimentazione. In particolare, si vari la tensione di alimentazione tra 1 V e 3.3 V a

passi di 0.1 V.

Successivamente, si grafichi il prodotto energia-ritardo e si stabilisca per quale

tensione di alimentazione questo sia minimo.

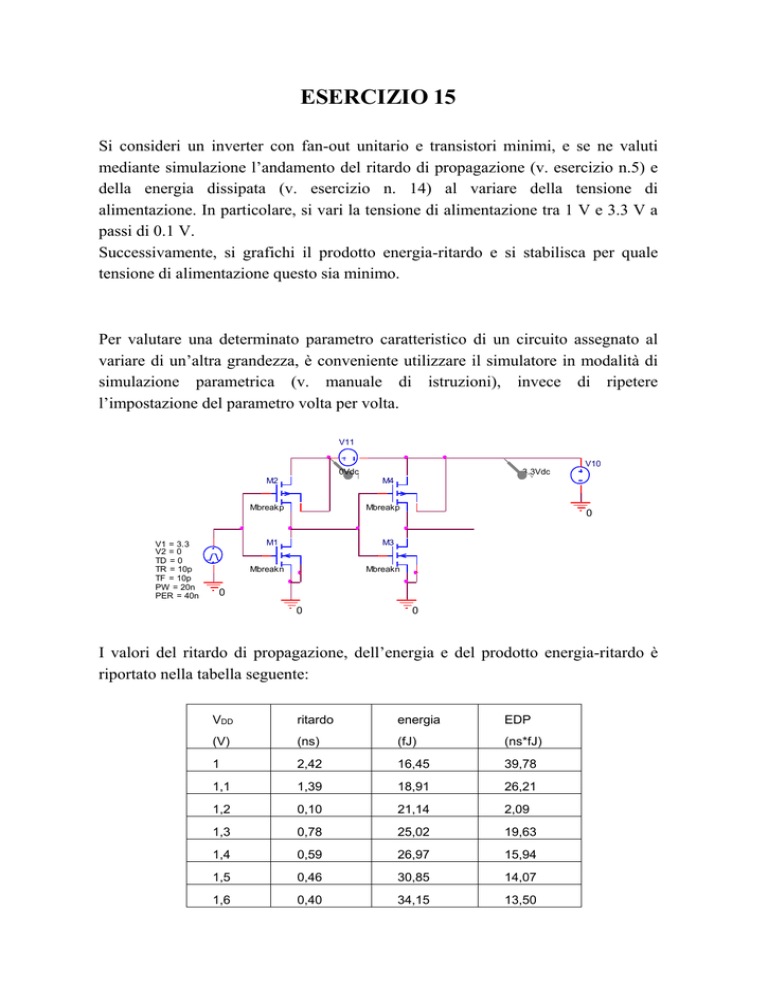

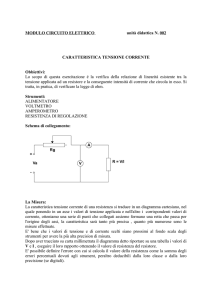

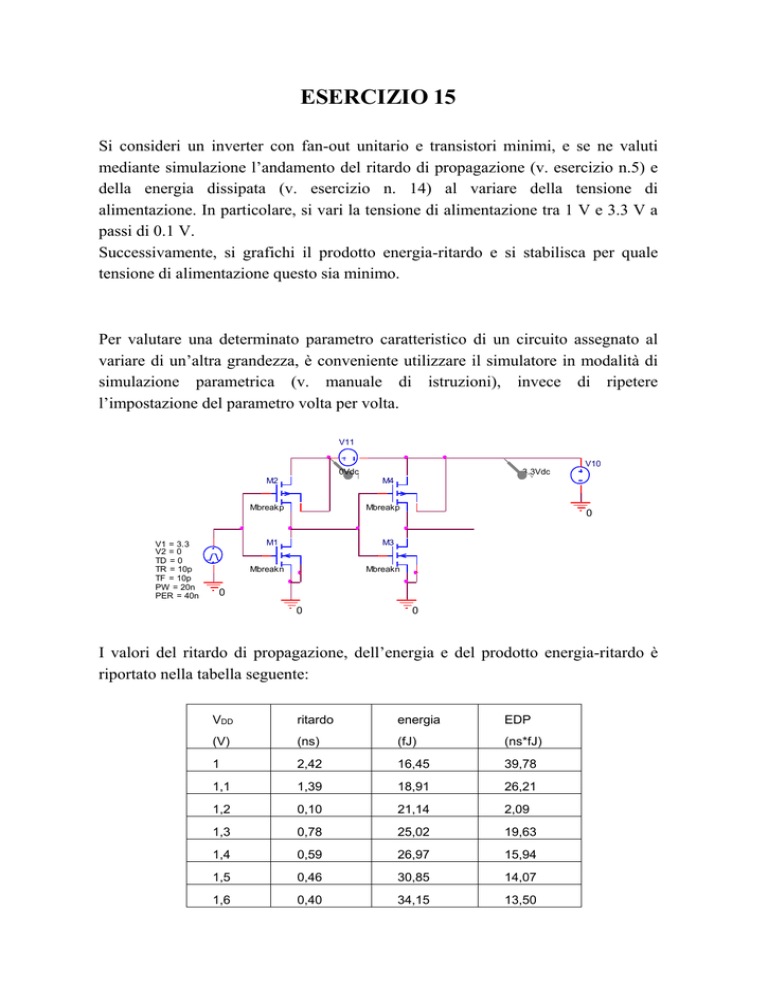

Per valutare una determinato parametro caratteristico di un circuito assegnato al

variare di un’altra grandezza, è conveniente utilizzare il simulatore in modalità di

simulazione parametrica (v. manuale di istruzioni), invece di ripetere

l’impostazione del parametro volta per volta.

V11

V10

0Vdc

I

M2

Mbreakp

V1 = 3.3

V2 = 0

TD = 0

TR = 10p

TF = 10p

PW = 20n

PER = 40n

3.3Vdc

V

M4

Mbreakp

M1

0

M3

Mbreakn

Mbreakn

0

0

0

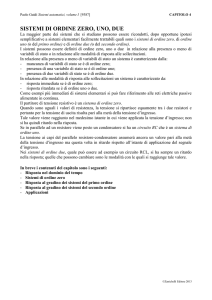

I valori del ritardo di propagazione, dell’energia e del prodotto energia-ritardo è

riportato nella tabella seguente:

VDD

ritardo

energia

EDP

(V)

(ns)

(fJ)

(ns*fJ)

1

2,42

16,45

39,78

1,1

1,39

18,91

26,21

1,2

0,10

21,14

2,09

1,3

0,78

25,02

19,63

1,4

0,59

26,97

15,94

1,5

0,46

30,85

14,07

1,6

0,40

34,15

13,50

1,7

0,031

36,48

1,27

1,8

0,03

37,62

11,56

1,9

0,27

4,26

1,14

2

0,23

4,49

1,02

2,1

0,21

5,16

1,07

2,2

0,20

5,61

1,10

2,3

0,19

5,99

1,11

2,4

0,18

6,75

1,19

2,5

0,17

0,69

1,12

2,6

0,16

7,40

1,15

2,7

0,16

7,84

1,22

2,8

0,14

0,83

1,12

2,9

0,14

8,97

1,24

3

0,13

9,62

1,29

3,1

0,13

10,14

1,34

3,2

0,12

10,78

1,13

3,3

0,12

11,52

1,39

Come atteso, il ritardo aumenta riducendo la tensione di alimentazione, in quanto la

corrente di saturazione disponibile alla carica/scarica della capacità di carico viene

ridotta. Al contempo, riducendo la tensione di alimentazione, l’energia dissipata

viene ridotta approssimativamente in maniera quadratica (essendo l’energia

proporzionale al quadrato di VDD).

Un buon compromesso tra le esigenze di bassa dissipazione ed elevata velocità è

rappresentato dal punto di minimo del prodotto energia-ritardo, che si ottiene per

VDD=2 V. Si noti che per un’assegnata frequenza di commutazione, tale condizione

minimizza anche il prodotto ritardo-consumo (che è una figura di merito più

usuale), in quanto la potenza dissipata è pari al prodotto dell’energia per la

frequenza di commutazione, nei circuiti logici CMOS.