cognome

A

B

C

D

E

F

nome

2

2

2

2

8

8

A

Totale

matricola

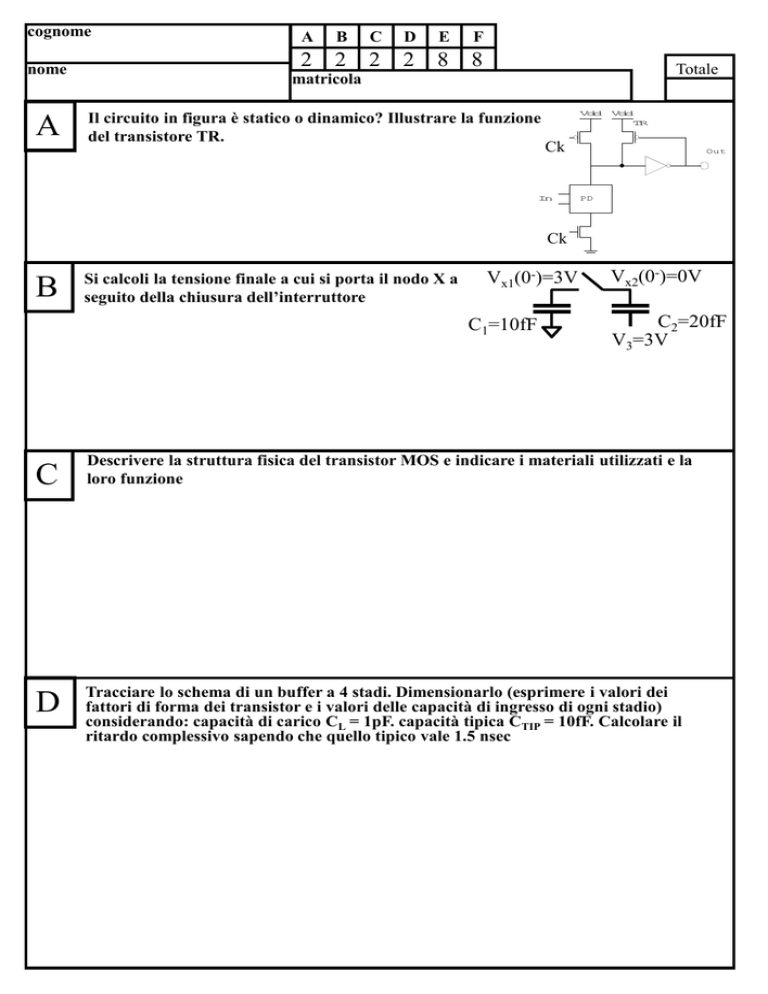

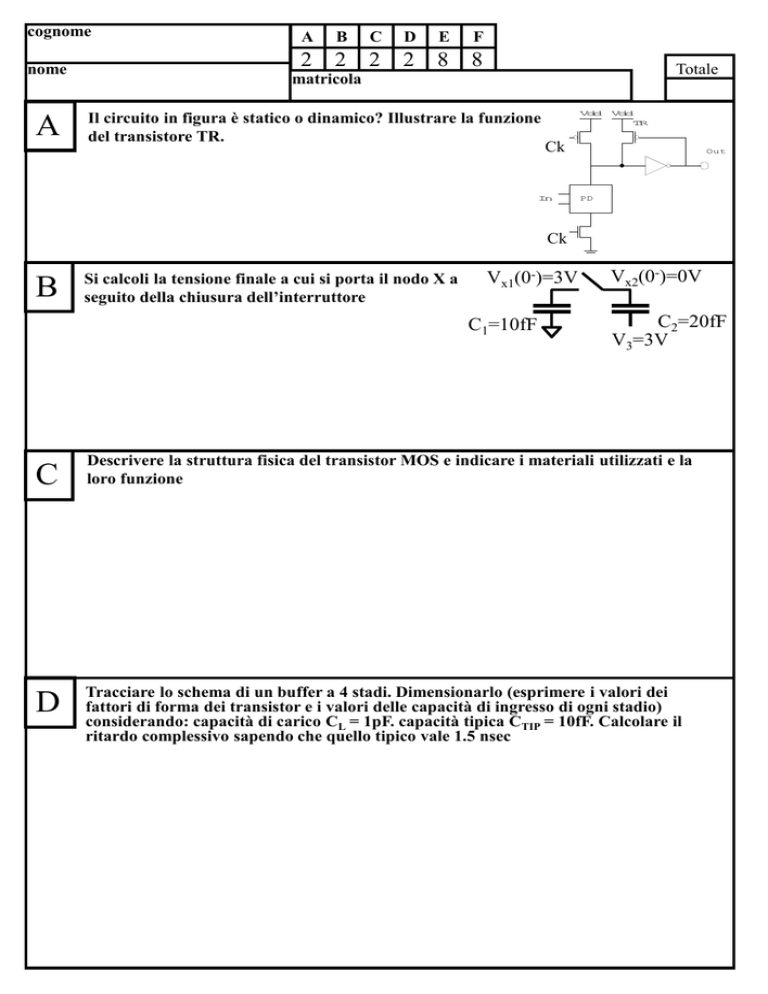

Il circuito in figura è statico o dinamico? Illustrare la funzione

del transistore TR.

Vdd

Vdd

TR

Ck

In

Out

PD

Ck

B

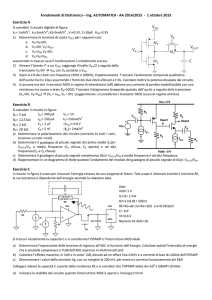

Si calcoli la tensione finale a cui si porta il nodo X a

seguito della chiusura dell’interruttore

Vx1(0-)=3V

C1=10fF

C

D

Vx2(0-)=0V

C2=20fF

V3=3V

Descrivere la struttura fisica del transistor MOS e indicare i materiali utilizzati e la

loro funzione

Tracciare lo schema di un buffer a 4 stadi. Dimensionarlo (esprimere i valori dei

fattori di forma dei transistor e i valori delle capacità di ingresso di ogni stadio)

considerando: capacità di carico CL = 1pF. capacità tipica CTIP = 10fF. Calcolare il

ritardo complessivo sapendo che quello tipico vale 1.5 nsec

E

E1 E2 E3 E4

CL = 100 fF

2

2

2

Totale

2

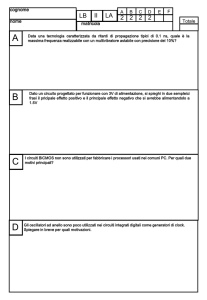

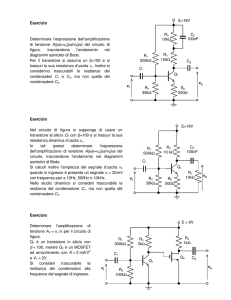

1) Si realizzi un gate FCMOS la cui funzione di uscita sia f D B A C A B C

2) Dimensionare la rete di pull-up in modo da ottenere un tempo di salita di caso peggiore di

tr=500psec (al 90%)

3) Dimensionare la rete di pull-down in modo da ottenere un tempo di discesa di caso peggiore

di tr=500psec (al 90%)

4) Calcolare l’area occupata dalla porta logica e calcolare la capacità in ingresso al nodo A

F

Vdd

A

2

P1

P4 A

Sp=3

B

P2

Sn=2

C

P3

A

F1 F2 F3 F4

S1

S2

B

1)

2)

OUT

C

S3

3)

4)

2

2

Totale

2

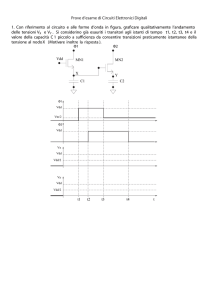

Tracciare la caratteristica statica (OUT-A) per A

che varia tra 0 V e Vdd, nell’ipotesi B=C=0.

Determinare il valore di A e di OUT nei punti di

transizione di regione di funzionamento dei

transistor e nei punti A=0 V e A = Vdd.

Determinare la soglia logica.

In assenza del transistore P4, calcolare il

dimensionamento dei transistori pMOS per

mantenere lo stesso valore di soglia logica e

valutare la soluzione migliore tra le due in

termini di area occupata.

PARAMETRI TECNOLOGICI (Vdd = 3.3 V)

VT 0

n channel

0.7 V

K'

100 μA/V 2

Cox

3.45 fF/ μm 2

Lmin

0.35 μm

λ

γ

0

0

p channel

- 0.7V

50 μA/V 2

3.45 fF/ μm 2

0.35 μm

0

0