UNIVERSITÀ DEGLI STUDI DI SIENA

Facoltà di Ingegneria

Esercitazioni di Elettronica II

Tommaso Addabbo - Valerio Vignoli

Ultima revisione: 6 dicembre 2005

c

Copyright 2005

TOMMASO ADDABBO - VALERIO VIGNOLI. Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version

1.2 or any later version published by the Free Software Foundation. A copy of the license can be retrieved from http://www.gnu.org, or contact the Free Software Foundation, Inc., 51 Franklin St, Fifth

Floor, Boston, MA 02110-1301 USA.

1

Indice

1

2

Amplificatori operazionali in circuiti con retroazione negativa

1.1 Modello dell’amplificatore operazionale reale . . . . . . . .

1.1.1 Valori tipici . . . . . . . . . . . . . . . . . . . . . .

1.2 Principali effetti delle non idealità . . . . . . . . . . . . . .

1.2.1 Amplificatore non invertente . . . . . . . . . . . . .

1.2.2 Amplificatore invertente . . . . . . . . . . . . . . .

1.3 Esercizi . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Amplificatori operazionali in circuiti a retroazione positiva

2.1 Trigger di Schmitt . . . . . . . . . . . . . . . . . . . . .

2.2 Circuiti con retroazione positiva e negativa . . . . . . . .

2.3 Circuiti astabili . . . . . . . . . . . . . . . . . . . . . .

2.3.1 Generatori di onda quadra . . . . . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

3

3

4

4

5

5

6

.

.

.

.

13

13

15

20

20

3

Convertitori A/D e D/A

22

3.1 Acquisizione dei dati . . . . . . . . . . . . . . . . . . . . . . . . 23

4

Elettronica digitale

26

4.1 Invertitori n-MOS . . . . . . . . . . . . . . . . . . . . . . . . . . 26

4.2 Invertitori C-MOS . . . . . . . . . . . . . . . . . . . . . . . . . . 28

2

Capitolo 1

Amplificatori operazionali in circuiti

con retroazione negativa

1.1

Modello dell’amplificatore operazionale reale

In questo documento si fa riferimento al modello semplificato dell’amplificatore

operazionale reale riprodotto in Fig. 1.1, dove

• VOS : tensione di offset [V ]

• IB1 , IB2 : correnti di polarizzazione [A]

• CM RR : Common Mode Rejection Ratio

• Rid : resistenza di ingresso differenziale [Ω]

• R0 : resistenza di uscita [Ω]

• Vcc , Vee : tensioni di alimentazione [V ]

Per l’operazionale si è inoltre assunto un comportamento a polo dominante per

cui

A0

A(ω) =

(1.1)

1 + j ωωB

dove ωB = 2πfB individua la pulsazione di taglio a −3dB. Ulteriori grandezze

definite sono

• GBW = A0 fB : prodotto guadagno-banda (Gain-Bandwidth) [Hz]. Coincide con la frequenza di transizione fT alla quale |A(2πfT )| ≈ 1

• SR : Slew-Rate [V/s]

• IOS = IB1 − IB2 : corrente di offset [A]

3

+

VOS

V+

V++V−

2CMRR

Vcc

IB1

Rid

A(ω)Vid

Vid

−

V−

R0

Vee

IB2

Figura 1.1: Modello semplificato dell’operazionale reale con le principali non

idealità.

1.1.1

Valori tipici

Negli amplificatori operazionali reali le quantità sopra introdotte possono variare

notevolmente. Nella tabella che segue sono riportati i valori tipici per alcuni dispositivi reali

VOS

Rid

R0

IB

IOS

A0

GBW

CM RR

SR

(Vcc − Vee )min

(Vcc − Vee )max

1.2

µA741

±1mV

1.5M Ω

75Ω

10nA

±2nA

106dB

1M Hz

90dB

0.5V /µs

8V

44V

T L081

±3mV

1012 Ω

200Ω

30pA

±5pA

106dB

3M Hz

86dB

13V /µs

8V

36V

LT C1051

±0.5µV

15pA

±30pA

130dB

2.5M Hz

130dB

4V /µs

5V

16V

Principali effetti delle non idealità

In riferimento ai valori tipici per le quantità sopra introdotte, sono riportati qui di

seguito alcuni dei principali effetti1 delle non idealità su alcuni circuiti esaminati

1

I risultati riportati sono approssimazioni ottenute attraverso opportune semplificazioni del

modello dell’operazionale reale di Fig. 1.1.

4

durante il corso. Nel seguito è posto β = R1 /(R1 + R2 ), con R1 , R2 = 102 Ω ÷

107 Ω.

1.2.1

Amplificatore non invertente

R2

Vin

Vout

R1

Zin

Zout

Figura 1.2: Amplificatore non invertente.

Posto

Vout

(ω)

Vin

(1.2)

A00

A(ω)

=

1 + βA(ω)

1 + j ωω0

(1.3)

A0 (ω) =

risulta

A0 (ω) ≈

B

dove

ωB0 = ωB (1 + βA0 )

e

A00 =

A0

1 + βA0

(1.4)

(1.5)

Inoltre

Rin (f = 0) ≈ Rid (1 + βA0 )

e

Rout (f = 0) ≈

1.2.2

R0

R0

//(R1 + R2 ) ≈

1 + βA0

1 + βA0

(1.6)

(1.7)

Amplificatore invertente

Posto

A0 (ω) =

5

Vout

(ω)

Vin

(1.8)

R2

R1

Vin

Vout

Zin

Zout

Figura 1.3: Amplificatore invertente.

risulta

A0 (ω) ≈

(β − 1)A(ω)

A00

=

1 + βA(ω)

1 + j ωω0

(1.9)

B

dove

ωB0 = ωB (1 + βA0 )

e

A00 =

(β − 1)A0

1 + βA0

Inoltre

Rin (f = 0) ≈ R1 +

e

Rout (f = 0) ≈

1.3

R2

//Rid ≈ R1

1 + A0

R0

R0

//(R1 + R2 ) ≈

1 + βA0

1 + βA0

(1.10)

(1.11)

(1.12)

(1.13)

Esercizi

Negli esercizi di questo capitolo, quando non altrimenti specificato, per gli amplificatori operazionali impiegati saranno assunte le seguenti caratteristiche R0 =

0Ω, Rid = ∞, CM RR = ∞, VOS = 0V, IB1 = IB2 = 0A, SR = ∞ e risposta in

frequenza a singolo polo (1.1).

Esercizio 1.3.1 L’amplificatore non invertente di Fig.1.2 presenta in continua

un guadagno reale di 40dB ed una resistenza di uscita di 0.1Ω. Calcolare il

guadagno in continua dell’amplificatore operazionale impiegato, assumendo che

R0 = 200Ω. Fornire un dimensionamento per R1 e R2 .

6

Soluzione. L’amplificatore non invertente in continua presenta un guadagno

A00 ≈

40

A0

= 10 20 = 100

1 + βA0

(1.14)

ed una resistenza di uscita pari a

Rout ≈

R0

= 0.1Ω

1 + βA0

(1.15)

Assumento R0 = 200Ω dalla precedente equazione si ottiene

1 + βA0 = 2000

(1.16)

Usando questo risultato nella (1.14) si ricava

A0 ≈ 2000 · 100 = 2 · 105

(1.17)

Pertanto dalla (1.16) si ottiene

β≈

2 · 103 − 1

R1

≈ 10−2 =

5

2 · 10

R1 + R2

(1.18)

da cui un possibile dimensionamento si ha ponendo R1 = 1kΩ e R2 = 99kΩ.

—————- ~ —————Esercizio 1.3.2 Si consideri per l’inseguitore di tensione di Fig. 1.4 un amplificatore operazionale con guadagno in continua di 80dB e frequenza di taglio a

−3dB di 20Hz. Calcolare l’errore commesso dall’inseguitore alla frequenza di

20kHz.

Vin

Vout

Figura 1.4: Inseguitore di tensione.

7

Soluzione. Impiegando un amplificatore operazionale ideale questo circuito ha

una funziona di trasferimento

Vout

(ω)

=1

(1.19)

Vin

ideale

L’unica non idealità da considerare è il guadagno finito e dipendente dalla frequenza (1.1). Sostituendo all’operazionale ideale il modello di Fig. 1.1 si ottiene

Vout

A(ω)

A0

(ω) =

=

Vin

1 + A(ω)

1 + A0 + j ωωB

(1.20)

80

Essendo A0 = 10 20 = 104 e ωB = 2π · 20 rad/s si ottiene

Vout

10

104

=

(2π · 20 · 103 ) ≈ 4

3

Vin

10 + j10

10 + j

(1.21)

da cui

Vout

10

3

Vin (2π · 20 · 10 ) ≈ √100 + 1 ≈ 0.995

L’errore commesso è dato dal FGE (Fractional Gain Error)

F GE|f =20kHz =

|Greale − Gideale |

= 0.005 = 0.5%

|Gideale |

(1.22)

(1.23)

—————- ~ —————Esercizio 1.3.3 Si realizzi un amplificatore di tensione con frequenza di taglio

fB0 ≥ 30kHz, e che presenti in continua Rin ≥ 1GΩ, Rout ≤ 0.5Ω e guadagno

Vout

= 400

(ω

=

0)

Vin

Per il progetto si utilizzi una cascata di uno o più stadi identici che impieghino un

amplificatore operazionale reale dalle seguenti caratteristiche

Rid = 800kΩ, R0 = 50Ω, A0 = 8 · 104 , fT = 1M Hz

Soluzione. Il progettista deve stabilire nell’ordine:

1. Il tipo di stadio da usare (amplificatore invertente o non invertente)

2. Il numero necessario di stadi

8

Al primo punto si trova facile risposta osservando che in una cascata di amplificatori invertenti o non invertenti la resistenza di ingresso e la resistenza di uscita della cascata di stadi è sostanzialmente definita dalla resistenza di ingresso del primo

stadio e dalla resistenza di uscita dell’ultimo stadio. Dalle specifiche di progetto,

l’elevata resistenza di ingresso richiesta deve indurre il progettista ad optare per

stadi amplificatori non invertenti (altrimenti, essendo in un amplificatore invertente Rin ≈ R1 si renderebbe necessario il vincolo poco realistico R1 ≥ 1GΩ).

La risposta al secondo punto è determinabile per tentativi, verificando se - partendo da un singolo stadio - è possibile soddisfare le specifiche del progetto.

Verifica per un singolo stadio

Considerando un amplificatore non invertente si ha

A00 ≈

A0

= 400

1 + βA0

(1.24)

da cui, essendo A0 = 8 · 104 , β ≈ 1/400. Impiegando l’operazionale proposto nel

singolo stadio si ottiene

Rin ≈ Rid (1 + βA0 ) = 8 · 105 (1 +

8 · 104

) ≈ 16 · 107 < 109 Ω

400

(1.25)

che non permette di soddisfare la condizione sulla resistenza di ingresso.

Verifica per una cascata di due stadi

Essendo richiesto l’utilizzo di stadi identici, il guadagno di ognuno di essi dovrà

essere tale da soddisfare

Vout

Vout

V

out

(ω = 0) =

(ω = 0) ·

(ω = 0) = 400

(1.26)

Vin

Vin

Vin

tot

1

2

da cui

√

Vout

Vout

(ω = 0) =

(ω = 0) = 400 = 20

Vin

Vin

1

2

(1.27)

Per ogni stadio quindi si ha

A00 ≈

A0

= 20

1 + βA0

(1.28)

da cui, essendo A0 = 8 · 104 , β ≈ 1/20. Impiegando l’operazionale proposto, la

resistenza di ingresso presentata dal primo stadio è

Rin ≈ Rid (1 + βA0 ) = 8 · 105 (1 +

9

8 · 104

) ≈ 3.2 · 109 > 109 Ω,

20

(1.29)

soddisfacendo la specifica sulla Rin . Per quanto riguarda la Rout presentata dal

secondo stadio (l’ultimo della cascata) si ha

Rout ≈

R0

50

−2

=

< 0.5Ω

4 ≈ 1.25 · 10

8·10

1 + βA0

1 + 20

(1.30)

soddisfacendo la specifica sulla Rout . Rimane da verificare che la frequenza di

taglio fB0 T OT dell’amplificatore determinato dalla cascata dei due stadi sia superiore a 30kHz. A tale scopo, la frequenza di taglio fB0 di ogni singolo stadio è pari

a

106

fT

(1 + βA0 ) ≈

= 50kHz

(1.31)

fB0 =

A0

20

In una cascata di N stadi identici, la frequenza di taglio a −3dB è data da

p

fBtot = fB0 21/N − 1

(1.32)

da cui, nel caso considerato per N = 2, si ha fB0 T OT ≈ 32kHz > 30kHz, che

soddisfa l’ultimo vincolo di progetto. Per completare l’esercizio, rimangono da

dimensionare R1 e R2 , per cui

R2

1

R1 = 10kΩ

=1+

= 20 ⇒

(1.33)

R2 = 190kΩ

β

R1

—————- ~ —————Esercizio 1.3.4 Nel circuito di Fig. 1.5 è impiegato un amplificatore operazionale

con guadagno ideale ma affetto da correnti di polarizzazione IB1 = IB2 = 1µA,

tensione di offset VOS = 4mV e slew rate SR = 4V /µs. Determinare il valore

di RK affinchè la componente in uscita legata alle non idealità introdotte sia

indipendente dal tempo. Assumendo in ingresso un gradino di tensione di 2V ,

determinare il valore limite della costante di tempo τ = RC compatibile con lo

slew rate dell’operazionale.

Soluzione. Sostituendo all’operazionale ideale il modello dell’operazionale reale

di Fig. 1.1 con le non idealità introdotte si ottiene il circuito di Fig. 1.6 da cui

Vx = VOS − IB RK

(1.34)

Facendo il bilancio delle correnti al nodo y si ottiene

Vin (t) − Vy (t)

= IB + IC (t)

R

dove

IC (t) = C

d

(Vy (t) − Vout (t))

dt

10

(1.35)

C

R

RK

Vin

Vout

Figura 1.5: Integratore compensato.

IB

R

IC

Vy

Vx

Vin

RK

C

opamp

ideale

Vout

VOS

IB

Figura 1.6: Modello circuitale per l’esercizio 1.3.4.

è la corrente istantanea che attraversa la capacità C. Essendo l’amplificatore operazionale nel circuito in analisi un operazionale ideale retroazionato negativamente,

vale il principio del cortocircuito virtuale ai suoi morsetti per cui Vy (t) = Vx =

costante da cui

IC (t) =

VOS − IB RK

d

Vin (t)

− IB −

= −C Vout (t)

R

R

dt

(1.36)

Affinché l’uscita non vari nel tempo a causa delle non idealità introdotte è necessario che

VOS − IB RK

IB +

=0

(1.37)

R

ovvero che RK = R + VOS /IB . In tal caso infatti si ottiene Vy = Vx = −IB R e

per l’uscita

Z t

Vin (θ)

Vout (t) = −IB R − VC (0) −

dθ

(1.38)

RC

0

11

Essendo lo slew rate dell’operazionale limitato, deve risultare

d

Vin (t) Vout (t)

=

≤ SR = 4 · 106 V /s

dt

CR

max

max

(1.39)

Assumendo in ingresso un gradino di ampiezza 2V deve essere

CR ≥

2

= 5 · 10−7 s

4 · 106

—————- ~ —————-

12

(1.40)

Capitolo 2

Amplificatori operazionali in circuiti

a retroazione positiva

Per la corretta risoluzione degli esercizi di questo capitolo, è bene ricordare che

nell’analisi dei circuiti con amplificatori operazionali con uscita in saturazione

NON è possibile applicare il principio del cortocircuito virtuale ai suoi morsetti.

Negli esercizi di questo capitolo, quando altrimenti non specificato, per gli amplificatori operazionali impegati saranno assunte le seguenti caratteristiche R0 =

0Ω, Rid = ∞, CM RR = ∞, VOS = 0V, IB1 = IB2 = 0A, SR = ∞. Inoltre,

gli amplificatori operazionali con uscita saturata sono supposti di tipo rail to rail e

con risposta V0 (Vid ) ideale riportata in Fig. 2.1.

VO

Vcc

Vid

VO

Vid

Vee

Figura 2.1: Guadagno ideale di un amplificatore operazionale con saturazione

2.1

Trigger di Schmitt

Esercizio 2.1.1 Si consideri il circuito in Fig. 2.2. Determinare l’andamento

della tensione di uscita in funzione di quella di ingresso, assumendo Vcc = 10V ,

R1 = 1kΩ e R2 = 3kΩ.

13

R2

R1

+Vcc

Vx

Vin

−Vcc

Vout

Figura 2.2: Trigger di Schmitt a logica positiva.

Soluzione. Una rapida analisi del circuito evidenzia come per Vin 6= 0 il sistema diverga (saturi) a ±Vcc (è una conseguenza della instabilità della soluzione

Vin = Vout = 0). Il circuito va analizzato verificando quali valori della tensione di ingresso siano compatibili con l’uscita in saturazione. Essendo la corrente

entrante nei morsetti dell’operazionale nulla, risulta

Vx =

(Vout − Vin )R1

+ Vin = βVout + Vin (1 − β)

R1 + R2

(2.1)

Dal momento che Vid > 0 ⇒ Vout = Vcc e che Vid < 0 ⇒ Vout = −Vcc risulta

Condizione di compatibilità per Vin affinchè Vout = Vcc

Dalla (2.1)

Vid = Vx > 0 ⇒ Vin > −

βVcc

−10/4

=

≈ −3.33V

1−β

3/4

(2.2)

Condizione di compatibilità per Vin affinchè Vout = −Vcc

Dalla (2.1)

Vid = Vx < 0 ⇒ Vin < +

βVcc

+10/4

=

≈ 3.33V

1−β

3/4

(2.3)

Assumendo di far variare in modo monotono crescente l’ingresso da −10V a

+10V si ottiene pertanto il grafico (a) riportato in Fig. 2.3. Viceversa, assumendo

di far variare in modo monotono decrescente l’ingresso da +10V a −10V si ottiene il grafico (b). Se ne evince che il circuito è affetto dalla isteresi riportata nel

grafico (c).

—————- ~ —————14

Vout

+Vcc

(a)

+10V

−10V

+3.33V

Vin

−Vcc

+Vcc

(b)

Vout

+10V

−3.33V

−10V

Vin

−Vcc

Vout

+Vcc

(c)

+10V

−3.33V

−10V

+3.33V

Vin

−Vcc

Figura 2.3: Isteresi del trigger di Schmitt a logica positiva dell’Es. 2.1.1.

2.2

Circuiti con retroazione positiva e negativa

Esercizio 2.2.1 Si consideri il circuito in Fig. 2.4 in cui R1 = R2 = R3 = R4 =

1kΩ, RL = 500Ω e Vcc = 15V . Determinare l’insieme dei valori di VK per cui il

circuito ammette soluzione e calcolare la corrente che scorre su RL .

Soluzione. Nel circuito è presente una retroazione positiva ed una negativa. L’insieme dei valori VK per cui il circuito ammette soluzione è determinato dai punti

fissi del sistema, ovvero da quei valori delle tensioni ai nodi e delle correnti nei

rami per cui sono congiuntamente soddisfatte tutte le leggi che regolano il circuito

(equazioni di Kirchoff per le correnti ai nodi, ecc...). Al fine di poter individuare

i punti fissi del sistema in questo tipo di circuiti si rende in generale necessario

15

R2

R1

+Vcc

Vy

−Vcc

Vx

R3

R4

2V

VK

RL

Figura 2.4: Circuito dell’Es. 2.2.1.

porre volta per volta l’amplificatore operazionale in uno dei suoi possibili stati

ideali (vedi Fig. 2.1):

1. uscita satura a +Vcc (Vid > 0)

2. uscita satura a −Vcc (Vid < 0)

3. uscita non satura ad un qualunque valore di tensione compreso fra Vcc e Vee ,

con Vid = 0

ed esaminare l’esistenza di soluzioni per il circuito.

1) Ipotesi di uscita dell’operazionale satura a +Vcc (Vid > 0)

In questa ipotesi deve essere Vx > Vy e VK = Vcc . Risulta

Vcc

Vcc R1

=

= 7.5V

R1 + R2

2

(2.4)

Vcc · R4 //RL

2 · R3 //RL

17

+

=

= 4.25V

R3 + R4 //RL R4 + R3 //RL

4

(2.5)

Vy =

Tuttavia

Vx =

Ma allora abbiamo ottenuto Vx < Vy ⇒ Vid < 0 che è un assurdo poichè contraddice l’ipotesi. Ne consegue che per VK = +Vcc il circuito non ammette soluzione.

2) Ipotesi di uscita dell’operazionale satura a −Vcc (Vid < 0)

In questa ipotesi deve essere Vx < Vy e VK = −Vcc . Risulta

Vy =

−Vcc R1

−Vcc

=

= −7.5V

R1 + R2

2

16

(2.6)

Tuttavia

Vx =

2 · R3 //RL

−13

−Vcc · R4 //RL

+

=

= −3.25V

R3 + R4 //RL

R4 + R3 //RL

4

(2.7)

Si ottiene quindi Vx > Vy ⇒ Vid > 0 che è un assurdo poichè contraddice l’ipotesi. Anche in questo caso per VK = −Vcc il circuito non ammette soluzione. Non

rimane che verificare la

3) Ipotesi di uscita dell’operazionale non satura ad un qualunque valore di tensione compreso fra +Vcc e −Vcc , con Vid = 0

In questo caso deve essere Vx = Vy , con

Vy =

VK · R1

VK

=

R1 + R2

2

(2.8)

Impostando il bilancio delle correnti al nodo x si ottiene

VK − VK /2 2 − VK /2

VK

+

=

R3

R4

2RL

(2.9)

da cui

VK

VK

+2−

= VK ⇒ VK = 2V

(2.10)

2

2

Ne consegue che l’unico valore ammissibile per VK è 2V , ed in tale condizione la

corrente che scorre sul resistore RL è pari a IL = 1/500 = 2mA.

Commento ai risultati

La soluzione individuata è una soluzione stabile, la cui stabilità è indotta dalla

prevalenza della retroazione negativa su quella negativa. Eseguendo una analisi

alle variazioni del circuito ad anello aperto1 nell’intorno del punto VK = 2V , una

variazione infinitesima dVK della tensione VK comporta una variazione dVy =

dVK R1

K RL //R4

= dVK /2 sul morsetto invertente ed una variazione dVx = dV

=

R1 +R2

RL //R4 +R3

dVK /4 sul morsetto non invertente, da cui sull’uscita dell’operazionale è indotta

una variazione

dVo = A dVid = A (dVx − dVy ) = −A

dVK

4

(2.11)

col predominio della retroazione negativa su quella positiva. In tale condizione,

a seguito di una perturbazione, il sistema tende naturalmente a ristabilizzarsi sul

suo unico punto di equilibrio caratterizzato da VK = 2V .

—————- ~ —————1

Ovvero staccando l’uscita dell’amplificatore operazionale dal nodo VK

17

Esercizio 2.2.2 Si consideri il circuito in Fig. 2.5, in cui Vcc = 10V , R1 =

1kΩ,R2 = 10kΩ,R3 = 9kΩ e si assuma per il diodo D il modello ideale2 con

caduta di tensione VON = 0.5V . Determinare l’insieme dei valori di Vout per cui

il circuito ammette soluzione.

R2

R3

Vx

D

R1

+Vcc

Vy

−Vcc

Vout

Figura 2.5: Circuito dell’Es. 2.2.2.

Soluzione. Analogamente a quanto visto nell’Es. 2.2.1, nel circuito di Fig. 2.5

sono presenti una retroazione positiva ed una negativa. Anche in questo caso,

al fine di poter individuare i punti fissi del sistema saranno cercate soluzioni che

siano compatibili con l’amplificatore operazionale posto volta per volta in uno dei

suoi possibili stati ideali (vedi Fig. 2.1):

1. uscita satura a +Vcc (Vid > 0)

2. uscita satura a −Vcc (Vid < 0)

3. uscita non satura ad un qualunque valore di tensione compreso fra Vcc e Vee ,

con Vid = 0

1) Ipotesi di uscita dell’operazionale satura a +Vcc (Vid > 0)

Il diodo in tale condizione è in conduzione, per cui - in riferimento al modello

ideale del diodo - qualunque sia la corrente sul resistore R3 si ha Vx = 0.5V . La

tensione Vy invece è data semplicemente dal partitore

Vy =

10

Vcc · R1

=

≈ 0.91V

R1 + R2

11

2

(2.12)

Applicando tale modello al diodo D nel circuito di Fig. 2.5, la corrente ID verso massa che

scorre nel diodo è nulla per Vx < VON e qualunque (positiva) per Vx = VON .

18

Ma allora abbiamo ottenuto Vx < Vy ⇒ Vid < 0 che è un assurdo poichè contraddice l’ipotesi. Ne consegue che per Vout = +Vcc il circuito non ammette

soluzione.

2) Ipotesi di uscita dell’operazionale satura a −Vcc (Vid < 0)

In tal caso il diodo è interdetto e sul resistore R3 non scorre corrente. Ne consegue

che Vx = Vout = −Vcc = −10V . Vy invece è data dal partitore

Vy =

−Vcc · R1

10

= − ≈ −0.91V

R1 + R2

11

(2.13)

Abbiamo trovato in questo caso Vy > Vx ⇒ Vid < 0. Ne consegue che per

Vout = −Vcc il circuito ammette soluzione. Per concludere è necessario analizzare se esistano altre soluzioni compatibili con la

3) Ipotesi di uscita dell’operazionale non satura ad un qualunque valore di tensione compreso fra +Vcc e −Vcc , con Vid = 0

In questo caso deve essere necessariamente Vx = Vy . Se il diodo è interdetto

(Vout < VON ) abbiamo che Vx = Vout , e

Vy =

Vout · R1

Vout

=

R1 + R2

11

(2.14)

da cui Vx = Vy se e solo se Vout = 0. Se il diodo è in conduzione (Vout ≥ VON ),

si ha che Vx = 0.5V e che l’unico valore di Vout per cui Vy = 0.5 dalla (2.14) è

Vout = 5.5V .

Ricapitolando risulta che il circuito ammette soluzione per i valori di

Vout ∈ {−10V, 0V, 5.5V }.

Commento ai risultati

I tre valori sopra individuati sono soluzioni formali del problema, ma solo i valori

Vout = −10V e Vout = +5.5V rappresentano soluzioni stabili del circuito, mentre

la soluzione Vout = 0V è instabile. Questo è dimostabile operando come nell’Es.

2.2.1. Si consideri ad esempio la soluzione Vout = 0 e si analizzi alle variazioni

il circuito ad anello aperto3 nell’intorno di questo punto. Ne consegue che nell’intorno di Vout = 0 il diodo è un circuito aperto e che una variazione dVout al

nodo Vout comporta una variazione dVx = dVout al nodo Vx , mentre la stessa vari1

azione dVout comporta una variazione dVy = dVout R1R+R

= dV11out al nodo Vy . Ne

2

consegue che sull’uscita dell’operazionale è

dVo = AdVid = A(dVx − dVy ) = A(dVout −

3

dVout

10

) = A dVout

11

11

Ovvero staccando l’uscita dell’amplificatore operazionale dal nodo Vout

19

(2.15)

col predominio della retroazione positiva su quella negativa. In tale condizione,

a seguito di una perturbazione, il sistema tende a divergere dal punto considerato

Vout = 0V . E’ lasciato per esercizio effettuare lo stesso tipo di analisi per le

due soluzioni stabili Vout = −10V e Vout = +5.5V (Per il punto Vout = −10V

sono di interesse solo le perturbazioni positive, giacché l’uscita non può divergere

negativamente oltre i −10V ).

—————- ~ —————-

2.3

2.3.1

Circuiti astabili

Generatori di onda quadra

Esercizio 2.3.1 Si consideri il generatore di onda quadra in Fig. 2.6 con RU =

2kΩ, RD = 3kΩ, RA = 2kΩ, R = 1kΩ, C = 1µF , Vcc = 10V . Calcolare il

periodo ed il duty cycle del segnale generato.

RA

RU

+Vcc

+Vcc

Vx

−Vcc

RD

−Vcc

Vout

VC

R

C

Figura 2.6: Generatore di onda quadra.

Soluzione. L’uscita dell’operazionale rimane satura a +Vcc fintanto che Vx > VC .

Ponendo quindi Vout = Vcc si trova che

VxU =

(Vcc − (−Vcc )) · RD

− Vcc = 5V

RD + RU //RA

(2.16)

Analogamente, l’uscita dell’operazionale rimane satura a −Vcc fintanto che Vx <

VC . Ponendo Vout = −Vcc si trova che

VxD =

(Vcc − (−Vcc )) · RD //RA

− Vcc = −2.5V

RU + RD //RA

20

(2.17)

I valori della tensione VC che determinano la commutazione del circuito sono

pertanto 5V e 2.5V . Fissato in t = 0 l’istante della commutazione dell’uscita

dell’operazionale si ha che

VC (t) = (Vout − VC (0))(1 − e−t/RC ) + VC (0)

(2.18)

Assumendo Vout commutato su Vcc = 10V e VC (0) = −2.5V si ha che il periodo

di tempo ∆tU per cui l’uscita è alta è il tempo per cui è verificata l’equazione

VCU (∆tU ) = (10 − (−2.5))(1 − e−∆tU /RC ) − 2.5 = 5V = VxU

(2.19)

da cui

∆tU = −RC ln 0.4 ≈ 0.916 ms

(2.20)

analogamente, assumendo Vout commutato su −Vcc = −10V e VC (0) = 5V si ha

che il periodo di tempo ∆tD per cui l’uscita è bassa è il tempo per cui è verificata

l’equazione

VCD (∆tD ) = (−10 − 5)(1 − e−∆tD /RC ) + 5 = −2.5V = VxD

(2.21)

da cui

∆tD = −RC ln 0.5 ≈ 0.693 ms

(2.22)

Ne consegue che il periodo del segnale generato è T = ∆tU + ∆tD = 1.609 ms,

mentre il duty cycle è

∆tU

duty cycle =

≈ 57%

(2.23)

T

—————- ~ —————-

21

Capitolo 3

Convertitori A/D e D/A

Negli esercizi di questo capitolo, quando non altrimenti specificato, per gli amplificatori operazionali impiegati saranno assunte le seguenti caratteristiche R0 =

0Ω, Rid = ∞, CM RR = ∞, VOS = 0V, IB1 = IB2 = 0A, SR = ∞ e risposta

in frequenza a singolo polo (1.1). In riferimento alle nozioni introdotte durante il

corso, sarà utilizzata la seguente notazione:

• SN R : rapporto segnale rumore

• n : numero dei bit del convertitore

• fc =

1

Tc

: frequenza di campionamento [Hz]

• tconv : tempo di conversione del convertitore A/D [s]

• tacq : tempo di acquisizione del Sample and Hold (S&H)[s]

• tset : tempo di settling del S&H [s]

• ∆tj jitter del ritardo di apertura del S&H [s]

• Droop : velocità di scarica della capacità di campionamento in fase di hold

[V /s]

• VF S : tensione di fondo scala del convertitore A/D [V ]

• VLSB =

VF S

2n

: risoluzione del converitore A/D [V ]

22

A/D

converter

C

DIGITAL SIGNALS

Vin

Figura 3.1: Stadio di acquisizione Sample and Hold

3.1

Acquisizione dei dati

Esercizio 3.1.1 Nello stadio Sample and Hold di Fig. 3.1 i due amplificatori

operazionali sono caratterizzati da correnti di polarizzazione Ib1 = Ib2 = 0.1µA,

e presentano una resistenza di ingresso di 10M Ω. Assumendo

• Vin (t) ≥ 0;

• banda di Vin (t) = 5kHz;

• C = 1nF

• convertitore A/D a 6 bit;

• dinamica del convertitore sempre adattata alla dinamica del segnale di

ingresso.

Si determini

1. il valore limite per la somma dei tempi di settling e di acquisizione

2. il minimo valore della dinamica di Vin

se il tempo di conversione del convertitore A/D rappresenta il 75% del tempo

totale disponibile per l’acquisizione e conversione di un singolo campione alla

frequenza di Shannon, ed se la la massima variazione di tensione sulla capacità

di tenuta durante il tempo di conversione deve essere inferiore ad 1VLSB .

Soluzione. Assumendo che il segnale di ingresso sia a banda limitata di 5kHz esso deve essere acquisito almeno ad una frequenza di campionamento fc ≥ 10kHz.

Assumendo Tc = 1/fc = 10−4 s deve risultare

tacq + tset + tconv ≤ Tc

23

Vin

A/D

converter

C

Ib

R

DIGITAL SIGNALS

A

B

Figura 3.2: Modello usato nell’Es.3.1.1

R

A

−Ib R

C

B

Figura 3.3: Scarica della capacità sul modello equivalente di Thevenin del bipolo

A-B a valle (Es. 3.1.1)

da cui, imponendo che il tempo di conversione dell’A/D sia pari al 75% del tempo

totale necessario all’acquisizione e conversione del dato deve essere

tacq + tset ≤

Tc

= 0.25 · 10−4 s

4

a cui corrisponde

3Tc

= 0.75 · 10−4 s

(3.1)

4

Adesso è necessario valutare il droop legato alle perdite del circuito. In particolare le non idealità introdotte determinano il modello di Fig. 3.2. L’andamento

temporale della tensione sulla capacità segue un andamento esponenziale la cui

espressione è di immediata determinazione una volta esplicitato l’equivalente di

Thevenin del circuito a valle della sezione A-B in Fig. 3.3. Durante la fase di

hold la tensione ai capi della capacità segue la legge

t

VC (t) = VC (0) − (Ib R + VC (0)) 1 − e− RC

tconv = 3(tacq + tset ) ≤

che per valori di t << RC = 10−2 s può essere approssimata1 considerando il

troncamento ai termini di primo grado della serie di Taylor di

t

t

+ o(t2 )

(1 − e− RC ) =

RC

1

Condizione ampiamente soddisfatta, considerando la (3.1)

24

ottenendo

(Ib R + VC (0)) t

RC

Il valore della capacità in t = 0 (inizio della fase di hold) è pari a Vin , per cui si

richiede che alla fine della conversione la variazione della tensione ai capi della

capacità non sia superiore a VLSB = V2FnS ovvero, essendo il convertitore a n = 6

bit

VF S

(Ib R + Vin ) tconv

< 6

(3.2)

RC

2

La (3.2) pone la condizione più stringente quando Vin = VF S , da cui si ottiene

VC (t) ≈ VC (0) −

(1 + VF S )tconv <

ovvero

VF S >

VF S

100 · 26

6400tconv

1 − 6400tconv

Assumendo tconv = 0.75 · 10−4 (il massimo ammissibile per tconv ) si ottiene

VF S > 0.93V .

—————- ~ —————-

25

Capitolo 4

Elettronica digitale

4.1

Invertitori n-MOS

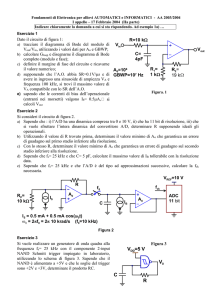

Esercizio 4.1.1 Si consideri l’invertitore di Fig. 4.1. Trascurando l’effetto body e

la modulazione di canale, calcolare VOL , VOH e la potenza statica media dissipata assumendo per i due transistor Vdd = 5V, Kn1 = 100µA/V 2 , Kn2 =

400µA/V 2 , VT n = 1V .

Vdd

D

M1

G

S

D

Vin

G

M2

Vout

S

Figura 4.1: Inverter n-MOS con carico attivo connesso a diodo.

Soluzione. Il transistor M1 è connesso a diodo, ovvero su di esso scorre una

corrente nulla per Vdd − Vout < VT n , mentre per Vdd − Vout ≥ VT n , risultando

sempre verificata la condizione di saturazione, scorre una corrente circa1 pari a

Kn1 (Vdd − Vout − VT n )2 . La tensione di uscita VOL è ottenuta assumendo in ingresso la tensione VOH e viceversa.

1

Ovvero trascurando la modulazione di canale e l’effetto substrato.

26

I [mA]

3.5

I2 @ Vin = VOH

3

2.5

2

1.5

I1

1

0.5

0

0

0.5

1

1.5

2

2.5

VOL

3

3.5

4

4.5

5

Vout [V]

Figura 4.2: Individuazione grafica del punto Vout = VOL per il circuito di Fig. 4.1.

Calcolo di VOH .

Per un corretto funzionamento di questo tipo di strutture circuitali è necessario

che la tensione VOL posta in ingresso sia tale da interdire il transistor pilotato M2

(ovvero VOL < VT n ). Assumendo per ipotesi tale condizione verificata, in seguito

ad una transizione alto-basso del segnale di ingresso, la capacità connessa al nodo

di uscita Vout viene caricata attraverso M1 alla tensione Vdd − VT n , valore oltre il

quale si ha l’interdizione di M1 . Pertanto se ne evince che per questo invertitore

VOH = Vdd − VT n = 4V .2

Calcolo di VOL .

Posto Vin = VOH è ragionevole assumere che il transistor M2 si trovi in regione

di triodo. Tale supposizione è giustificata osservando la Fig. 4.2, ed avendo ipotizzato VOL < VT n . Il valore dell’uscita Vout = VOL è determinato imponendo

l’uguaglianza fra le correnti che scorrono nei due transistor:

2

Kn2 [2(VGS2 − VT n )VDS2 − VDS2

] = Kn1 (VGS1 − VT n )2

(4.1)

da cui, assumendo VGS2 = Vin = VOH = 4V

VOL

2

Kn2 [2(VOH − VT n )VOL − VOL

] = Kn1 (Vdd − VOL − VT n )2

√

32 ± 322 − 20 · 16

0.55V

≈

≈

5.8V ( soluzione impossibile)

10

2

(4.2)

(4.3)

Tenendo conto dell’effetto body, sarebbe corretto scrivere VOH = Vdd − VT n1 (VOH ), poichè

se Vout > 0 per il transistor M1 risulta VSB > 0.

27

Verifica dei risultati.

Per la convalida dei risultati ottenuti è necessario verificare le ipotesi fatte:

• VOL ≈ 0.55V ⇒ (VOL < VT n ) è verificata;

• VOL ≈ 0.55V ⇒ (VOL < VOH − VT n ), ovvero il transistor M 2 è effettivamente in regione di triodo.

Calcolo della potenza statica media dissipata.

L’invertitore dissipa potenza statica solo nello stato Vout = VOL , poichè nello

stato Vout = VOH il transistor M 2 è in condizione di interdizione. Assumendo i

due stati dell’inverter equiprobabili risulta

PDstat (VOL )

PDstat (VOL ) + PDstat (VOH )

=

=

2

2

Vdd · I1 (VOL )

Vdd Kn1 (Vdd − VOL − VT n )2

=

=

≈

2

2

≈ 2.95mW

PDstat =

(4.4)

(4.5)

(4.6)

—————- ~ —————-

4.2

Invertitori C-MOS

Esercizio 4.2.1 Si consideri l’invertitore di Fig. 4.3 dove i due transistor sono

caratterizzati da VT n = |VT p | = 1V . Assumendo Vdd = 1.5V determinare

l’andamento della tensione di uscita in funzione di quella di ingresso.

Soluzione. Analizziamo il comportamento del circuito variando in modo crescente la tensione di ingresso da 0V a Vdd = 1.5V . Il transistor M1 è in conduzione

se Vin > VT n = 1V , mentre il transistor M2 è in conduzione se Vin < Vdd − VTn =

0.5V . Ne consegue che per 0 ≤ Vin < 0.5V il transistor M2 è interdetto, mentre

M1 è in conduzione, mantenendo l’uscita a Vdd = 1.5V . Per 0.5 ≤ Vin ≤ 1V entrambi i transistor sono interdetti. In questa situazione la capacità CL si mantiene

carica alla tensione Vout = 1.5V . Per 1 < Vin ≤ 1.5V il transistor M2 passa

alla conduzione, portando l’uscita a Vout = 0V . L’analisi si completa facendo

variare in modo decrescente la tensione di ingresso da 1.5V a 0V , ottenendo in

conclusione il ciclo di isteresi riportato in Fig. 4.4

—————- ~ —————Esercizio 4.2.2 Si consideri la cascata di due invertitori identici di Fig. 4.5.

Assumendo i transistor caratterizzati da VT n = |VT p |, Wn = Ln = Lp , µn =

2.5µp , Kn = Kp

28

Vdd

M1

Vin

Vout

M2

CL

Figura 4.3: Inverter CMOS con carico capacitivo CL .

Vout

1.5V

0V

0.5V

1.0V

1.5V

Vin

Figura 4.4: Isteresi del circuito di Fig. 4.3 con Vdd = 1.5V, VT n = −VT p = 1V .

1. fornire una stima approssimata del carico capacitivo del primo inverter;

2. calcolare il tempo di propagazione del primo inverter, assumendo in ingresso un segnale ideale a transizioni istantanee.

3. Risolvere i punti 1) e 2) assumendo VT n = |VT p |, Wp = Wn = Ln =

Lp , µn = 2.5µp .

Soluzione. Il primo inverter presenta un carico capacitivo dato della capacità di

ingresso del secondo inverter.

Soluzione ai punti 1) e 2).

29

Vdd

Vin

M1

M3

M2

M4

Vout

Figura 4.5: Cascata di due invertitori CMOS.

In prima approssimazione la capacità risultante corrisponde alla somma

CL ≈ Cox (Wn Ln + Wp Lp ) = 3.5 Cox Wn Ln

Il risultato è calcolato tenendo conto che essendo Ln = Lp e µn = 2.5µp risulta

(Kn = Kp ) ⇒ (Wp = 2.5Wn ). Il tempo di propagazione è dato da

tP =

tP HL + tP LH

2

Il tempo tP HL corriponde a quello necessario alla tensione di uscita per passare da

VOH a metà dello swing logico. In questo caso la capacità è scaricata attraverso

l’nMOS, da cui

VOH −VOL

CL

Vdd 3.5 Wn Ln Cox

2

(4.7)

=

tP HL ≈

|Isat |n

2Kn (Vdd − VT n )2

Analogamente si calcola il tempo tP LH

VOH −VOL

CL

Vdd 3.5 Wn Ln Cox

2

tP LH ≈

=

|Isat |p

2Kp (Vdd − VT p )2

(4.8)

Con riferimento ai dati del problema si trova

tP ≈

Vdd 3.5 Wn Ln Cox

2Kn (Vdd − VT n )2

Soluzione al punto 3).

30

(4.9)

Con i nuovi dati risulta che in prima approssimazione la capacità CL corrisponde

alla somma

CL ≈ Cox (Wn Ln + Wp Lp ) = 2 Cox Wn Ln

Analogamente al caso precedente le (4.7)-(4.8) risultano

VOH −VOL

CL

Vdd Wn Ln Cox

2

=

tP HL ≈

|Isat |n

Kn (Vdd − VT n )2

VOH −VOL

CL

Vdd Wn Ln Cox

2

=

tP LH ≈

|Isat |p

Kp (Vdd − VT p )2

Essendo Wp = Wn = Ln = Lp e µn = 2.5µp risulta Kn = 2.5 Kp da cui

1

2.5

Vdd 3.5 Wn Ln Cox

Vdd Wn Ln Cox

+

=

tP ≈

2(Vdd − VT )2 Kn Kn

2Kn (Vdd − VT n )2

(4.10)

(4.11)

(4.12)

Commento ai risultati.

Osservando le espressioni trovate si evidenzia come i tempi di propagazione di un

inverter CMOS simmetrico (VT n = |VT p | e Kn = Kp ) con l’nMos realizzato ad

area minima ha lo stesso tempo di propagazione di un inverter CMOS realizzato

con entrambi i transistor ad area minima (con conseguente non simmetria legata a

Kn 6= Kp ). In quest’ultimo caso tuttavia risulta che il tP LH è oltre due volte più

grande del tP HL .

—————- ~ —————Esercizio 4.2.3 Quando il segnale di ingresso è un’onda quadra reale a valori

0V − 10V l’inverter CMOS simmetrico di Fig. 4.3 con Vdd = 10V e carico CL =

50pF assorbe mediamente una corrente di alimentazione pari a 0.8uA/kHz. Stimare qual’è la componente di questa corrente che deriva dalla carica e scarica del carico capacitivo. Dire a quali cause è dovuta la parte rimanente della

corrente media assorbita.

Soluzione. Nell’ipotesi che le costanti di tempo del circuito (RON CL ) siano

almeno 4-5 volte più piccole del periodo del segnale di ingresso, durante ogni

periodo per la carica e scarica della capacità CL viene dissipata una energia circa

2

pari a CL Vdd

. Essendo l’inverter alimentato costantemente a Vdd , ne consegue

che la corrente mediamente assorbita è pari a CL f Vdd , dove f è la frequenza del

segnale di ingresso. Normalizzando rispetto alla frequenza di lavoro si ottiene una

corrente mediamente assorbita pari a CL Vdd = 50 · 10−12 · 10 = 0.5uA/kHz. La

parte rimanente della corrente mediamente assorbita è dovuta alla corrente che

attraversa la serie dei due transistor M1 ed M2 durante le transizioni del segnale

di ingresso.

31