ELETTRONICA DEI SISTEMI DIGITALI

Prova scritta del 09/10/13

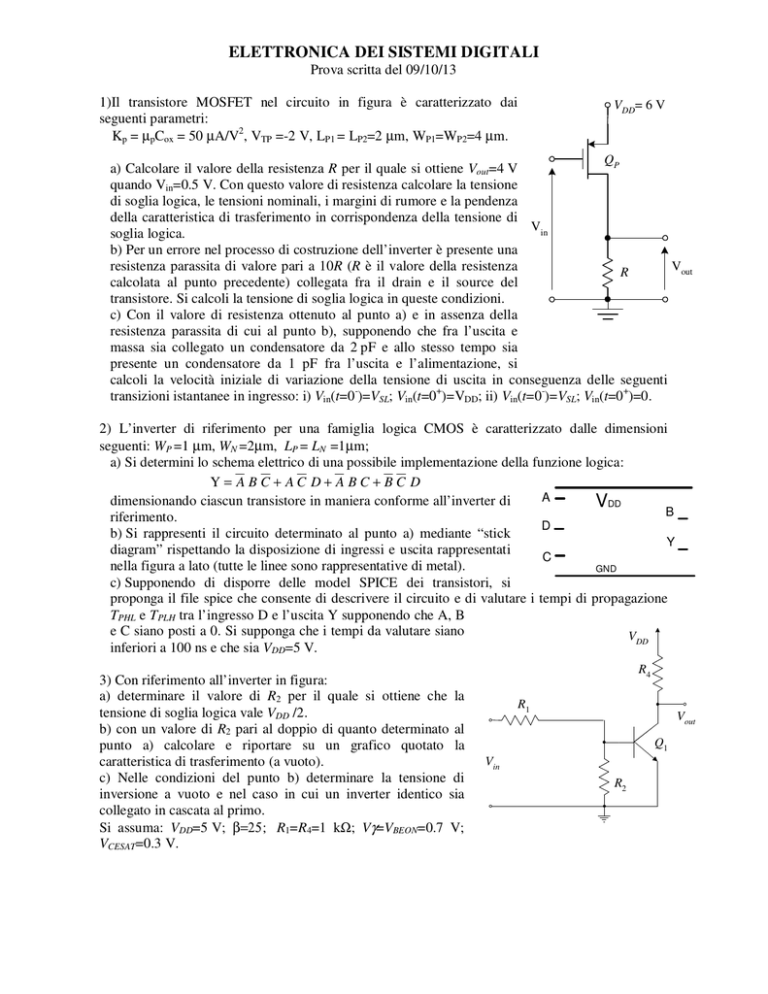

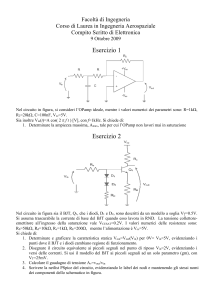

1)Il transistore MOSFET nel circuito in figura è caratterizzato dai

seguenti parametri:

Kp = µpCox = 50 µA/V2, VTP =-2 V, LP1 = LP2=2 µm, WP1=WP2=4 µm.

VDD= 6 V

Q

P

a) Calcolare il valore della resistenza R per il quale si ottiene Vout=4 V

quando Vin=0.5 V. Con questo valore di resistenza calcolare la tensione

di soglia logica, le tensioni nominali, i margini di rumore e la pendenza

della caratteristica di trasferimento in corrispondenza della tensione di

Vin

soglia logica.

b) Per un errore nel processo di costruzione dell’inverter è presente una

Vout

resistenza parassita di valore pari a 10R (R è il valore della resistenza

R

calcolata al punto precedente) collegata fra il drain e il source del

transistore. Si calcoli la tensione di soglia logica in queste condizioni.

c) Con il valore di resistenza ottenuto al punto a) e in assenza della

resistenza parassita di cui al punto b), supponendo che fra l’uscita e

massa sia collegato un condensatore da 2 pF e allo stesso tempo sia

presente un condensatore da 1 pF fra l’uscita e l’alimentazione, si

calcoli la velocità iniziale di variazione della tensione di uscita in conseguenza delle seguenti

transizioni istantanee in ingresso: i) Vin(t=0 -)=VSL; Vin(t=0+)=VDD; ii) Vin(t=0-)=VSL; Vin(t=0 +)=0.

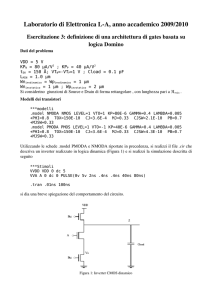

2) L’inverter di riferimento per una famiglia logica CMOS è caratterizzato dalle dimensioni

seguenti: WP =1 µm, WN =2µm, LP = LN =1µm;

a) Si determini lo schema elettrico di una possibile implementazione della funzione logica:

Y = A B C + AC D+ A BC + BC D

A

dimensionando ciascun transistore in maniera conforme all’inverter di

VDD

B

riferimento.

D

b) Si rappresenti il circuito determinato al punto a) mediante “stick

Y

diagram” rispettando la disposizione di ingressi e uscita rappresentati

C

nella figura a lato (tutte le linee sono rappresentative di metal).

GND

c) Supponendo di disporre delle model SPICE dei transistori, si

proponga il file spice che consente di descrivere il circuito e di valutare i tempi di propagazione

TPHL e TPLH tra l’ingresso D e l’uscita Y supponendo che A, B

e C siano posti a 0. Si supponga che i tempi da valutare siano

VDD

inferiori a 100 ns e che sia VDD=5 V.

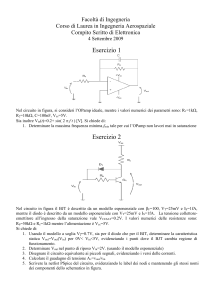

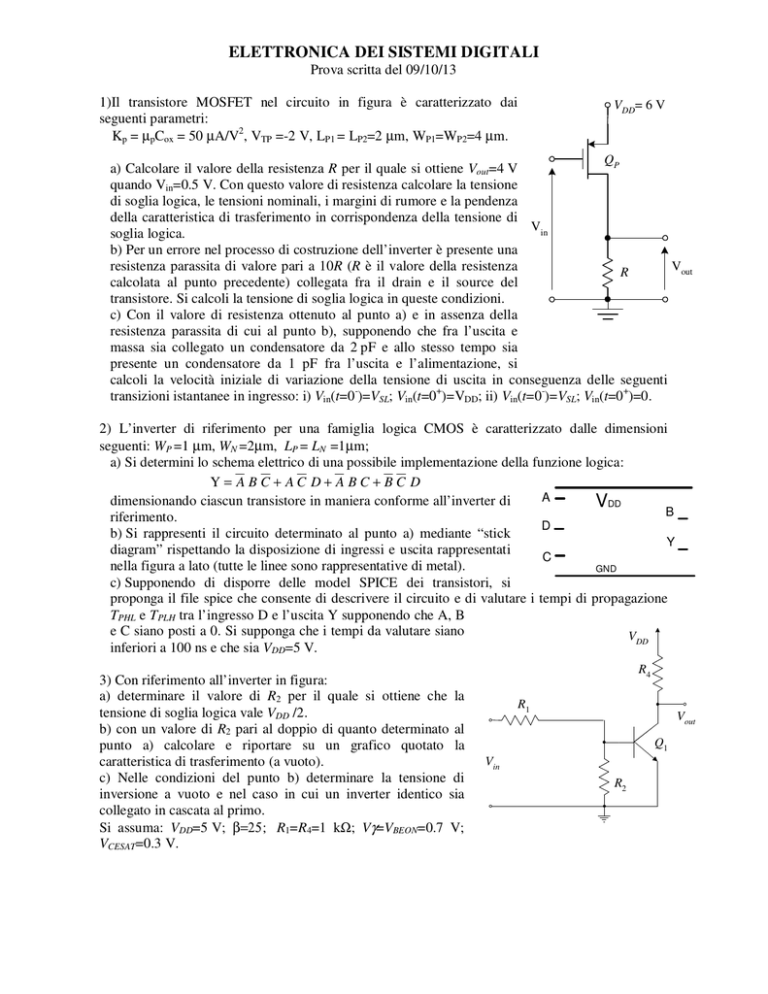

3) Con riferimento all’inverter in figura:

a) determinare il valore di R2 per il quale si ottiene che la

tensione di soglia logica vale VDD /2.

b) con un valore di R2 pari al doppio di quanto determinato al

punto a) calcolare e riportare su un grafico quotato la

caratteristica di trasferimento (a vuoto).

c) Nelle condizioni del punto b) determinare la tensione di

inversione a vuoto e nel caso in cui un inverter identico sia

collegato in cascata al primo.

Si assuma: VDD=5 V; β=25; R1=R4=1 kΩ; Vγ=VBEON=0.7 V;

VCESAT=0.3 V.

R4

R1

Vout

Q1

Vin

R2