ELETTRONICA DEI SISTEMI DIGITALI 1

PRIMA PROVA IN ITINERE – A.A. 2003/2004 – 11 Novembre 2003

12345678901234567890123456789012345678901234567890123456789012345678901234567890123456789

01234567890123456789012345678901234567890123456789012345678901234567890123456789012345678

90123456789012345678901234567890123456789012345678901234567890123456789012345678901234567

89012345678901234567890123456789012345678901234567890123456789012345678901234567890123456

78901234567890123456789012345678901234567890123456789012345678901234567890123456789012345

67890123456789012345678901234567890123456789012345678901234567890123456789012345678901234

56789012345678901234567890123456789012345678901234567890123456789012345678901234567890123

45678901234567890123456789012345678901234567890123456789012345678901234567890123456789012

34567890123456789012345678901234567890123456789012345678901234567890123456789012345678901

23456789012345678901234567890123456789012345678901234567890123456789012345678901234567890

12345678901234567890123456789012345678901234567890123456789012345678901234567890123456789

01234567890123456789012345678901234567890123456789012345678901234567890123456789012345678

90123456789012345678901234567890123456789012345678901234567890123456789012345678901234567

89012345678901234567890123456789012345678901234567890123456789012345678901234567890123456

78901234567890123456789012345678901234567890123456789012345678901234567890123456789012345

67890123456789012345678901234567890123456789012345678901234567890123456789012345678901234

56789012345678901234567890123456789012345678901234567890123456789012345678901234567890123

45678901234567890123456789012345678901234567890123456789012345678901234567890123456789012

34567890123456789012345678901234567890123456789012345678901234567890123456789012345678901

23456789012345678901234567890123456789012345678901234567890123456789012345678901234567890

12345678901234567890123456789012345678901234567890123456789012345678901234567890123456789

01234567890123456789012345678901234567890123456789012345678901234567890123456789012345678

90123456789012345678901234567890123456789012345678901234567890123456789012345678901234567

89012345678901234567890123456789012345678901234567890123456789012345678901234567890123456

78901234567890123456789012345678901234567890123456789012345678901234567890123456789012345

67890123456789012345678901234567890123456789012345678901234567890123456789012345678901234

56789012345678901234567890123456789012345678901234567890123456789012345678901234567890123

45678901234567890123456789012345678901234567890123456789012345678901234567890123456789012

34567890123456789012345678901234567890123456789012345678901234567890123456789012345678901

23456789012345678901234567890123456789012345678901234567890123456789012345678901234567890

12345678901234567890123456789012345678901234567890123456789012345678901234567890123456789

01234567890123456789012345678901234567890123456789012345678901234567890123456789012345678

90123456789012345678901234567890123456789012345678901234567890123456789012345678901234567

89012345678901234567890123456789012345678901234567890123456789012345678901234567890123456

78901234567890123456789012345678901234567890123456789012345678901234567890123456789012345

67890123456789012345678901234567890123456789012345678901234567890123456789012345678901234

56789012345678901234567890123456789012345678901234567890123456789012345678901234567890123

45678901234567890123456789012345678901234567890123456789012345678901234567890123456789012

34567890123456789012345678901234567890123456789012345678901234567890123456789012345678901

23456789012345678901234567890123456789012345678901234567890123456789012345678901234567890

COGNOME:

MATRICOLA:

NOME:

ORDINAMENTO (VO/NO):

Regole:

1) Non è consentito portare vicino al posto nulla che non siano penne, matite, gomma,

calcolatrice non programmabile. Giacconi, borse, appunti e cellulari devono essere

lasciati all’ingresso dell’aula.

2) Viene consegnato un gruppo di fogli pinzato di cui i primi contengono il testo e lo

spazio per riportare la soluzione, l’unica parte che verrà corretta è quella nei

riquadri appositamente indicati, il resto dei fogli deve essere consegnato ma non

verrà corretto.

3) Qualora la parte per la soluzione venisse pasticciata è possibile riscriverla su uno

degli altri fogli (nella stessa forma, non allungata) e fare un riferimento all'interno del

box soluzione. Il resto del compito ed il suo retro è pasticciabile a piacere. Non

verranno dati altri fogli.

4) Se i fogli vengono spinzati per errore, bisogna chiedere immediatamente che

vengano ripinzati.

5) Se un partecipante verrà trovato con fogli staccati, materiale non fornito dalla

commissione, o a scambiare informazioni con colleghi verrà allontanato e non gli

sarà permesso partecipare alle prove successive.

6) Il tempo per la soluzione è due ore e mezza durante le quali non è possibile andare

in bagno.

7) Verranno dati 5 minuti per la lettura di tutto il testo. Durante il compito, dopo tre

quarti d’ora circa e poi dopo altri 45 minuti, verranno dati altri due intervalli di 5

minuti durante i quali si potranno fare domande sulla comprensione del testo. Non

sarà possibile farlo durante il resto del compito.

8) La prova è costituita da 3 esercizi da 10 punti ciascuno.

Esercizio 1

Data la funzione:

Z = (A+BC+DEF)’

a) Disegnare lo schematico del circuito CMOS statico che la implementa ipotizzando

che B sia un segnale critico che arriva per ultimo.

b) Dimensionare tutti i transistor secondo i criteri del dimensionamento ottimo NON

semplificato sapendo che µn/µp=2

c) Scrivere un modulo verilog che implementi la funzione iniziale in stile strutturale

a) Circuito e b) Dimensionamento (scrivere il valore di W/L affianco a ciascun MOS)

W1 = 1 Wmin

W2 = W3 = 2 Wmin

W4 = W5 = W6 = 3 Wmin

W7 = W8 = W9 = W10 = W11 = W12 = 6 Wmin

I MOS pilotati da B sono più vicini all’uscita per minimizzare il numero di nodi parassiti da

pilotare quando commuta B.

c) Modulo verilog (scrivere in stampatello)

module my_func(A,B,C,D,E,F,Z);

input A,B,C,D,E,F;

output Z;

wire A,B,C,D,E,F,Z,A1,A2,O1;

and a1(A1,B,C);

and a2(A2,D,E,F);

or o1(O1,A,A1,A2);

not n1(Z,O1);

endmodule

Esercizio 2

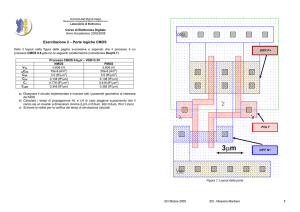

Dato il seguente layout ed un processo CMOS con parametri:

VTH

PMOS:

0.6 V

VDD=3.3V

NMOS:

0.6 V

VDSAT

0.4 V

0.4 V

µ COX

25 uA/V2

75 uA/V2

COX

3.5 fF/um2

3.5 fF/um2

COV

0.1 fF/um

0.1 fF/um

CJ

1 fF/um2

1 fF/um2

CJSW

1 fF/um

1 fF/um

Keq

0.5

0.5

a) Disegnare il circuito corrispondente (per chiarezza di disegno il metal1 non è

colorato internamente, ma è rappresentato da un riquadro vuoto, seguitene i

contorni per capire le interconnessioni).

b) Trovare la funzionalità logica implementata

c) Dire a quale famiglia logica appartiene la porta

d) Dire quale è la commutazione HL di caso peggiore e spiegare perché.

e) Determinare le dimensioni (W e L) di tutti i MOS, e solo le capacità parassite (ed

eventualmente aree e perimetri di diffusioni necessari per calcolarle) necessarie al

calcolo del tempo di propagazione per la commutazione individuata al punto d)

f) Calcolare il tempo di propagazione per la commutazione al punto d) nel caso si

abbia una carico di 10fF

1 QUADRATO = 0.2um

a) Circuito (dare un nome a ciascun MOS per potere compilare facilmente le domande

successive)

b) Funzione logica

Z=(ABC)’

c) Famiglia logica

PSEUDO-NMOS

d) Commutazione di caso peggiore

A

B

C

0->1

1

1

Perché:

Il caso peggiore per le commutazioni HL si ha quando la capacità da scaricare è massima

(quindi è coinvolto il maggior numero di capacità parassite) e quando la corrente a

disposizione per la scarica è minima. In questo caso si ha un solo percorso possibile per la

scarica (attraverso i 3 nmos), quindi si tratta di vedere semplicemente quando è massima

la capacità da scaricare.

Ovviamente il caso peggiore è quello in cui entrambi i nodi interni debbono essere

scaricati e questo succede appunto nella commutazione indicata perché, essendo B=1 e

C=1 i due nodi interni (drain di M2 e di M3) sono entrambi inizialmente connessi all’uscita,

quindi le capacità parassite che vi sono connesse debbono essere scaricate quando

commuta A accendendo M3.

In questa commutazione debbono essere pilotati i drain di M1, M2, M3, M4 (quindi tutte le

Cdb e Cgd associate) e i soli source di M1 e M2 (quindi anche le loro Csb e Cgs).

e) Dimensioni e capacità (compilare solo le caselle richieste dal testo, cioè tutte le W e L e

solo le caselle necessarie al calcole delle capacità parassite individuate al punto d)

NOME

W

L

AD

AS

PD

PS

Cdb

Csb

Cgd

Cgs

M4

1.20E-06

2.00E-06

1.68E-12

1.68E-12

4.00E-06

4.00E-06

2.84E-15

1.20E-16

M1

1.20E-06

4.00E-07

1.68E-12

3.60E-13

4.00E-06

6.00E-07

2.84E-15

4.80E-16

1.20E-16

1.24E-15

M2

1.20E-06

4.00E-07

3.60E-13

3.60E-13

6.00E-07

6.00E-07

4.80E-16

4.80E-16

1.20E-16

1.24E-15

M3

1.20E-06

4.00E-07

3.60E-13

1.68E-12

6.00E-07

4.00E-06

4.80E-16

1.20E-16

f) Tempo di propagazione

Si applica la formula di Elmore tenendo conto dei nodi interni N1 (source di M1 e drain di M2) e N2 (source

di M2 e drain di M3).

Cp1 = Csb1 + Cdb2 + Cgs1 + Cgd2 = 2.32 fF

Cp2 = Csb2 + Cdb3 + Cgs2 + 2Cgd3 = 2.44 fF (Cgd3 pesata 2 per Miller)

CL = CL’ + Cdb4 + Cdb1 + Cgd4 + Cgd1 = 15.92 fF

Isat1 = Isat2 = Isat3 = 225 uA

Req1 = Req2 = Req3 = Req = ¾ VDD/Isat1 = 11kΩ

tpHL = 0.69 Req (Cp2 + 2 Cp1 + 3 CL) = 416 psec

Esercizio 3

Dato il circuito in Figura, costituito da due porte logiche dinamiche in cascata:

a) Determinare la funzione logica Z1.

b) Determinare la funzione logica Z2 (ovviamente in funzione degli ingressi A, B e C)

c) Dire se esiste qualche potenziale problema nella connessione in cascata delle due

porte. Se la risposta è SI, dire per quale combinazione di ingresso (se più di una

basta citarne una sola) si può verificare il problema, se la risposta è NO spiegare

perché.

d) Scrivere la netlist spice per l’analisi in transitorio, supponendo che gli ingressi A, B

e C siano costanti e commuti il segnale di clock fn.

a) Funzione Z1

Z1= (AB)’

b) Funzione Z2

Z2 = ((AB)’+C)’ = ABC’

c) Connessione in cascata

Esiste un problema che si verifica, ad

Non esiste problema perché:

esempio, per la combinazione

A=1

B=1

C=0

e consiste nel fatto che l’uscita Z2 dovrebbe

essere pari a 1 (ABC’=1), però, siccome

all’inizio della valutazione sia Z1 che Z2

sono 1 (a causa della precarica), un

ingresso pari a 1 sul MOS M6 potrebbe

causare la scaricare di Z2 che non potrebbe

più essere ricaricato e quindi Z2 potrebbe

essere valutato erroneamente pari a 0.

d) Netlist spice

* Logica dinamica

* Inclusione dei modelli dei mos, gli nMOS sono definiti come N1 e i pMOS come P1

.include models.dat

* -- Netlist –

* Non essendo definite altrimenti nel testo prenderò dimensioni a scelta per

* le W e L di tutti i MOS

* Porta Z1

m1 Z1 fn vdd vdd p1 w=1u l=1u

m2 Z1 A 1 0 n1 w=1u l=1u

m3 1 B 2 0 n1 w=1u l=1u

m4 2 fn 0 0 n1 w=1u l=1u

* Porta Z2

m5 Z2 fn vdd vdd p1 w=1u l=1u

m6 Z2 Z1 3 0 n1 w=1u l=1u

m7 Z2 C 3 0 n1 w=1u l=1u

m8 3 fn 0 0 n1 w=1u l=1u

* Generatori

* Scelgo ad esempio la combinazione che ho individuato come problematica anch

* se non espressamente richiesto dal testo

vdd vdd 0 dc 3.3

va A 0 dc 3.3

vb B 0 dc 3.3

vc C 0 dc 0

vfn fn 0 pulse 0 3.3 1n 1p 1p 1n 2n

* Analisi

.tran 1p 4n

.end

ELETTRONICA DEI SISTEMI DIGITALI 1

PRIMA PROVA IN ITINERE – A.A. 2004/2005 – 10 Novembre 2004

12345678901234567890123456789012345678901234567890123456789012345678901234567890123456781

01234567890123456789012345678901234567890123456789012345678901234567890123456789012345678

90123456789012345678901234567890123456789012345678901234567890123456789012345678901234567

89012345678901234567890123456789012345678901234567890123456789012345678901234567890123456

78901234567890123456789012345678901234567890123456789012345678901234567890123456789012345

67890123456789012345678901234567890123456789012345678901234567890123456789012345678901234

56789012345678901234567890123456789012345678901234567890123456789012345678901234567890123

45678901234567890123456789012345678901234567890123456789012345678901234567890123456789012

34567890123456789012345678901234567890123456789012345678901234567890123456789012345678901

23456789012345678901234567890123456789012345678901234567890123456789012345678901234567890

12345678901234567890123456789012345678901234567890123456789012345678901234567890123456789

01234567890123456789012345678901234567890123456789012345678901234567890123456789012345678

90123456789012345678901234567890123456789012345678901234567890123456789012345678901234567

89012345678901234567890123456789012345678901234567890123456789012345678901234567890123456

78901234567890123456789012345678901234567890123456789012345678901234567890123456789012345

67890123456789012345678901234567890123456789012345678901234567890123456789012345678901234

56789012345678901234567890123456789012345678901234567890123456789012345678901234567890123

45678901234567890123456789012345678901234567890123456789012345678901234567890123456789012

34567890123456789012345678901234567890123456789012345678901234567890123456789012345678901

23456789012345678901234567890123456789012345678901234567890123456789012345678901234567890

12345678901234567890123456789012345678901234567890123456789012345678901234567890123456789

01234567890123456789012345678901234567890123456789012345678901234567890123456789012345678

90123456789012345678901234567890123456789012345678901234567890123456789012345678901234567

89012345678901234567890123456789012345678901234567890123456789012345678901234567890123456

78901234567890123456789012345678901234567890123456789012345678901234567890123456789012345

67890123456789012345678901234567890123456789012345678901234567890123456789012345678901234

56789012345678901234567890123456789012345678901234567890123456789012345678901234567890123

45678901234567890123456789012345678901234567890123456789012345678901234567890123456789012

34567890123456789012345678901234567890123456789012345678901234567890123456789012345678901

23456789012345678901234567890123456789012345678901234567890123456789012345678901234567890

12345678901234567890123456789012345678901234567890123456789012345678901234567890123456789

01234567890123456789012345678901234567890123456789012345678901234567890123456789012345678

90123456789012345678901234567890123456789012345678901234567890123456789012345678901234567

89012345678901234567890123456789012345678901234567890123456789012345678901234567890123456

78901234567890123456789012345678901234567890123456789012345678901234567890123456789012345

67890123456789012345678901234567890123456789012345678901234567890123456789012345678901234

56789012345678901234567890123456789012345678901234567890123456789012345678901234567890123

45678901234567890123456789012345678901234567890123456789012345678901234567890123456789012

34567890123456789012345678901234567890123456789012345678901234567890123456789012345678901

23456789012345678901234567890123456789012345678901234567890123456789012345678901234567890

COGNOME:

MATRICOLA:

NOME:

ORDINAMENTO (VO/NO):

Regole:

1) Non è consentito portare vicino al posto nulla che non siano penne, matite, gomma,

calcolatrice non programmabile. Giacconi, borse, appunti e cellulari devono essere

lasciati all’ingresso dell’aula.

2) Viene consegnato un gruppo di fogli pinzato di cui i primi contengono il testo e lo

spazio per riportare la soluzione, l’unica parte che verrà corretta è quella nei

riquadri appositamente indicati, il resto dei fogli deve essere consegnato ma non

verrà corretto.

3) Qualora la parte per la soluzione venisse pasticciata è possibile riscriverla su uno

degli altri fogli (nella stessa forma, non allungata) e fare un riferimento all'interno del

box soluzione. Il resto del compito ed il suo retro è pasticciabile a piacere. Non

verranno dati altri fogli.

4) Se i fogli vengono spinzati per errore, bisogna chiedere immediatamente che

vengano ripinzati.

5) Se un partecipante verrà trovato con fogli staccati, materiale non fornito dalla

commissione, o a scambiare informazioni con colleghi verrà allontanato e non gli

sarà permesso partecipare alle prove successive.

6) Il tempo per la soluzione è 2 ORE e 30 MINUTI durante le quali non è possibile

andare in bagno.

7) Dato che la prova si svolge in 2 aule separate non sarà possibile fare domande

durante il compito. All’inizio della prova saranno dati 5 minuti per la lettura del

testo dopo i quali si potranno fare domande sul testo degli esercizi. Altri 5 minuti di

domande verranno riservati a metà prova.

8) La prova è costituita da 3 esercizi da 10 punti ciascuno.

Esercizio 1

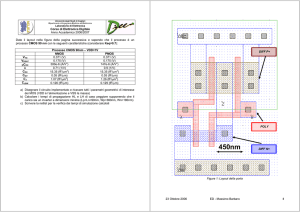

Dato il layout in Figura ed un processo CMOS 0.4um di parametri:

PMOS:

VDD=3.3V

NMOS:

VTH

0.6 V

0.6 V

VDSAT

0.4 V

0.4 V

µCOX

25 uA/V2

75 uA/V2

COV

0.1 fF/um

0.1 fF/um

CJ

1 fF/um2

1 fF/um2

CJSW

1 fF/um

1 fF/um

Keq

0.5

0.5

a) Disegnare lo schematico del circuito implementato (1 quadrato di lato = 0.2um)

b) Scrivere la netlist spice per la simulazione in transitorio del circuito, dettagliando TUTTI i

parametri geometrici di interesse

c) Determinare, QUALITATIVAMENTE, se la soglia logica è maggiore o minore di VDD/2 e

spiegare perché.

d) Calcolare il tempo di propagazione HL se il carico è una capacità pari a 10fF.

Layout

b) Netlist SPICE (SCRIVERE IN STAMPATELLO)

* Simulazione inverter

* Inclusione modelli

.include models.dat

* -------------* -- Netlist –

* -------------* Inverter

m2 Z A vdd vdd p1 w=2u l=0.4u ad=2.8e-12 pd=4.8u

m1 Z A 0 0 n1 w=1.2u l=0.4u ad=1.68e-12 pd=4u

* Carico

cl Z 0 10f

* -----------------* - Generatori –

* -----------------* Alimentazione

vdd vdd 0 dc 3.3

* Ingresso

va A 0 pulse 0 3.3 1n 1p 1p 1n 2n

* ------------* - Analisi * ------------.tran 1p 2n

.end

c) Soglia logica

La soglia logica è MINORE di VDD/2.

Infatti:

Il rapporto fra la mobilità del NMOS e del PMOS è 3 (dai dati del processo), tenendo conto

che le VDSAT sono uguali il PMOS dovrebbe essere 3 volte più largo del NMOS per avere

lo stesso K del pull-down. Così non è, il PMOS è solo poco meno del doppio del NMOS

quindi la soglia logica sarà minore di VDD/2 in quanto lo NMOS è troppo conduttivo e

l’ingresso deve diventare più basso per riuscire a fare diventare la sua corrente

equivalente a quella del pull-up.

d) Tempo di propagazione HL

Scrivere le formule utilizzate per calcolare ogni parametro

Isatn = unCOX (W/L) VDSAT (VDD – VTH – VDSAT/2) = 225uA

Reqn = ¾ VDD/Isatn = 11 kΩ

Cdbn = Keq (CJ AD1 + CJSW PD1) = 2.84 fF

Cgdn = COV W1 = 0.12 fF

Cdbp = Keq (CJ AD2 + CJSW PD2) = 3.8 fF

Cgdp = COV W2 = 0.2 fF

CL = CL’ + Cdbp + Cdbn + 2Cgdp + 2Cgdn = 17.28 fF

tpHL = 0.69*Reqn*CL = 131 psec

Esercizio 2

Dato il processo CMOS dell’esercizio precedente:

a) Disegnare il circuito della famiglia logica pseudo-NMOS che implementa una porta

NAND a 3 ingressi (A,B,C).

b) Dimensionare i transistor in modo che la rete di pull-down sia equivalente ad un NMOS

con (W/L)=2 e che la VOL sia al massimo pari a 100mV

c) Calcolare il massimo consumo di potenza statica e dire in corrispondenza di quale

combinazione di ingressi si verifica

a) Circuito (dare un nome a ciascun MOS)

b) Dimensionamento (con passaggi)

I transistor del pull-down sono 3 in serie e devono essere equivalenti ad uno solo con

Weq=2Lmin

L1 = L2 = L3 = Lmin = 0.4 um

W1 = W2 = W3 = 2*3*Lmin = 2.4 um

Per dimensionare il pmos impongo la tensione VOL quando i 3 nmos in serie sono accesi.

In tale condizione l’uscita è pari a VOL, il pmos è evidentemente in saturazione e lo nmos

equivalente in triodo. Le correnti del pmos e del nmos equivalente devono essere uguali:

Isatp = Itrioden

Isatp = upCOX (W/L)p VDSAT (VDD – VTH – VDSAT/2)

Itrioden = unCOX (W/L)n [ (VDD-VTH) VOL – VOL2/2] = 40uA

(W/L)p = 1.6

Ho ottenuto un valore maggiore di 1 (quindi L=Lmin e dimensiono W altrimenti avrei

fissatoW=Wmin e dimensionato L)

L = Lmin = 0.4 um

W = 1.6 Lmin = 0.64 um

In realtà posso avere solo multipli di 0.2 scelgo quindi:

W = 0.6 um

Isatp = 37.5uA

c) Massima potenza statica

In corrispondenza della combinazione

A

B

C

1

1

1

Si ha un consumo di :

Pstat = VDD Isatp = 3.3 * 37.5 uA = 124 uW

Perché:

Sia il pull-up che il pull-down sono accesi quindi scorre corrente dall’alimentazione a

massa. La corrente è quella di saturazione del pmos (che coincide con quella di triodo del

nmos equivalente).

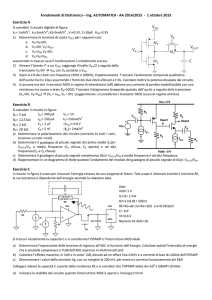

Esercizio 3

Dato il circuito in Figura (si consideri un processo CMOS con gli stessi parametri definiti

negli esercizi precedenti):

a) Determinare a che tipo di famiglia logica appartiene.

b) Determinare la funzione logica Z

c) Determinare il valore della tensione al nodo Z quando A=1, B=0 spiegando

brevemente come si è ricavato tale valore

a) Famiglia logica

PASS-TRANSISOR

b) Funzione Z

A

0

0

1

1

Z = A+B

c) Tensione al nodo Z

B

0

1

0

1

Z

0

1

1

1

( porta OR )

2.7V

Perché:

Quando A=1, B=0 risulta acceso il percorso attraverso M1 che deve copiare il valore di

VDD presente in ingresso sul nodo A. Per portare Z a VDD però il transistor M1 deve

caricare la capacità CL (tramite una corrente che scorre da A a Z, dunque A è il drain e Z il

source). Non appena V(Z) = VDD-VTH = 2.7V la VGS di M1 diventa VDD-(VDD-TH)=VTH

dunque M1 si spegne e non riesce a caricare ulteriormente il nodo Z.

ELETTRONICA DIGITALE

PRIMA PROVA IN ITINERE – A.A. 2005/2006 – 10 Novembre 2005

12345678901234567890123456789012345678901234567890123456789012345678901234567890123456781

01234567890123456789012345678901234567890123456789012345678901234567890123456789012345678

90123456789012345678901234567890123456789012345678901234567890123456789012345678901234567

89012345678901234567890123456789012345678901234567890123456789012345678901234567890123456

78901234567890123456789012345678901234567890123456789012345678901234567890123456789012345

67890123456789012345678901234567890123456789012345678901234567890123456789012345678901234

56789012345678901234567890123456789012345678901234567890123456789012345678901234567890123

45678901234567890123456789012345678901234567890123456789012345678901234567890123456789012

34567890123456789012345678901234567890123456789012345678901234567890123456789012345678901

23456789012345678901234567890123456789012345678901234567890123456789012345678901234567890

12345678901234567890123456789012345678901234567890123456789012345678901234567890123456789

01234567890123456789012345678901234567890123456789012345678901234567890123456789012345678

90123456789012345678901234567890123456789012345678901234567890123456789012345678901234567

89012345678901234567890123456789012345678901234567890123456789012345678901234567890123456

78901234567890123456789012345678901234567890123456789012345678901234567890123456789012345

67890123456789012345678901234567890123456789012345678901234567890123456789012345678901234

56789012345678901234567890123456789012345678901234567890123456789012345678901234567890123

45678901234567890123456789012345678901234567890123456789012345678901234567890123456789012

34567890123456789012345678901234567890123456789012345678901234567890123456789012345678901

23456789012345678901234567890123456789012345678901234567890123456789012345678901234567890

12345678901234567890123456789012345678901234567890123456789012345678901234567890123456789

01234567890123456789012345678901234567890123456789012345678901234567890123456789012345678

90123456789012345678901234567890123456789012345678901234567890123456789012345678901234567

89012345678901234567890123456789012345678901234567890123456789012345678901234567890123456

78901234567890123456789012345678901234567890123456789012345678901234567890123456789012345

67890123456789012345678901234567890123456789012345678901234567890123456789012345678901234

56789012345678901234567890123456789012345678901234567890123456789012345678901234567890123

45678901234567890123456789012345678901234567890123456789012345678901234567890123456789012

34567890123456789012345678901234567890123456789012345678901234567890123456789012345678901

23456789012345678901234567890123456789012345678901234567890123456789012345678901234567890

12345678901234567890123456789012345678901234567890123456789012345678901234567890123456789

01234567890123456789012345678901234567890123456789012345678901234567890123456789012345678

90123456789012345678901234567890123456789012345678901234567890123456789012345678901234567

89012345678901234567890123456789012345678901234567890123456789012345678901234567890123456

78901234567890123456789012345678901234567890123456789012345678901234567890123456789012345

67890123456789012345678901234567890123456789012345678901234567890123456789012345678901234

56789012345678901234567890123456789012345678901234567890123456789012345678901234567890123

45678901234567890123456789012345678901234567890123456789012345678901234567890123456789012

34567890123456789012345678901234567890123456789012345678901234567890123456789012345678901

23456789012345678901234567890123456789012345678901234567890123456789012345678901234567890

COGNOME:

MATRICOLA:

NOME:

Regole:

1) Non è consentito portare vicino al posto nulla che non siano penne, matite, gomma,

calcolatrice non programmabile. Giacconi, borse, appunti e cellulari devono essere

lasciati all’ingresso dell’aula.

2) Viene consegnato un gruppo di fogli pinzato di cui i primi contengono il testo e lo

spazio per riportare la soluzione, l’unica parte che verrà corretta è quella nei

riquadri appositamente indicati, il resto dei fogli deve essere consegnato ma non

verrà corretto.

3) Qualora la parte per la soluzione venisse pasticciata è possibile riscriverla su uno

degli altri fogli (nella stessa forma, non allungata) e fare un riferimento all'interno del

box soluzione. Il resto del compito ed il suo retro può essere pasticciato a piacere.

Non verranno dati altri fogli.

4) Se i fogli vengono staccati per errore, bisogna chiedere immediatamente che

vengano pinzati nuovamente.

5) Se un partecipante verrà trovato con fogli staccati, materiale non fornito dalla

commissione, od a scambiare informazioni con colleghi verrà allontanato e non gli

sarà permesso partecipare alle prove successive.

6) Il tempo per la soluzione è 2 ORE e 30 MINUTI durante le quali non è possibile

andare in bagno.

7) Dato che la prova si svolge in 2 aule separate non sarà possibile fare domande

durante il compito. All’inizio della prova saranno dati 5 minuti per la lettura del

testo dopo i quali si potranno fare domande sul testo degli esercizi. Altri 5 minuti di

domande verranno riservati a metà prova.

8) La prova è costituita da 3 esercizi.

Esercizio 1

Dato il layout in Figura ed un processo CMOS 0.5um di parametri:

VTH

PMOS:

0.6 V

VDD=3.3V

NMOS:

0.6 V

VDSAT

0.4 V

0.4 V

µ COX

30 uA/V2

60 uA/V2

COX

4 fF/um2

4 fF/um2

COV

0.1 fF/um

0.1 fF/um

CJ

1 fF/um2

1 fF/um2

CJSW

2 fF/um

2 fF/um

Keq

0.5

0.5

a) Disegnare lo schematico del circuito implementato (lato di 1 quadrato = 0.25um)

b) Determinare la famiglia logica a cui appartiene il circuito.

c) Individuare la funzione logica implementata (espressione algebrica e nome). Il segnale

S0’ è ovviamente il negato di S0 ed il segnale S1’ il negato di S1.

d) Calcolare il tempo di propagazione nel caso della combinazione A=0, B=1, C=0, D=1,

S1=0 (quindi S1’=1), S0: 1->0 (quindi S0’:0->1) se il carico è una capacità pari a 10fF.

Layout (lato di 1 quadrato = 0.25um)

a) Schematico del circuito. Dare un nome a ciascun MOS (M1, M2, M3, etc.)

b) Famiglia logica

Pass-transistor

c) Funzione logica

Espressione algebrica

Z = A S1’ S0’ + B S1’ S0 + C S1 S0’ + D S1 S0

Nome della porta logica (es. AND

a 4 ingressi, XOR, etc. etc.)

Multiplexer 4x1 (a seconda della combinazione di

ingressi S1 e S0 fa passare uno fra A, B, C e D)

d) Tempo di propagazione

Nella combinazione indicata la commutazione è (segnare con una crocetta):

HL

LH

La corrente di scarica/carica è quella corrispondente al percorso:

M1-M2 (in realtà al commutare di S0 il nodo interno N1 è GIA’ scarico e deve essere

scaricato solo Z ed il nodo interno N3, notare che di N3 non si può conoscere lo

stato di carica o scarica quindi bisogna considerare il caso peggiore)

spiegare brevemente il perché

Al commutare di S0 si passa da una combinazione in cui Z era 1 ad una in cui Z

deve diventare 0. Il nodo interno N1 è già scarico, N3 non necesariamente (non si

sa). Quindi attraverso il percorso M1-M2 bisogna scaricare il nodo Z ed il nodo N3.

Le capacità parassite coinvolte sono (calcolare il valore SOLO DELLE CAPACITA’

COINVOLTE nella commutazione e mettere una crocetta nella colonna opportuna se

la capacità subisce effetto Miller). Calcolare il valore di una capacità non necessaria

sarà considerato un ERRORE.

NOME MOS Cdb

M1

6.31E-15

M2

M3

6.31E-15

M4

M5

1.03E-15

M6

M7

6.31E-15

M8

Csb

Cgd

Cgs

Miller

1.50E-16

*

1.50E-16

*

1.03E-15

1.50E-16

6.31E-15

1.50E-16

1.50E-16

2.15E-15

* (per Cgs6 devo mettere anche il contributo di canale)

*

Capacità parassite:

CL = CL’ + Cdb2 + Cdb4 + Csb6 + Cdb8 + 2*(Cgd2 + Cgd4 + Cgs6 + Cgd8) = 40.44 fF

Cpn3 = Cdb5 + Cdb6 + Cgd5 + 2*Cgd6 = 2.51 fF

La corrente di carica/scarica è (indicare la formula usata):

Isat = unCOX (W/L)2 VDSAT (VDD – VTH – VDSAT/2) = 180 uA

R1 = R2 = R6 = Req = 13.75 kΩ

Il tempo di propagazione richiesto è (indicare la formula usata):

tp = 0.69 [CL (R1+R2) + Cpn3 (R1+R2)] = 0.69 2Req (CL+Cpn3) = 815 psec

(il percorso di scarica in comune fra CL e Cpn3 è dato dalle sole R1 e R2)

Esercizio 2

Data la seguente netlist spice ed il processo CMOS dell’esercizio precedente:

a) Disegnare lo schematico corrispondente.

b) Dire se la porta è dimensionata in modo ottimo (NON SEMPLIFICATO); se no, spiegare

qualitativamente quale è il tempo di propagazione maggiore (HL o LH) e correggere i

valori del dimensionamento per avere un dimensionamento ottimo.

c) Individuare la commutazione HL di caso peggiore (del circuito originale) e spiegare

perché

* Porta logica TALDEITALI

* Inclusione modelli (N1 è lo NMOS e P1 il PMOS)

.include model.dat

* Netlist

M1 Z A 1 vdd P1 W=0.5u L=0.5u

M2 1 B vdd vdd P1 W=0.5u L=0.5u

M3 Z C 2 vdd P1 W=0.5u L=0.5u

M4 2 D vdd vdd P1 W=0.5u L=0.5u

M5 Z A 3 0 N1 W=0.5u L=0.5u

M6 Z B 3 0 N1 W=0.5u L=0.5u

M7 3 C 0 0 N1 W=0.5u L=0.5u

M8 3 D 0 0 N1 W=0.5u L=0.5u

* Non si fanno analisi e non ci sono generatori

.end

a) Circuito (dare un nome a ciascun MOS ed indicare il valore di W/L).

b) Dimensionamento

Il caso peggiore è dato da una commutazione (segnare con una crocetta):

HL

LH

Perché:

Il dimensionamento non è ottimo ed il percorso di carica peggiore (che coinvolge 2

pmos) risulta più resistivo del percorso di scarica peggiore (che coinvolge

ugualmente 2 nmos). Il percorso di carica infatti è equivalente ad un mos di

dimensione

Kp,equiv = up COX (W/L)p,equiv = ½ un COX (W/L)p,equiv = ¼ un COX

Il percorso di scarica invece:

Kn,equiv = un COX (W/L)n,equiv = ½ un COX

Kp,equiv < Kn,equiv

Il dimensionamento ottimo è mostrato in Figura dal numero fra parentesi.

c) Commutazione di caso peggiore

La commutazione HL di caso peggiore (prima delle modifiche) corrisponde alla seguente

combinazione:

A=0 B=1 C=0 D:0->1

Perché:

In tale situazione, a parità di corrente di scarica risulta massima la capacità

parassita totale da scaricare poiché tutti i nodi interni sono coinvolti nella

commutazione: infatti N3 è nel mezzo del percorso di scarica e N1 e N2 sono

connessi all’uscita da M1 e M4.

Esercizio 3

Implementare il circuito in logica CMOS dinamica corrispondente alla funzione

Z=[(A+B)’(C+D)]’

e spiegare le scelte fatte.

a) Schematico del circuito (utilizzare un approccio a due livelli di logica, ossia con 2

porte in cascata).

b) Motivazioni

Si è utilizzata una implementazione in logica np per evitare i problemi dovuti alla

connessione di due blocchi dinamici in cascata.

L’uscita del primo blocco è:

Z1 = (A+B)’

L’uscita del secondo è:

Z = Z1’ + (C’D’) = (A+B)+(C’D’) = [(A+B)+(C’D’)]’’ = [(A+B)’(C’D’)’]’ = [(A+B)’(C+D)]’

ELETTRONICA DIGITALE

PRIMA PROVA IN ITINERE – A.A. 2006/2007 – 17 Novembre 2006

12345678901234567890123456789012345678901234567890123456789012345678901234567890123456781

01234567890123456789012345678901234567890123456789012345678901234567890123456789012345678

90123456789012345678901234567890123456789012345678901234567890123456789012345678901234567

89012345678901234567890123456789012345678901234567890123456789012345678901234567890123456

78901234567890123456789012345678901234567890123456789012345678901234567890123456789012345

67890123456789012345678901234567890123456789012345678901234567890123456789012345678901234

56789012345678901234567890123456789012345678901234567890123456789012345678901234567890123

45678901234567890123456789012345678901234567890123456789012345678901234567890123456789012

34567890123456789012345678901234567890123456789012345678901234567890123456789012345678901

23456789012345678901234567890123456789012345678901234567890123456789012345678901234567890

12345678901234567890123456789012345678901234567890123456789012345678901234567890123456789

01234567890123456789012345678901234567890123456789012345678901234567890123456789012345678

90123456789012345678901234567890123456789012345678901234567890123456789012345678901234567

89012345678901234567890123456789012345678901234567890123456789012345678901234567890123456

78901234567890123456789012345678901234567890123456789012345678901234567890123456789012345

67890123456789012345678901234567890123456789012345678901234567890123456789012345678901234

56789012345678901234567890123456789012345678901234567890123456789012345678901234567890123

45678901234567890123456789012345678901234567890123456789012345678901234567890123456789012

34567890123456789012345678901234567890123456789012345678901234567890123456789012345678901

23456789012345678901234567890123456789012345678901234567890123456789012345678901234567890

12345678901234567890123456789012345678901234567890123456789012345678901234567890123456789

01234567890123456789012345678901234567890123456789012345678901234567890123456789012345678

90123456789012345678901234567890123456789012345678901234567890123456789012345678901234567

89012345678901234567890123456789012345678901234567890123456789012345678901234567890123456

78901234567890123456789012345678901234567890123456789012345678901234567890123456789012345

67890123456789012345678901234567890123456789012345678901234567890123456789012345678901234

56789012345678901234567890123456789012345678901234567890123456789012345678901234567890123

45678901234567890123456789012345678901234567890123456789012345678901234567890123456789012

34567890123456789012345678901234567890123456789012345678901234567890123456789012345678901

23456789012345678901234567890123456789012345678901234567890123456789012345678901234567890

12345678901234567890123456789012345678901234567890123456789012345678901234567890123456789

01234567890123456789012345678901234567890123456789012345678901234567890123456789012345678

90123456789012345678901234567890123456789012345678901234567890123456789012345678901234567

89012345678901234567890123456789012345678901234567890123456789012345678901234567890123456

78901234567890123456789012345678901234567890123456789012345678901234567890123456789012345

67890123456789012345678901234567890123456789012345678901234567890123456789012345678901234

56789012345678901234567890123456789012345678901234567890123456789012345678901234567890123

45678901234567890123456789012345678901234567890123456789012345678901234567890123456789012

34567890123456789012345678901234567890123456789012345678901234567890123456789012345678901

19456789012345678901234567890123456789012345678901234567890123456789012345678901234567890

COGNOME:

MATRICOLA:

NOME:

Regole:

1) Non è consentito portare vicino al posto nulla che non siano penne, matite, gomma,

calcolatrice non programmabile. Giacconi, borse, appunti e cellulari devono essere

lasciati all’ingresso dell’aula.

2) Viene consegnato un gruppo di fogli pinzato di cui i primi contengono il testo e lo

spazio per riportare la soluzione, l’unica parte che verrà corretta è quella nei

riquadri appositamente indicati, il resto dei fogli deve essere consegnato ma non

verrà corretto.

3) Qualora la parte per la soluzione venisse pasticciata è possibile riscriverla su uno

degli altri fogli (nella stessa forma, non allungata) e fare un riferimento all'interno del

box soluzione. Il resto del compito ed il suo retro può essere pasticciato a piacere.

Non verranno dati altri fogli.

4) Se i fogli vengono staccati per errore, bisogna chiedere immediatamente che

vengano pinzati nuovamente.

5) Se un partecipante verrà trovato con fogli staccati, materiale non fornito dalla

commissione, od a scambiare informazioni con colleghi verrà allontanato e non gli

sarà permesso partecipare alle prove successive.

6) Il tempo per la soluzione è 2 ORE e 30 MINUTI durante le quali non è possibile

andare in bagno.

7) All’inizio della prova saranno dati 5 minuti per la lettura del testo dopo i quali si

potranno fare domande sul testo degli esercizi. Sarà consentito fare altre domande

solo ogni 30 minuti, restando al posto ed alzando la mano.

8) La prova è costituita da 3 esercizi.

Esercizio 1

Dato il layout in Figura ed un processo CMOS 90nm di parametri:

VDSAT

µ COX

COV

VTH

0.3 V

0.1 V

150 uA/V2

PMOS:

0.1 fF/um

VDD=1 V

2

NMOS: COX = 20 fF/um

0.3 V

0.1 V

300 uA/V2

0.1 fF/um

WMIN = 180nm, LMIN = 90nm

CJ

1 fF/um2

1 fF/um2

CJSW

2 fF/um

2 fF/um

Keq

0.5

0.5

a) Disegnare lo schematico del circuito implementato (lato di 1 quadrato = 0.045um = 45nm)

b) Determinare la famiglia logica a cui appartiene il circuito (il nome completo, se si tratta di una tipologia

particolare di una certa famiglia).

c) Individuare la funzione logica implementata al nodo Z1 ed al nodo Z in funzione del solo segnale A. Il

segnale fp è il negato di fn. Indicare anche di che tipo di porte logiche si tratta.

d) Calcolare il tempo di propagazione HL del segnale Z1 al variare di fn se A è costante.

e) Descrivere il meccanismo di commutazione LH del segnale Z.

SUGGERIMENTO: Si tratta di due porte in cascata.

Layout (lato di 1 quadrato = 0.045um)

a) Schematico del circuito. Dare un nome a ciascun MOS (M1, M2, M3, etc.)

Dimensioni geometriche da misurare sul layout:

L1 = L2 = L3 = L4 = LMIN = 90nm

W1 = W2 = W3 = 4*45 nm = 180nm

W4 = 6*45nm = 270nm

AD2 = AD1 = (6*6+4) (0.045)2 um2 = 0.081 um2

AS2 = AD3 = (4*3) (0.045)2 / 2 um2 = 0.01215 um2

PD2 = PD1 = (7+6+6+2+1) (0.045) um = 0.99 um

PS2 = PD3 = (3+3) (0.045) / 2 um = 0.135 um

Capacità parassite:

Cdb2 = Cdb1 = Keq (CJ AD2 + CJSW PD2) = 1.03 fF

Cdb3 = Csb2 = Keq (CJ AD3 + CJSW PD3) = 0.14 fF

Cgd1 = Cgd2 = Cgd3 = COV W2 = 0.018 fF

Cgs2 = COV W2 + 2/3 COX W2L2 = 0.246 fF (considero anche il contributo del canale)

Cg4 = COX W4 L4 = 0.486 fF

b) Famiglia logica

Logica dinamica np

c) Funzione logica

Espressione algebrica

Z1 = A’

Z = Z1’ = A

Si tratta di (tipo di porte): Due inverter in cascata (buffer non invertente).

d) Tempo di propagazione di Z1

La corrente di scarica è quella corrispondente al percorso:

M2-M3

spiegare brevemente il perché

Quando fn va alto e A=1 si chiude il suddetto percorso che scarica a 0 il segnale Z1.

Le capacità parassite coinvolte sono (calcolare il valore SOLO DELLE CAPACITA’

COINVOLTE nella commutazione e mettere una crocetta nella colonna opportuna se

la capacità subisce effetto Miller

NOME MOS

M1

M2

M3

M4

Cdb

1.03 fF

1.03 fF

0.14 fF

Csb

0.14 fF

Cgd

0.018 fF

0.018 fF

0.018 fF

Cgs

Cg

Miller

*

0.246 fF

*

0.486fF

Le capacità coinvolte sono (elencarle tutte, con formula e valore):

Cp1 = Cdb3 + Csb2 + 2Cgd3 + Cgs2 = 0.562 fF

CpZ1 = Cdb1 + Cdb2 + 2Cgd1 + Cgd2 + Cg4 = 2.6 fF

La formula di Elmore risulta (fare tutti i passaggi):

Isat = unCOX W/L VDSATn (VDD – VTH –VDSATN/2 ) = 39 uA

Req = ¾ VDD/Isat = 19.2 kΩ

τ = Req (Cp1 + 2 CpZ1 ) = 110.6 psec

Il tempo di propagazione richiesto è (indicare la formula usata):

tp = 0.69 τ = 76 psec

e) Meccanismo di commutazione LH di Z

La logica è dinamica, dunque funziona in 2 fasi. Quando fn=0 (fp=1) il nodo Z1 viene

precaricato a VDD (da M1) e Z precaricato a 0 (da M6). Quando fn diventa 1 (fp=0) inizia

la fase di valutazione: se A=1 la PDN1 scarica Z1 a 0, innesca in questo modo la PUN2

che porta Z a VDD.

Il meccanismo di commutazione HL è ovviamente l’opposto: se A=0 la PDN1 NON scarica

Z1, dunque la PUN2 NON carica Z che rimane al valore a cui era stato precaricato (0).

Esercizio 2 (STESSA TECNOLOGIA CMOS DELL’ESERCIZIO 1)

a) Implementare il circuito, in logica pseudo-NMOS, corrispondente alla funzione

Z=[(A+B)(C+D)]’

dimensionando la rete di pull-down in modo che ciascun percorso di scarica equivalga ad

un NMOS a dimensioni minime (W = WMIN = 180nm, L = LMIN = 90nm) e dimensionando il

PMOS in modo che:

VOL = 5 mV

b) Calcolare la potenza statica dissipata ed individuare una combinazione di ingressi per

cui si ha tale dissipazione di potenza.

SUGGERIMENTO1: Ricordare che le dimensioni possono essere solo multipli del

passo della griglia (45nm).

SUGGERIMENTO2: Nel calcolare la corrente di triodo di un MOS è consigliato di

trascurare il termine quadratico di VDS.

a1) Schematico del circuito (DARE UN NOME AI MOS)

a2) Dimensionamento

NMOS:

W1 = 360nm

W2 = 360nm

W3 = 360nm

W4 = 360nm

L1 = 90nm

L2 = 90nm

L3 = 90nm

L4 = 90nm

Il dimensionamento degli NMOS si basa sul seguente ragionamento:

Ovviamente gli NMOS sono tutti realizzati a LMIN (90nm). Per le W bisogna imporre che in

ciascun percorso di scarica la Weq sia uguale a WMIN (180nm). I possibili percorsi di

scarica singoli sono tutti costituiti da 2 NMOS in serie, ossia M1-M3, M1-M4, M2-M3, M2M4. Poiché, per 2 MOS in serie:

(W/L)eq = (W/L) / 2 => W = 2 Weq = 360nm

PMOS:

WP = WMIN = 180nm

LP = 855 nm

Il dimensionamento del PMOS si basa sul seguente ragionamento (FORMULE):

Il PMOS viene dimensionato imponendo il valore della VOL. La condizione peggiore è

quella in cui sono accesi solo 2 NMOS in serie (minore corrente di pull-down a

disposizione). In tale condizione, essendo acceso anche il PMOS, le correnti del NMOS

equivalente e del PMOS devono essere uguali. Il PMOS sarà sicuramente in saturazione

(VSD = VDD – VOL = 0.995 V) mentre lo NMOS sarà in triodo (VDS = VOL = 0.005 V)

dunque:

IDp = IDn

upCOX (W/L)p VDSATp (VDD – VTH –VDSATp/2) = unCOX (W/L)eq (VDD – VTH) VOL

(W/L)p = 0.215

Essendo il rapporto minore di 1 bisogna fissare il valore di W (WMIN) e ricavare L:

LP = WMIN / 0.215 = 837 nm ≈ 855 nm (devo scegliere il multiplo di 45nm più prossimo,

ma maggiore)

b) Potenza statica

Si consuma potenza statica, ad esempio, con la seguente combinazione di ingressi:

A=1

B=0

C=1

D=0

La potenza vale (scrivere i passaggi):

Per questa combinazione la rete PDN è accesa ed è acceso anche il PMOS, la potenza è

data dal prodotto fra la tensione di alimentazione e la corrente erogata che coincide con la

corrente del PMOS.

Isatp = upCOX (W/L)p VDSATp (VDD – VTH – VDSATp/2) = 2 uA

Pstat = VDD Isatp = 2 uW

Esercizio 3 (STESSA TECNOLOGIA CMOS DELL’ESERCIZIO 1)

Lo schematico in Figura mostra una porta logica di tipo DCVSL (Differential Cascode Voltage

Switch Logic) che rappresenta un’evoluzione della famiglia logica pseudo-NMOS. Sapendo che

i 2 PMOS sono dimensionati con W/L = 0.1 mentre gli NMOS delle due PDN del circuito sono

dimensionati in modo ottimo (qualsiasi percorso di scarica singolo equivalente ad un NMOS

con W/L=WMIN/LMIN) e notando che, come dice il nome, l’uscita Z’ deve essere il negato di Z:

a) Determinare la funzione logica Z implementata dal circuito (tabella di verità ed

espressione algebrica).

b) Determinare il valore di VOL.

c) Determinare il consumo di potenza statico.

a) Funzione logica

A

0

0

0

0

1

1

1

1

B

0

0

1

1

0

0

1

1

C

0

1

0

1

0

1

0

1

Z

1

1

1

0

0

0

0

0

Z = [A+BC]’

Spiegazione:

Quando la rete di pull-down di sinistra (PDN1) si chiude cerca di portare Z a 0. Allo stesso

tempo la PDN di destra (PDN2) si apre, essendo duale alla PDN1. Il PMOS M7, in tale

situazione, potrebbe essere acceso o spento (a seconda del valore di Z’). In ogni caso,

visto che W/L = 0.1, il PMOS è molto meno conduttivo della PDN1 ed il valore di Z riesce a

scendere. Quando Z scende abbastanza (almeno sotto VDD-VTH), accende il PMOS M8

che porta alto Z’ (fino a VDD, fino che la PDN2 è spenta). Visto che Z’ va a VDD il PMOS

M7 si spegne e, in tale situazione, la PDN1 riesce a portare fino a 0 l’uscita Z. Quando

l’uscita deve essere 1 accade il contrario: la PDN1 si spegne e la PDN2 si accende, la

PDN2 porta Z’ abbastanza in basso da accendere M7 che porta Z fino a VDD.

b) VOL

VOL = 0

Spiegazione:

Come descritto in precedenza, quando la PDN1 è accesa porta Z abbastanza in basso da

accendere M8 che porta Z’ a VDD (visto che PDN2 è spenta) e spegne M7. Quando M7 si

spegne, PDN1 riesce a terminare la commutazione di Z portandolo fino a 0.

c) Potenza statica

Pstat = 0

Spiegazione:

Come descritto in precedenza, quando la PDN1 è accesa si spegne M7. Quando invece è

accesa la PDN2 si spegne M8, dunque non c’è mai una situazione in cui scorra

direttamente corrente dall’alimentazione alla massa.

ELETTRONICA DIGITALE

PRIMA PROVA IN ITINERE – A.A. 2007/2008 – 16 Novembre 2007

12345678901234567890123456789012345678901234567890123456789012345678901234567890123456781

01234567890123456789012345678901234567890123456789012345678901234567890123456789012345678

90123456789012345678901234567890123456789012345678901234567890123456789012345678901234567

89012345678901234567890123456789012345678901234567890123456789012345678901234567890123456

78901234567890123456789012345678901234567890123456789012345678901234567890123456789012345

67890123456789012345678901234567890123456789012345678901234567890123456789012345678901234

56789012345678901234567890123456789012345678901234567890123456789012345678901234567890123

45678901234567890123456789012345678901234567890123456789012345678901234567890123456789012

34567890123456789012345678901234567890123456789012345678901234567890123456789012345678901

23456789012345678901234567890123456789012345678901234567890123456789012345678901234567890

12345678901234567890123456789012345678901234567890123456789012345678901234567890123456789

01234567890123456789012345678901234567890123456789012345678901234567890123456789012345678

90123456789012345678901234567890123456789012345678901234567890123456789012345678901234567

89012345678901234567890123456789012345678901234567890123456789012345678901234567890123456

78901234567890123456789012345678901234567890123456789012345678901234567890123456789012345

67890123456789012345678901234567890123456789012345678901234567890123456789012345678901234

56789012345678901234567890123456789012345678901234567890123456789012345678901234567890123

45678901234567890123456789012345678901234567890123456789012345678901234567890123456789012

34567890123456789012345678901234567890123456789012345678901234567890123456789012345678901

23456789012345678901234567890123456789012345678901234567890123456789012345678901234567890

12345678901234567890123456789012345678901234567890123456789012345678901234567890123456789

01234567890123456789012345678901234567890123456789012345678901234567890123456789012345678

90123456789012345678901234567890123456789012345678901234567890123456789012345678901234567

89012345678901234567890123456789012345678901234567890123456789012345678901234567890123456

78901234567890123456789012345678901234567890123456789012345678901234567890123456789012345

67890123456789012345678901234567890123456789012345678901234567890123456789012345678901234

56789012345678901234567890123456789012345678901234567890123456789012345678901234567890123

45678901234567890123456789012345678901234567890123456789012345678901234567890123456789012

34567890123456789012345678901234567890123456789012345678901234567890123456789012345678901

23456789012345678901234567890123456789012345678901234567890123456789012345678901234567890

12345678901234567890123456789012345678901234567890123456789012345678901234567890123456789

01234567890123456789012345678901234567890123456789012345678901234567890123456789012345678

90123456789012345678901234567890123456789012345678901234567890123456789012345678901234567

89012345678901234567890123456789012345678901234567890123456789012345678901234567890123456

78901234567890123456789012345678901234567890123456789012345678901234567890123456789012345

67890123456789012345678901234567890123456789012345678901234567890123456789012345678901234

56789012345678901234567890123456789012345678901234567890123456789012345678901234567890123

45678901234567890123456789012345678901234567890123456789012345678901234567890123456789012

34567890123456789012345678901234567890123456789012345678901234567890123456789012345678901

19456789012345678901234567890123456789012345678901234567890123456789012345678901234567890

COGNOME:

MATRICOLA:

NOME:

Regole:

1) Non è consentito portare vicino al posto nulla che non siano penne, matite, gomma,

calcolatrice non programmabile. Giacconi, borse, appunti e cellulari devono essere

lasciati all’ingresso dell’aula.

2) Viene consegnato un gruppo di fogli pinzato di cui i primi contengono il testo e lo

spazio per riportare la soluzione, l’unica parte che verrà corretta è quella nei

riquadri appositamente indicati, il resto dei fogli deve essere consegnato ma non

verrà corretto.

3) Qualora la parte per la soluzione venisse pasticciata è possibile riscriverla su uno

degli altri fogli (nella stessa forma, non allungata) e fare un riferimento all'interno del

box soluzione. Il resto del compito ed il suo retro può essere pasticciato a piacere.

Non verranno dati altri fogli.

4) Se i fogli vengono staccati per errore, bisogna chiedere immediatamente che

vengano pinzati nuovamente.

5) Se un partecipante verrà trovato con fogli staccati, materiale non fornito dalla

commissione, od a scambiare informazioni con colleghi verrà allontanato e non gli

sarà permesso partecipare alle prove successive.

6) Il tempo per la soluzione è 3 ORE durante le quali non è possibile andare in bagno.

7) All’inizio della prova saranno dati 5 minuti per la lettura del testo dopo i quali si

potranno fare domande sul testo degli esercizi. Sarà consentito fare altre domande

solo ogni 30 minuti, restando al posto ed alzando la mano.

8) La prova è costituita da 3 esercizi.

Esercizio 1

Dato il layout in Figura ed un processo CMOS 90nm di parametri:

VDSAT

µ COX

COV

VTH

0.3 V

0.1 V

150 uA/V2

PMOS:

0.1 fF/um

VDD=1 V

2

NMOS: COX = 20 fF/um

0.3 V

0.1 V

300 uA/V2

0.1 fF/um

WMIN = 180nm, LMIN = 90nm

a)

b)

c)

d)

e)

CJ

1 fF/um2

1 fF/um2

CJSW

2 fF/um

2 fF/um

Keq

0.5

0.5

Disegnare lo schematico del circuito implementato (lato di 1 quadrato = 0.045um = 45nm)

Determinare la famiglia logica a cui appartiene il circuito.

Individuare la funzione logica implementata al nodo Z.

Calcolare il tempo di propagazione LH nel caso peggiore sapendo che il carico vale 1fF.

Il circuito è dimensionato in modo ottimo semplificato? Se no, dimensionarlo in modo ottimo semplificato.

Layout (lato di 1 quadrato = 0.045um)

a) Schematico del circuito. Dare un nome a ciascun MOS (M1, M2, M3, etc.) e mettere

affianco le sue dimensioni W/L.

e) Modifiche al circuito. Mettere fra parentesi le nuove dimensioni richieste per il

dimensionamento ottimo.

Le dimensioni sul layout sono:

(W/L)1 = (W/L)2 = (W/L)3 = 180nm / 90nm = 2

(W/L)4 = (W/L)5 = (W/L)6 = 360nm / 90nm = 4

Per avere un dimensionamento

semplificato bisognerebbe avere:

ottimo

(W/L)1 = (Wmin/Lmin) = 180nm / 90nm

(M1 è il solo MOS sul percorso)

(W/L)2 = (W/L)3 = 2(Wmin/Lmin) = 360nm / 90nm

(M2 e M3 sono in serie quindi debbono essere

il doppio del transistor minimo per essere

equivalenti ad esso)

(W/L)4 = (W/L)5 = (W/L)6 = 4(Wmin/Lmin) =

=720nm / 90nm

(M4 e M5, oppure M4 e M6 sono in serie

dunque debbono essere il doppio del PMOS

equivalente che, a sua volta, per il

dimensionamento ottimo semplificato, deve

essere il doppio del transistor minimo)

b) Famiglia logica

CMOS statica

c) Funzione logica

Espressione algebrica

Z = (A+BC)’

d) Tempo di propagazione LH

La commutazione di caso peggiore corrisponde alla combinazione:

A=0

B=1

C=1→0

spiegare brevemente il perché:

in corrispondenza di tale commutazione sono coinvolti entrambi i nodi parassiti, N1

perché è all’interno del percorso di carica ed è inizialmente scarico (M4 è acceso) e N2

perché è connesso a Z tramite M2 (acceso).

Le capacità parassite coinvolte sono (calcolare il valore SOLO DELLE CAPACITA’

COINVOLTE nella commutazione e mettere una crocetta nella colonna opportuna se la

capacità subisce effetto Miller)

NOME MOS

M1

M2

M3

M4

M5

M6

Cdb (fF)

0.4723

0.4723

0.141

1.05

0.3923

1.05

Csb (fF)

0.141

0.3923

Cgd (fF)

0.018

0.18

0.018

0.036

0.036

0.036

Le capacità coinvolte sono (elencarle tutte, con formula e valore):

Dimensioni:

(W/L)1 = (W/L)2 = (W/L)3 = 180 / 90 = 2

(W/L)4 = (W/L)5 = (W/L)6 = 360 / 90 = 4

Aree e perimetri:

AD4 = AD6 = 56 (0.045)2 um2 = 0.1134 um2

PD4 = PD6 = 22 (0.045) um = 0.99 um

AD5 = AS4 = 64 (0.045)2 /2 um2 = 0.0648 um2

PD5 = PS4 = 16 (0.045) /2 um = 0.36 um

AD1 = AD2 = 44 (0.045)2 /2 um2 = 0.0445 um2

PD1 = PD2 = 20 (0.045) /2 um = 0.45 um

AD3 = AS2 = 12 (0.045)2 /2 um2 = 0.01215 um2

PD3 = PS2 = 6 (0.045) /2 um = 0.135 um

Capacità di diffusione:

CDB4 = CDB6 = Keq (CJ AD4 + CJSW PD4) = 1.05 fF

CDB5 = CSB4 = Keq (CJ AD5 + CJSW PD5) = 0.3923 fF

CDB1 = CDB2 = Keq (CJ AD1 + CJSW PD1) = 0.4723 fF

CDB3 = CSB2 = Keq (CJ AD3 + CJSW PD3) = 0.141 fF

Cgs (fF)

Miller

0.18

*

0.468

*

Capacità gate-drain e gate-source:

CGD4 = CGD5 = CGD6 = W4 COV = 0.036 fF (M5 è in cut-off, M4 e M6 in saturazione)

CGS4 = W4 COV + 2/3 COX W4L4 = 0.468 fF (M4 è in saturazione)

CGD1 = CGD3 = W1 COV = 0.018 fF (M1 e M3 sono in cut-off)

CGD2 = CGS2 = W2 COV + ½ COX W2L2 = 0.18 fF (M2 è in triodo)

La formula di Elmore risulta (fare tutti i passaggi):

Isat4 = Isat6 = 39 uA

R4 = R6 = ¾ VDD/Isat4 = 19.23 kΩ

Cp1 = Cdb5 + Cdb6 + Csb4 + Cgd5 + Cgs4 + 2 Cgd6 = 2.4106 fF

Cp2 = Cdb3 + Csb2 + Cgs2 + 2 Cgd3 = .0.498 fF

Cpz = Cdb4 + Cdb1 + Cdb2 + Cgd4 + Cgd1 + Cgd2 = 2.229 fF

CL = Cpz + CL’ = 3.229 fF

Il tempo di propagazione richiesto è (indicare la formula usata):

tp = 0.69 [Cp1 R6 + CL(R4+R6) + Cp2(R4+R6) ] = 0.69 R6 (Cp1+2CL+2Cp2) = 130.8 psec

e) Dimensionamento ottimo semplificato.

Il circuito è dimensionato in modo ottimo semplificato? SI

NO

(Se si sceglie NO, scrivere le dimensioni richieste per il dimensionamento ottimo semplificato

affianco a ciascun transistor nel riquadro (a) dove si è disegnato il circuito. Mettere le NUOVE

dimensioni fra parentesi.)

Esercizio 2 (STESSA TECNOLOGIA CMOS DELL’ESERCIZIO 1)

Lo schematico in Figura mostra una porta logica di tipo pass-transistor con l’aggiunta di un

meccanismo di level-restoring. Sapendo che tutti gli inverter sono dimensionati in modo

ottimo semplificato e che tutti i pass-transistor NMOS hanno W/L=3:

a) Determinare la funzione logica Z implementata dal circuito (tabella di verità ed

espressione algebrica).

b) Determinare la soglia logica degli inverter.

c) Dimensionare il PMOS M7 in modo da consentire al circuito di funzionare

correttamente. (Vanno bene risposte qualitative, purché giustificate da un

ragionamento).

SUGGERIMENTO: Perché il circuito funzioni gli NMOS devono riuscire a fare commutare

il primo inverter nonostante l’azione del level-restorer. Ricordare che le dimensioni

devono essere multipli della griglia.

a) Funzione logica

A

0

0

1

1

Z=A+B

B

0

1

0

1

Z

0

1

1

1

(OR)

Spiegazione:

M3-M4 e M5-M6 sono ovviamente degli inverter. Due inverter in cascata costituiscono un

buffer non invertente dunque il valore logico di Z coincide col valore logico di X. Basta allora

guardare, per ogni combinazione di ingressi, quale sia il valore di X. Ovviamente si considera

che il level-restorer (M7) non impedisca il corretto funzionamento dei pass-transistor (vedi

risposta (c) ).

Quando B=0 (righe 1 e 3) risulta B’=1 (M1 acceso) dunque passa il segnale A, viceversa

quando B=1 (righe 2 e 4) passa in uscita B stesso (M2 acceso) ossia proprio 1.

b) Soglia logica

r = (up COX (W/L)p VDSATp) / ( un COX (W/L)n VDSATn) = 1

VM = [ (VTH + VDSATn/2) + r (VDD-VTH - VDSATp/2)] / (1+r) = VDD / 2 = 0.5 V

Spiegazione:

Per calcolare la soglia logica si uguagliano le correnti del PMOS e del NMOS ipotizzando che

ingresso ed uscita siano uguali e pari a VM.

c) Dimensionamento di M7 (con passaggi)

Procedimento:

Come dice il testo, il problema è garantire che gli NMOS (i pass-transistor) riescano a fare

commutare l’inverter M3-M4 in modo da spegnere il level-restorer M7. Per fare questo bisogna

che la tensione al nodo X scenda al di sotto della soglia logica dell’inverter (a tal punto

l’inverter commuta, porta alto Y e spegne M7). Poiché tale soglia è VDD/2 (domanda

precedente), basta che lo NMOS sia più conduttivo del PMOS perché la tensione al nodo X

scenda al di sotto di VDD/2. Siccome lo NMOS non è a dimensione minima, basta che il PMOS

sia a dimensione minima (tanto più che la mobilità delle lacune è anche minore di quella degli

elettroni) perché lo NMOS risulti più conduttivo.

W7 = Wmin = 180nm

L7 = Lmin = 90nm

Questa è la risposta più semplice, ma sono corrette tutte le risposte che implicano:

Kp < Kn

=> (W/L)p < (unCOX / upCOX) (W/L)n

=> (W/L)p < 2 (W/L)n = 6

Esercizio 3 (STESSA TECNOLOGIA CMOS DELL’ESERCIZIO 1)

a) Implementare il circuito, in logica dinamica np-CMOS, corrispondente alla funzione

Z = [ (ABC)’ D ]’

b) Sapendo che la capacità parassita su cui vengono memorizzati i valori di PRECARICA sotto

forma di carica elettrica vale complessivamente 2fF e che le correnti di leakage (qualunque sia

la loro natura) valgono complessivamente 1pA, quale è la MASSIMA durata della fase di

VALUTAZIONE? (Ragionare esclusivamente sul primo livello di logica)

Suggerimenti per la risposta alla domanda b):

1) Ricordate che la soglia logica delle logiche dinamiche coincide con la tensione di soglia

del MOS (basta che la rete di pull-down si accenda a prescindere dall’eventuale pull-up, il

quale sarà comunque spento).

2) Ricordare che la corrente I di scarica o carica che scorre in un capacitore di valore C è

pari a I = C dV/dt . In questo caso tale corrente è costante e corrisponde alla corrente di

leakage.

3) Il problema potenziale è legato al fatto che dopo un certa quantità di tempo, la corrente di

leakage potrebbe scaricare inavvertitamente l’uscita del primo livello di logica.

a) Schematico del circuito (DARE UN NOME AI MOS)

b) Massima durata della fase di valutazione

Spiegare brevemente il ragionamento (con i passaggi):

Come dice il testo, il problema potenziale è legato alla possibile scarica involontaria

(dovuta al leakage) del nodo Z1. Tale scarica potrebbe accendere erroneamente M7

portando Z a VDD. Per evitare questo bisogna fare durare la fase di valutazione meno del

tempo necessario alla corrente di leakage per scaricare Z1 abbastanza da accendere M7.

Tale transistor (come dice ancora il testo) si accenderà appena la sua VSG sarà superiore

a VTH ossia non appena la tensione su Z1 scenderà dal valore VDD al valore VDD-VTH = 0.7.

La scarica è dovuta alla corrente costante I = Ileakage = 1pA, mentre la variazione di

tensione è ∆V=0.3V. Integrando la formula della corrente nel capacitore si ricava

facilmente:

tMAX = C∆V / Ileakage = 2 10-15 0.3 / 10-12 = 0.6 msec

ELETTRONICA DIGITALE

PRIMA PROVA IN ITINERE – A.A. 2008/2009 – 14 Novembre 2008

12345678901234567890123456789012345678901234567890123456789012345678901234567890123456781

01234567890123456789012345678901234567890123456789012345678901234567890123456789012345678

90123456789012345678901234567890123456789012345678901234567890123456789012345678901234567

89012345678901234567890123456789012345678901234567890123456789012345678901234567890123456

78901234567890123456789012345678901234567890123456789012345678901234567890123456789012345

67890123456789012345678901234567890123456789012345678901234567890123456789012345678901234

56789012345678901234567890123456789012345678901234567890123456789012345678901234567890123

45678901234567890123456789012345678901234567890123456789012345678901234567890123456789012

34567890123456789012345678901234567890123456789012345678901234567890123456789012345678901

23456789012345678901234567890123456789012345678901234567890123456789012345678901234567890

12345678901234567890123456789012345678901234567890123456789012345678901234567890123456789

01234567890123456789012345678901234567890123456789012345678901234567890123456789012345678

90123456789012345678901234567890123456789012345678901234567890123456789012345678901234567

89012345678901234567890123456789012345678901234567890123456789012345678901234567890123456

78901234567890123456789012345678901234567890123456789012345678901234567890123456789012345

67890123456789012345678901234567890123456789012345678901234567890123456789012345678901234

56789012345678901234567890123456789012345678901234567890123456789012345678901234567890123

45678901234567890123456789012345678901234567890123456789012345678901234567890123456789012

34567890123456789012345678901234567890123456789012345678901234567890123456789012345678901

23456789012345678901234567890123456789012345678901234567890123456789012345678901234567890

12345678901234567890123456789012345678901234567890123456789012345678901234567890123456789

01234567890123456789012345678901234567890123456789012345678901234567890123456789012345678

90123456789012345678901234567890123456789012345678901234567890123456789012345678901234567

89012345678901234567890123456789012345678901234567890123456789012345678901234567890123456

78901234567890123456789012345678901234567890123456789012345678901234567890123456789012345

67890123456789012345678901234567890123456789012345678901234567890123456789012345678901234

56789012345678901234567890123456789012345678901234567890123456789012345678901234567890123

45678901234567890123456789012345678901234567890123456789012345678901234567890123456789012

34567890123456789012345678901234567890123456789012345678901234567890123456789012345678901

23456789012345678901234567890123456789012345678901234567890123456789012345678901234567890

12345678901234567890123456789012345678901234567890123456789012345678901234567890123456789

01234567890123456789012345678901234567890123456789012345678901234567890123456789012345678

90123456789012345678901234567890123456789012345678901234567890123456789012345678901234567

89012345678901234567890123456789012345678901234567890123456789012345678901234567890123456

78901234567890123456789012345678901234567890123456789012345678901234567890123456789012345

67890123456789012345678901234567890123456789012345678901234567890123456789012345678901234

56789012345678901234567890123456789012345678901234567890123456789012345678901234567890123

45678901234567890123456789012345678901234567890123456789012345678901234567890123456789012

34567890123456789012345678901234567890123456789012345678901234567890123456789012345678901

39456789012345678901234567890123456789012345678901234567890123456789012345678901234567890

COGNOME:

MATRICOLA:

NOME:

POSTO:

Regole:

1) Non è consentito portare vicino al posto nulla che non siano penne, matite, gomma,

calcolatrice non programmabile. Giacconi, borse, appunti e cellulari devono essere

lasciati all’ingresso dell’aula.

2) Viene consegnato un gruppo di fogli pinzato di cui i primi contengono il testo e lo

spazio per riportare la soluzione, l’unica parte che verrà corretta è quella nei

riquadri appositamente indicati, il resto dei fogli deve essere consegnato ma non

verrà corretto.

3) Qualora la parte per la soluzione venisse pasticciata è possibile riscriverla su uno

degli altri fogli (nella stessa forma, non allungata) e fare un riferimento all'interno del

box soluzione. Il resto del compito ed il suo retro può essere pasticciato a piacere.

Non verranno dati altri fogli.

4) Se i fogli vengono staccati per errore, bisogna chiedere immediatamente che

vengano pinzati nuovamente.

5) Se un partecipante verrà trovato con fogli staccati, materiale non fornito dalla

commissione, od a scambiare informazioni con colleghi verrà allontanato e non gli

sarà permesso partecipare alle prove successive.

6) Il tempo per la soluzione è 3 ORE durante le quali non è possibile andare in bagno.

7) All’inizio della prova saranno dati 5 minuti per la lettura del testo dopo i quali si

potranno fare domande sul testo degli esercizi. Sarà consentito fare altre domande

solo ogni 30 minuti, restando al posto ed alzando la mano.

8) La prova è costituita da 3 esercizi.

Esercizio 1

Dato il layout in Figura ed un processo CMOS 90nm di parametri:

VDSAT

µ COX

COV

VTH

0.15 V

0.1 V

250 uA/V2

PMOS:

0.3 fF/um

VDD=1 V

2

NMOS: COX = 10 fF/um

0.15 V

0.1 V

500 uA/V2

0.3 fF/um

WMIN = 180nm, LMIN = 90nm

a)

b)

c)

d)

CJ

2 fF/um2

2 fF/um2

CJSW

2 fF/um

2 fF/um

Keq

0.5

0.5

Disegnare lo schematico del circuito implementato. Gli ingressi sono A, B, C e fn mentre l’uscita è Z.

Determinare la famiglia logica a cui appartiene il circuito.

Individuare la funzione logica implementata al nodo Z.

Calcolare il tempo di propagazione HL nel caso peggiore sapendo che il carico è un inverter static

CMOS a dimensionamento ottimo semplificato.

Layout (lato di 1 quadrato = 0.045um)

a) Schematico del circuito. Dare un nome a ciascun MOS. Il nome deve essere costituito

dalla lettera M, seguita da N o P a seconda del tipo di transistor e poi dal nome del

segnale che pilota il gate (es. MNA, MNB, MPC). Mettere a fianco a ciascun MOS le sue

dimensioni W/L.

b) Famiglia logica

LOGICA DINAMICA φn

c) Funzione logica

Espressione algebrica

Z = [(A+B)C]’

d) Tempo di propagazione HL

La commutazione di caso peggiore corrisponde alla combinazione:

A=1

B=0

C=1

fn = 0->1

spiegare brevemente il perché:

Commuta il transistor più lontano dall’uscita ed è necessario scaricare tutti i nodi

parassiti intermedi.

Parametri geometrici di interesse (calcolate e riportate SOLO quelli necessari).

NOME MOS

MNA

MNB

MNC

MNFN

MPFN

W (µm)

0.18

0.18

0.18

0.18

0.27

L (µm)

0.09

0.09

0.09

0.09

0.09

AD (µm2)

0.045

0.045

0.045

0.012

0.085

AS (µm2)

0.081

0.045

0.012

PD (µm)

0.45

0.45

0.45

0.135

0.9

PS (µm)

0.99

0.45

0.135

Capacità coinvolte (mettere un asterisco nella colonna Miller se per la capacità in questione

bisogna tenere conto dell’effetto Miller):

Capacità

Formula

Valore (fF)

CDB_MNA

Keq(CJ ADMNA +CJSW PDMNA)

0.5

CSB_MNA

Keq(CJ ASMNA +CJSW PSMNA)

1.07

CGD_MNA

COV WMNA

0.05

CGS_MNA

COV WMNA + 2/3 COX WMNAB LMNA

0.16

CDB_MNB

Keq(CJ ADMNB +CJSW PDMNB)

0.5

CSB_MNB

Keq(CJ ASMNB +CJSW PSMNB)

0.5

CGD_MNB

COV WMNB

0.05

CGS_MNB

COV WMNB

0.05

CDB_MNC

Keq(CJ ADMNC +CJSW PDMNC)

0.5

CSB_MNC

Keq(CJ ASMNC +CJSW PSMNC)

0.15

CGD_MNC

COV WMNC

0.05

CGS_MNC

COV WMNC + 2/3 COX WMNC LMNC

0.16

CDB_MNFN

Keq(CJ ADMNFN +CJSW PDMNFN)

0.15

COV WMNFN

0.05

Keq(CJ ADMPFN +CJSW PDMPFN)

0.99

COV WMPFN

0.08

Miller

CSB_MNFN

CGD_MNFN

*

CGS_MNFN

CDB_MPFN

CSB_MPFN

CGD_MPFN

CGS_MPFN

*

La formula di Elmore risulta (fare tutti i passaggi):

ReqMNA = ¾ VDD / [un COX (W/L)MNA VDSAT (VDD-VTH-VDSAT/2) ] = 9.4 kΩ

ReqMNB = ReqMNA

ReqMNC = ReqMNA

ReqMNFN = ReqMNA

ReqMPFN =

I nodi da considerare sono i seguenti (nome, capacità coinvolte, valore):

CN1 = CSBMNA + CSBMNB + CDBMNC + CGSMNA + CGSMNB + CGDMNC = 2.33 fF

CN2 = CSBMNC + CDBMNFN + CGSMNC + 2CGDMNFN = 0.56 fF

Il carico è un inverter a dimensionamento ottimo semplificato:

CL’ = COX (2WMIN + WMIN) LMIN = 0.49 fF

CZ = CL’ + CDBMPFN + CDBMNA + CDBMNB + CGDMNA + CGDMNB + 2CGDMPFN = 2.74 fF

Il tempo di propagazione richiesto è (indicare la formula usata):

tp = 0.69 ReqMNA (CN2 + 2CN1 + 3 CZ) = 87 psec

Da compito a compito cambiavano i valori numerici e la funzione implementata dal

layout, ma la metodologia di risoluzione era sempre la stessa.

Esercizio 2 (STESSA TECNOLOGIA CMOS DELL’ESERCIZIO 1)

Supponendo di poter realizzare solo transistor MOS che abbiano diffusioni di drain e source

realizzate con rettangoli con un lato pari alla W del MOS e l’altro lato pari a 270nm.

a) Si progetti un inverter static CMOS in modo che, quando il carico è costituito da un

altro inverter IDENTICO e la capacità del wire è trascurabile, il tempo di propagazione

sia minimo. Calcolare il tempo di propagazione risultante.

b) Si progetti un inverter static CMOS in modo che, quando il carico è costituito da un

altro inverter IDENTICO e la capacità del wire è pari a 0.5fF, il tempo di propagazione

sia minimo. Calcolare il tempo di propagazione risultante.

c) Si progetti un inverter static CMOS in modo ottimo semplificato, quando il carico è

costituito da un altro inverter IDENTICO e la capacità del wire è pari a 0.5f. Calcolare

il tempo di propagazione risultante.

a) Minimizzazione tP con CW=0. SPIEGARE TUTTI I PASSAGGI

Il dimensionamento dell’inverter CMOS in base alla minimizzazione del tempo di

propagazione (nel caso in cui debba pilotare un altro inverter identico) si basa sul fatto che

tutti i capacitori parassiti di un MOS sono proporzionali alla sua W. Prendendo, quindi, un

NMOS a dimensione minima ed un PMOS proporzionale a tale NMOS (attraverso un fattore

di proporzionalità beta) ed esprimendo il tempo di propagazione in funzione di beta e dei

capacitori parassiti del NMOS, si deve scegliere una valore di beta che renda minima tale

espressione. Si deve perciò ricavare la derivata, in funzione di beta, ed eguagliarla a 0. Si

veda, per i passaggi, la teoria (Modulo 4, pagg. 41 e seguenti).

Si ricava:

beta = √(r’(1+CW/(Cdn1+Cgn2))

dove

r’ = unCox / upCox = 2

e

Cdn1 = Keq (CJ Adn + CJSW PDn) = 0.77 fF

Cgn2 = COX Wn Ln = 0.16 fF

Si ottiene:

beta = 1.414

WP = 255 nm ≈ 270 nm (approssimato al multiplo di 45nm più vicino)

In questo caso:

Cgp2 = COX Wp Lp = 0.24 fF

Cdp1 = Keq (CJ Adp + CJSW PDp) = 0.88 fF

Idsatn = un COX(W/L)n VDSAT (VDD – VTH – VDSAT/2) = 80 uA

Idsatp = up COX (W/L)p VDSAT (VDD – VTH – VDSAT/2) = 60 uA

Reqn = ¾ VDD/Idsatn = 9.4 kΩ

Reqp = ¾ VDD/Idsatp = 12.5 kΩ

tP = 0.69 / 2 ( Reqn+ Reqp ) (Cdn1 + Cdp1 + Cgn2 + Cgp2) = 15 psec

(oppure, se si tiene conto anche dei capacitori Cgd

Cdn1 = Keq (CJ Adn + CJSW PDn) + 2 COV Wn = 0.88 fF

Cdp1 = Keq (CJ Adp + CJSW PDp) + 2 COV Wp = 1.04 fF

tP = 0.69 / 2 ( Reqn+ Reqp ) (Cdn1 + Cdp1 + Cgn2 + Cgp2) = 17 psec

)

b) Minimizzazione tP con CW=0.5fF. SPIEGARE TUTTI I PASSAGGI

Come visto prima:

beta = √(r’(1+CW/(Cdn1+Cgn2))

Cdn1 = Keq (CJ Adn + CJSW PDn) = 0.77 fF

Cgn2 = COX Wn Ln = 0.16 fF

Si ottiene:

beta = 1.75

WP = 315 nm (è un multiplo di 45nm)

In questo caso:

Cgp2 = COX Wp Lp = 0.28 fF