Circuiti Elettronici Digitali L-A

18 luglio 2006

Esercizio 1

1. Quanto vale il consumo di potenza dinamico di una porta logica alimentata a VDD = 2.5V, la cui

tensione di uscita VO commuta su una capacità di carico CL = 200fF tra VOL = 0.3V e VOH = 2.3V

ad una frequenza f = 500MHz?

2. Se in un invertitore CMOS viene raddoppiata la lunghezza di canale L dei due transistori, come si

modifica, in prima approssimazione

• la capacità di ingresso Cg

• le resistenze equivalenti Rn ed Rp

• la capacità intrinseca di uscita Co

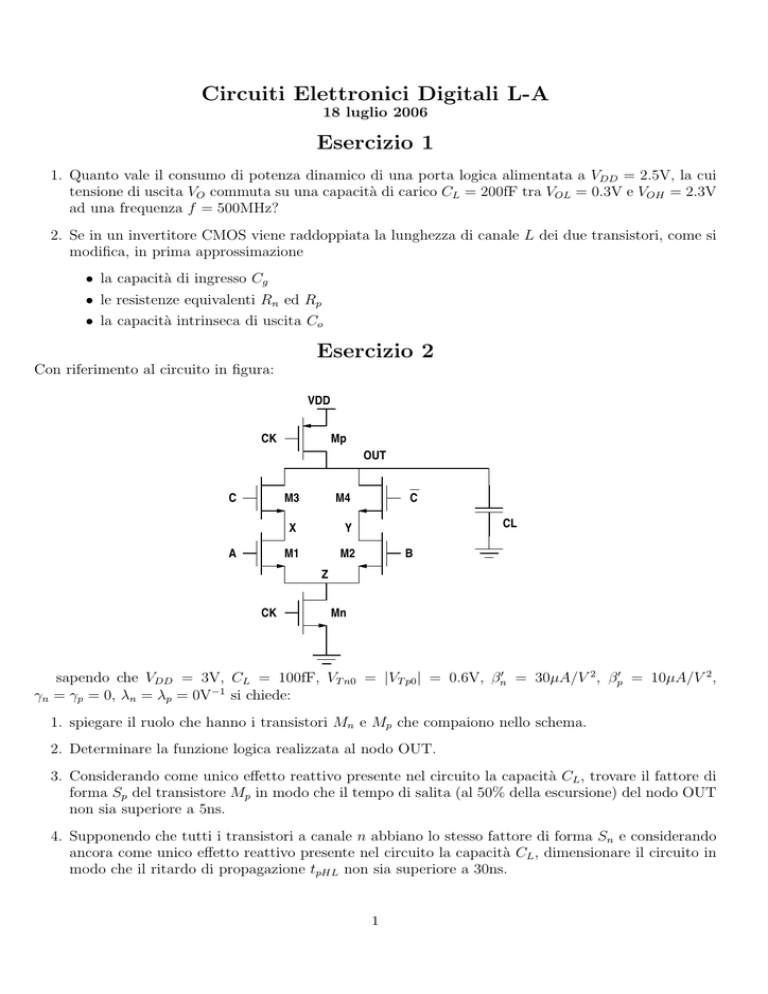

Esercizio 2

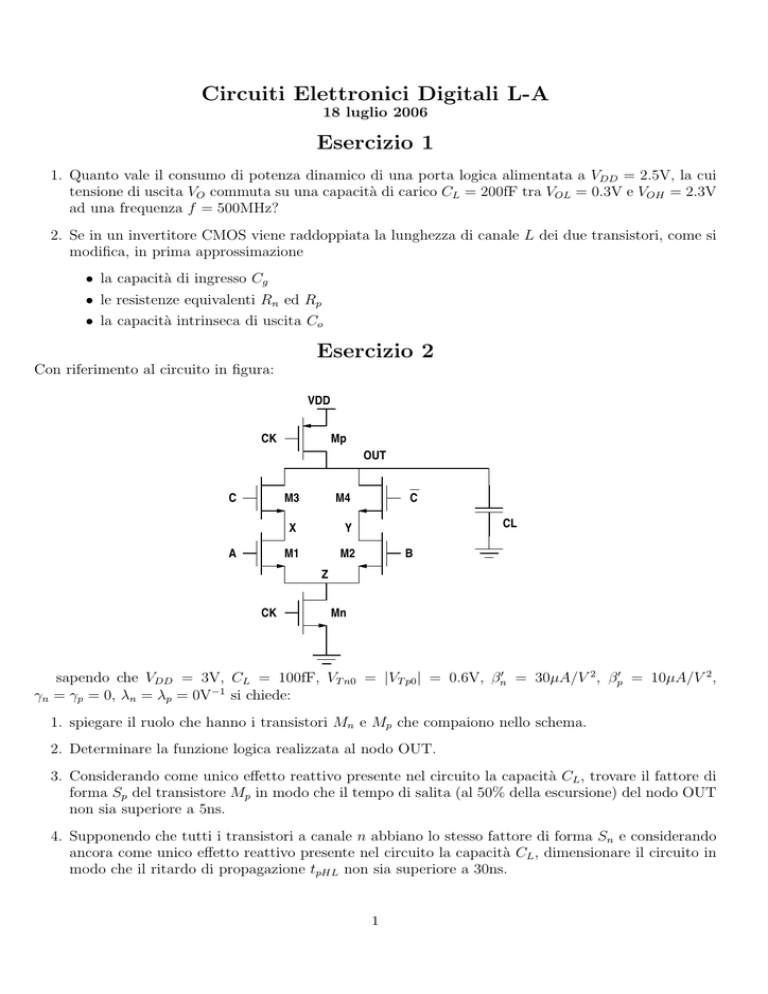

Con riferimento al circuito in figura:

VDD

CK

Mp

OUT

C

A

M3

M4

X

Y

M1

M2

C

CL

B

Z

CK

Mn

sapendo che VDD = 3V, CL = 100fF, VT n0 = |VT p0 | = 0.6V, βn0 = 30µA/V 2 , βp0 = 10µA/V 2 ,

γn = γp = 0, λn = λp = 0V−1 si chiede:

1. spiegare il ruolo che hanno i transistori Mn e Mp che compaiono nello schema.

2. Determinare la funzione logica realizzata al nodo OUT.

3. Considerando come unico effetto reattivo presente nel circuito la capacità CL , trovare il fattore di

forma Sp del transistore Mp in modo che il tempo di salita (al 50% della escursione) del nodo OUT

non sia superiore a 5ns.

4. Supponendo che tutti i transistori a canale n abbiano lo stesso fattore di forma Sn e considerando

ancora come unico effetto reattivo presente nel circuito la capacità CL , dimensionare il circuito in

modo che il ritardo di propagazione tpHL non sia superiore a 30ns.

1

5. Il circuito in esame può soffrire del problema della condivisione di carica (charge sharing) con

effetti sul nodo di uscita. Descrivere un caso in cui il problema si manifesta e indicare come varia

la tensione al nodo di uscita.

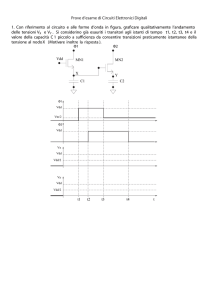

6. Completare il diagramma temporale in figura indicando chiaramente il valore delle tensioni raggiunte sui nodi OUT, X, Y, Z nelle diverse situazioni.

VDD

CK

0

VDD

A,B

0

VDD

C

0

VDD

OUT

0

VDD

X

0

VDD

Y

0

VDD

Z

0

7. Supponendo di avere a disposizione i segnali di ingresso A, B, C nella sola forma vera, disegnare lo

schema a pass transistor che realizza la stessa funzione logica OUT.

Esercizio 3

Spiegare dove e perchè viene impiegato il Sense Amplifier e cosa si intende per “sensibilità”.

Esercizio 4

1. Disegnare la struttura di una cella di memoria RAM a 1T.

2. Descrivere come avviene l’operazione di lettura del contenuto memorizzato.

3. Indicare quali vantaggi e quali svantaggi presenta la realizzazione della struttura di memoria a 1T

rispetto all’uso di una cella statica

2