24 Giugno 2009

cognome

nome

A

B

C

D

A

matricola

B

C

D

2 2 2 2

I

L

Totale

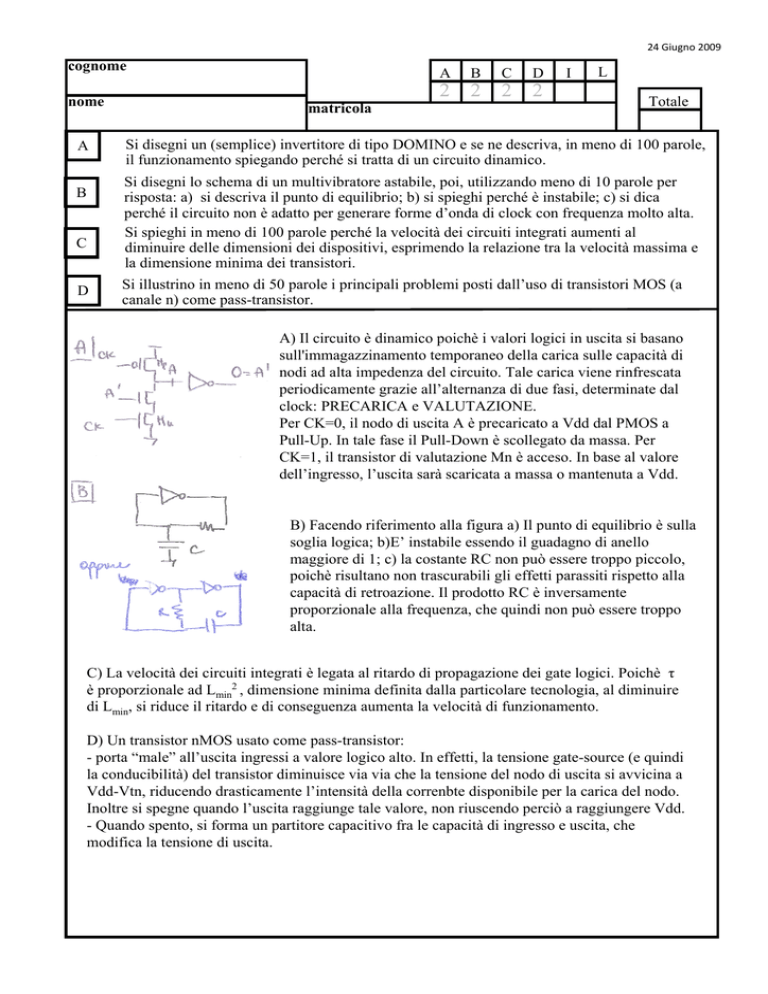

Si disegni un (semplice) invertitore di tipo DOMINO e se ne descriva, in meno di 100 parole,

il funzionamento spiegando perché si tratta di un circuito dinamico.

Si disegni lo schema di un multivibratore astabile, poi, utilizzando meno di 10 parole per

risposta: a) si descriva il punto di equilibrio; b) si spieghi perché è instabile; c) si dica

perché il circuito non è adatto per generare forme d’onda di clock con frequenza molto alta.

Si spieghi in meno di 100 parole perché la velocità dei circuiti integrati aumenti al

diminuire delle dimensioni dei dispositivi, esprimendo la relazione tra la velocità massima e

la dimensione minima dei transistori.

Si illustrino in meno di 50 parole i principali problemi posti dall’uso di transistori MOS (a

canale n) come pass-transistor.

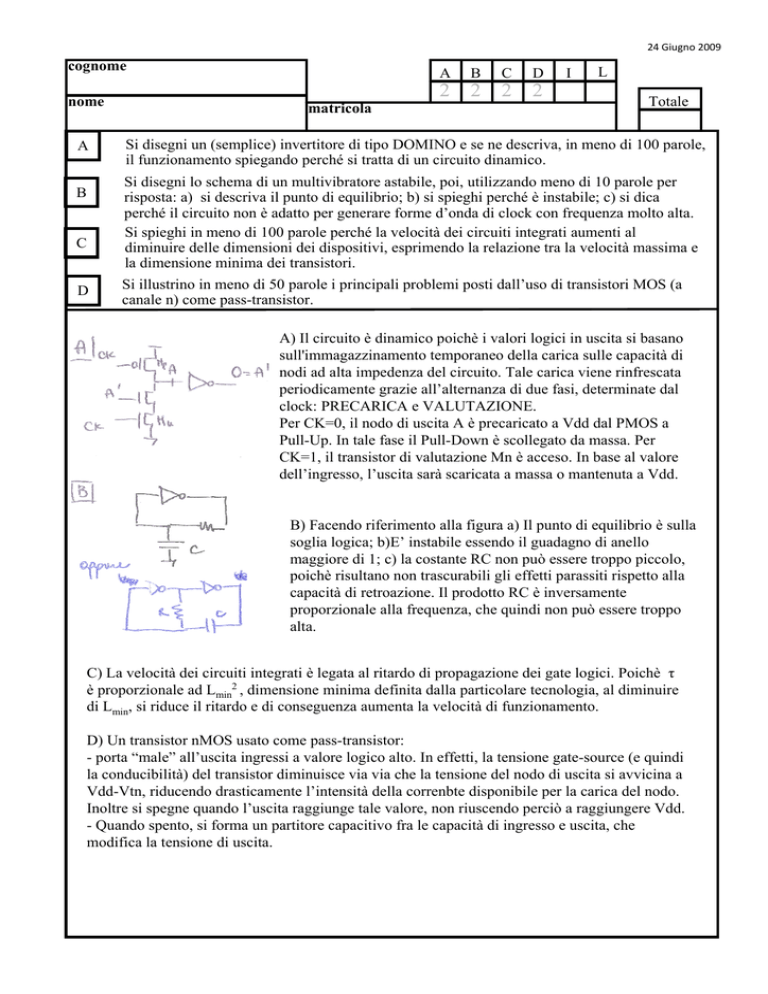

A) Il circuito è dinamico poichè i valori logici in uscita si basano

sull'immagazzinamento temporaneo della carica sulle capacità di

nodi ad alta impedenza del circuito. Tale carica viene rinfrescata

periodicamente grazie all’alternanza di due fasi, determinate dal

clock: PRECARICA e VALUTAZIONE.

Per CK=0, il nodo di uscita A è precaricato a Vdd dal PMOS a

Pull-Up. In tale fase il Pull-Down è scollegato da massa. Per

CK=1, il transistor di valutazione Mn è acceso. In base al valore

dell’ingresso, l’uscita sarà scaricata a massa o mantenuta a Vdd.

B) Facendo riferimento alla figura a) Il punto di equilibrio è sulla

soglia logica; b)E’ instabile essendo il guadagno di anello

maggiore di 1; c) la costante RC non può essere troppo piccolo,

poichè risultano non trascurabili gli effetti parassiti rispetto alla

capacità di retroazione. Il prodotto RC è inversamente

proporzionale alla frequenza, che quindi non può essere troppo

alta.

C) La velocità dei circuiti integrati è legata al ritardo di propagazione dei gate logici. Poichè τ

è proporzionale ad Lmin2 , dimensione minima definita dalla particolare tecnologia, al diminuire

di Lmin, si riduce il ritardo e di conseguenza aumenta la velocità di funzionamento.

D) Un transistor nMOS usato come pass-transistor:

- porta “male” all’uscita ingressi a valore logico alto. In effetti, la tensione gate-source (e quindi

la conducibilità) del transistor diminuisce via via che la tensione del nodo di uscita si avvicina a

Vdd-Vtn, riducendo drasticamente l’intensità della correnbte disponibile per la carica del nodo.

Inoltre si spegne quando l’uscita raggiunge tale valore, non riuscendo perciò a raggiungere Vdd.

- Quando spento, si forma un partitore capacitivo fra le capacità di ingresso e uscita, che

modifica la tensione di uscita.

I1

I

1)

2)

3)

4)

5)

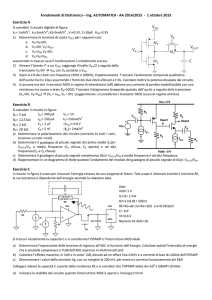

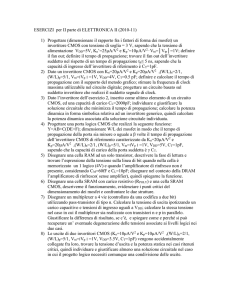

f = AC + BC + AD

I3

I4

I5

2 2 2 2 2

Totale

Si realizzi la funzione logica f in logica FCMOS

Si dimensioni il gate FCMOS in modo da pilotare una capacità di carico di 500fF con un

ritardo al 90% sia di salita che di discesa di 1ns.

Si realizzi la funzione logica f in logica DOMINO

Si dimensioni l’invertitore di uscita in modo che il suo ritardo (al 50%) nel pilotare una

capacità di carico 1pF sia 50 psec per i fronti di salita e per i fronti di discesa. (Si applichi il

metodo della resistenza equivalente).

Si calcoli la capacità di ingresso dell’invertitore presente nella realizzazione DOMINO e si

dimensionino le reti di pull-up e pull-down del gate dinamico in modo da avere un ritardo

(al 50%) di 50ps nel pilotare l’invertitore d’uscita. (Si applichi il metodo della resistenza

equivalente.)

L1 L2 L3 L4 L5

L

3 3 3 3 ☺

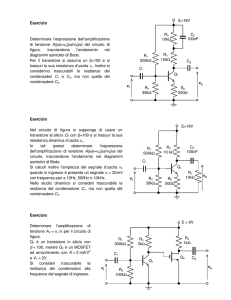

Vdd

L2=0.3mm

S=80

B

L1=0.2mm

A

I2

X

O

L3=0.1mm

SN=10

SP=20

C

S=40

Totale

Con riferimento al circuito in figura, usando modelli a π per le

interconnessioni, con cL=0.5 fF/µm, rL=2 Ω/µm

1. Si determini il ritardo con cui un fronte istantaneo di salita in A

raggiunge il punto B

2. Si determini il ritardo con cui un fronte istantaneo di salita in A

raggiunge il punto C

3. Si calcoli il valore a regime della tensione sul nodo O nei seguenti 3

casi: BC=01, BC=10; BC=11.

4. Si indichi il caso peggiore del ritardo di propagazione tra il nodo A

ed O

5. (Punti extra) Si tracci la caratteristica statica del gate composto dai

due PMOS, in cui VC = -10V e VB Є[0, Vdd]. Se ne calcoli il

consumo di potenza statico di caso peggiore.

PARAMETRI TECNOLOGICI (Vdd

= 3.3 V)

N-channel

P-channel

VT0

0,7 V

-0,7V

β’

100µA/V2

50µA/V2

Cox

3,45 fF/ µm2

3,45 fF/ µm2

Lmin

0,35 µm

0,35 µm

λ,γ

0

0

Req_rif(Vgs=|Vdd|, 50%, Srif=1)

2,2 KΩ

4,4 KΩ

Req_rif(Vgs=|Vdd|, 90%, Srif=1)

5,39 KΩ

10,78 KΩ