ESERCIZI per II parte di ELETTRONICA II (2010-11)

1) Progettare (dimensionare il rapporto fra i fattori di forma dei mosfet) un

invertitore CMOS con tensione di soglia = 3 V, sapendo che la tensione di

alimentazione VDD=5V, Kn’=25μA/V2 e Kp’=10μA/V2 , Vtn=│Vtp│=1V; definire

il fan out; definire il tempo di propagazione; trovare il fan out dell’invertitore

suddetto nel rispetto di un tempo di propagazione tp≤ 5 ns, sapendo che la

capacità di ingresso dell’invertitore di riferimento è CT=1pF.

2) Dato un invertitore CMOS con Kn=20μA/V2 e Kp=20μA/V2 ,(W/L)n=2/1,

(W/L)p=5/1, Vtn=׀Vp = ׀1V, VDD=4V, CT=0.5 pF; definire e calcolare il tempo di

propagazione con il supporto del metodo grafico; stimare la frequenza di clock

massima utilizzabile nel circuito digitale; progettare un circuito basato sul

suddetto invertitore che realizzi il suddetto segnale di clock.

3) Dato l’invertitore dell’esercizio 2, inserito come ultimo elemento di un circuito

CMOS, ed una capacità di carico CL=2000pF; individuare e giustificare la

soluzione circuitale che minimizza il tempo di propagazione; calcolare la potenza

dinamica in forma simbolica relativa ad un invertitore generico, quindi calcolare

la potenza dinamica associata alla soluzione circuitale individuata.

4) Progettare una porta logica CMOS che realizzi la seguente funzione:

Y=AB+C(DE+F); dimensionare W/L dei mosfet in modo che il tempo di

propagazione della porta sia minore o uguale a β volte il tempo di propagazione

dell’invertitore CMOS di riferimento caratterizzato da Kn=20μA/V2 e

Kp=20μA/V2 ,(W/L)n=2/1, (W/L)p=5/1, Vtn=׀Vp = ׀1V, VDD=5V, CT=1pF,

sapendo che la capacità di carico della porta suddetta è γ CT.

5) Disegnare una cella RAM ad un solo transistor, descrivere la fase di lettura e

trovare l’espressione della tensione sulla linea di bit quando nella cella è

memorizzato un 1 logico (4V) e quando l’amplificatore di rinfresco non è

presente, considerando CM=60fF e CL=10pF; disegnare nel contesto della DRAM

l’amplificatore di rinfresco( sense amplifier), quindi spiegarne la funzione.

6) Disegnare una cella SRAM con carico resistivo (RPOLY) e una cella SRAM

CMOS, descriverne il funzionamento, evidenziare i punti critici del

dimensionamento dei mosfet e confrontare le due strutture.

7) Disegnare un multiplexer a 4 vie (controllato da una codifica a due bit)

utilizzando pass-transistor di tipo n. Calcolare la tensione di uscita ipotizzando un

carico capacitivo e tensioni di ingresso uguali a VDD; calcolare la stessa tensione

nel caso in cui il multiplexer sia realizzato con transistori n e p in parallelo.

Giustificare la differenza di risultato, se c’è, e spiegare come e perché si può

recuperare un’ eventuale degenerazione delle tensioni associate ai livelli logici nei

due casi.

8) Le uscite di due invertitori CMOS (Kn=10μA/V2 e Kp=10μA/V2 ,(W/L)n=2/1,

(W/L)p=5/1, Vtn=׀Vp = ׀1V, VDD=3.5V, CT=1pF) vengono accidentalmente

collegate fra loro, trovare la tensione d’uscita e la potenza statica nei casi ritenuti

critici, quindi individuare e giustificare almeno una soluzione circuitale nel caso

in cui il progetto logico necessiti comunque una condivisione delle uscite.

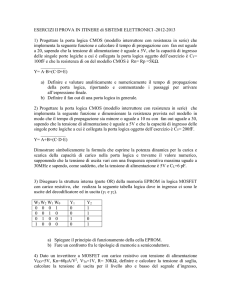

9) Disegnare la parte OR di una memoria EPROM che realizzi la seguente tabella e

descrivere la struttura della singola cella (FAMOS) e le modalità di

programmazione:

a2,a1,a0

000

001

010

011

100

101

110

111

Y0

0

0

0

0

0

0

1

0

Y1

1

0

1

0

1

0

0

1

Y2

1

1

0

0

0

1

1

0

Y3

0

0

0

0

0

0

0

1