Università di Bologna, Facoltà di Ingegneria

Corso di Laurea in Ingegneria Elettronica

Esercitazioni di E LETTRONICA L-C

Anno Accademico 2001/2002

Esercitazione N. 4

7 giugno 2002

Questa esercitazione prevede la progettazione e la simulazione di un multivibratore astabile, basato sull’accoppiamento di un condensatore con un resistore anomalo a caratteristica S. Al fine di

comprendere meglio il funzionamento di questo tipo di circuiti l’esercitazione è divisa in due parti.

Nella prima, il resistore anomalo viene sintetizzato con un circuito ad amplificatore operazionale;

nella seconda si sfrutta una cella differenziale a transistor.

La prova di laboratorio ha i seguenti obiettivi:

1. Approfondire la propria conoscenza del simulatore circuitale, ed in particolare per quanto

riguarda l’uso del front-end per tracciare il ciclo limite di circuiti oscillanti.

2. Verificare i concetti appresi a lezione sul progetto degli astabili.

3. Approfondire i limiti dei circuiti ad operazionale e alcune delle problematiche che emergono

nel progetto di dispositivi realizzati a transistor.

Progetto dell’astabile

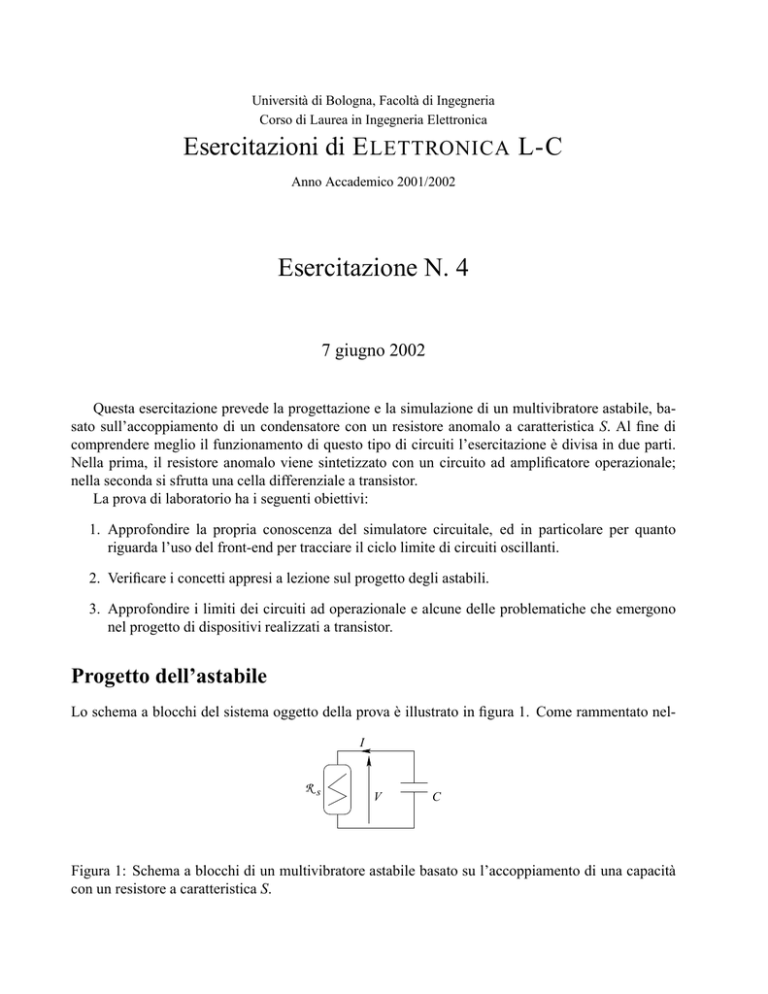

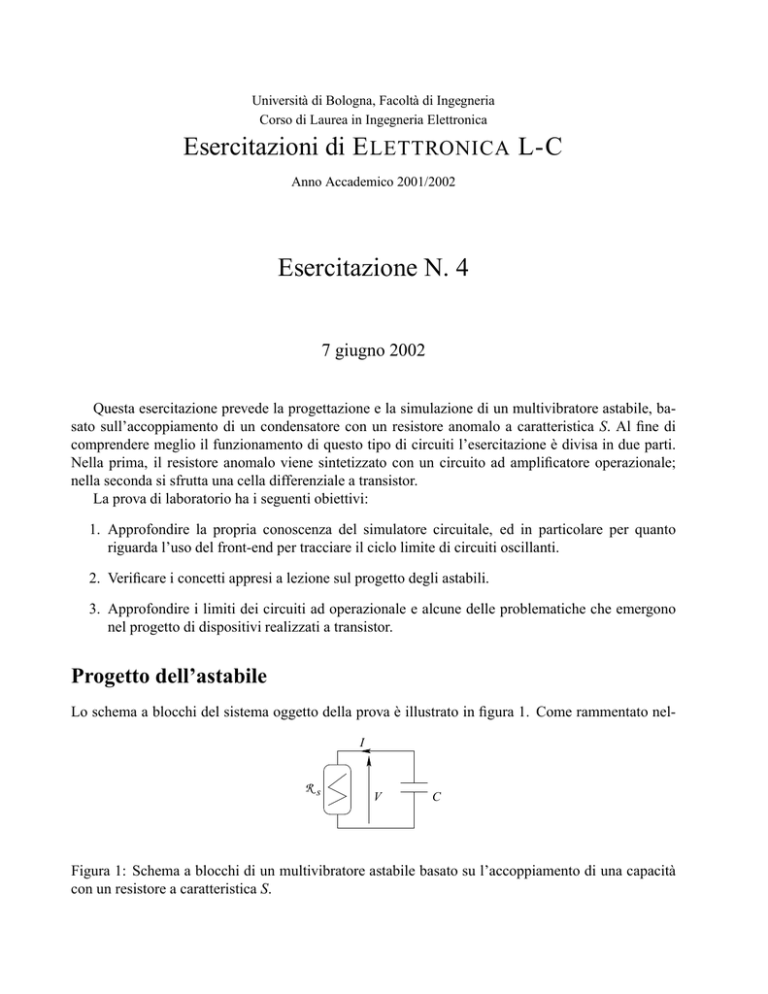

Lo schema a blocchi del sistema oggetto della prova è illustrato in figura 1. Come rammentato nelI

s

V

C

Figura 1: Schema a blocchi di un multivibratore astabile basato su l’accoppiamento di una capacità

con un resistore a caratteristica S.

l’introduzione, nella prima parte dell’esperienza il resistore anomalo

viene realizzato impiegando

un amplificatore operazionale, mentre nella seconda viene impiegato un circuito basato direttamente

su transistor bipolari e MOS.

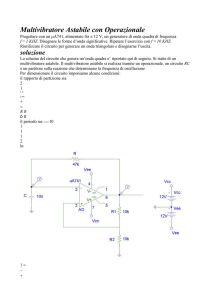

Realizzazione ad amplificatore operazionale

Per il resistore

si utilizza lo schema ad amplificatore operazionale, in figura 2, che fornisce un

resistore anomalo in cui nessuno dei due terminali coincide con la massa.

I generatori di polarizzazione

e

, non rigorosamente indispensabili, forniscono due ulteriori

gradi di libertà nella progettazione del circuito. Il circuito operazionale di figura 2 è descritto mediante

il seguente modello beavhioural:

V

I

+

−

Vout

RB

R

RA

+ Vb1 + Vb2

−

−

Figura 2: Schema elettrico del bipolo anomalo a caratteristica S realizzato ad operazionale.

.SUBCKT OPAMP INP INN OUT PARAMS: VUMP=10 VUMN=-10 AD=400K

+ WT=62.8 SR=5Meg

.PARAM IMAX=10M GM={AD*WT*IMAX/SR} CAP={IMAX/SR} ERRE={1/WT/CAP}

.PARAM FS=1K

RINN INN 0 10G

RINP INP 0 10G

G1 0 X VALUE={MAX(MIN(GM*V(INP,INN),IMAX),-IMAX)}

GZ1 X 0 VALUE={MAX(V(X)-VUMP,0)*IMAX/(VUMP-VUMN)*FS}

GZ2 0 X VALUE={MAX(VUMN-V(X),0)*IMAX/(VUMP-VUMN)*FS}

C1 X 0 {CAP}

R1 X 0 {ERRE}

E1 OUT 0 X 0 1

.ENDS

Progettazione del multivibratore astabile

Assumendo

si dimensionino

, , affinché siano soddisfatti i seguenti requisiti:

2

( ) ! +*-,/ . !#". % $'& del ciclo di isteresi pari a metà dell’escursione della tensione di

Duty-cycle 01324265 .

Massima corrente ( , ( ! 789,/. .

Il primi due punti delle condizioni di progetto permettono di dimensionare i resistori # e , mentre

il secondo punto permette di determinare il valore della tensione . Con questo ultimo punto siamo

in grado di dimensionare il resistore .

Al termine di questo flusso di progetto si è in possesso dei valori di , # , , e e quindi si

dispone del bipolo anomalo a caratteristica : . Si usi ora il simulatore circuitale Spice per verificare

Ampiezza

uscita e

che il circuito si comporta secondo le specifiche.

<-= (?>

1. Si utilizzi il simulatore Spice come aiuto per disegnare la caratteristica corrente-tensione (

) del bipolo , verificando che corrisponda a quella teorica.

Per realizzare questa analisi si deve tenere bene a mente che:

( = A>

Il bipolo deve essere comandato in corrente in quanto

è

.

= (@>

;

è una funzione, mentre non lo

= (?>

Quando si dovranno analizzare i risultati si dovrà disegnare la caratteristica

ponendo

sulle ascisse la tensione e sulle ordinate la corrente . Per fare questo si deve agire dal

front-end di Spice come segue:

Selezionare Axis Setting... dal menu Plot, aprire la tendina etichettata come X Axis e

scegliere la funzione Axis Variable.... Per porre sull’asse delle ascisse la tensione indicare la seguente Trace Expression V(INP,OUT) (dove V(INP) è la tensione sul morsetto

positivo dell’amplificatore operazionale e V(OUT) è la corrispondente tensione di uscita.

La traccia della corrente è la stessa che attraversa il resistore che può essere inserita

“cliccando” sul pulsante Add Trace e selezionandola dall’elenco delle traccie disponibili.

(

(

2. Verificare come varia la caratteristica corrente-tensione del bipolo

per i seguenti valori di

tensione di riferimento

, evidenziando tutti i valori per cui il

circuito funziona come astabile.

B C "D@EF"HGIEF"#J?E EKJLEMGIEND?O

<QP J-RLST

Una volta testato il circuito che permette di generare la resistenza negativa si completi il progetto

, ricavando il

dell’astabile imponendo i requisiti sulla frequenza del segnale di uscita

corrispondente valore di . Si analizzi ora il circuito, mediante il simulatore Spice, verificando:

U

3. La frequenza di oscillazione simulata e la si confronti con quella di progetto.

4. Il valore di duty-cycle dell’astabile.

5. Il valore dell’ampiezza di oscillazione.

6. L’andamento delle tensioni ai capi dei nodi di ingresso dell’amplificatore operazionale e della

tensione e corrente sul condensatore .

U

7. Utilizzando il front-end di Spice, come spiegato in precedenza, si tracci il ciclo limite

dell’oscillatore astabile.

3

(?V4

Si deve disegnare il ciclo limite sul piano

, ponendo quindi sull’asse delle ascisse

la tensione ai capi del condensatore e coerentemente sulle ordinare la corrente che lo

attraversa.

8. Se il dimensionamento dei componenti è corretto si noteranno i due tratti verticali, che corrispondono allo “scatto” del multivibratore e i due tratti obliqui, che corrispondono alla scarica

ed alla carica di . Si determini in che senso è percorso il ciclo limite.

U

WXKY

9. È altresı̀ da notare un tratto della funzione

non appartenente al ciclo limite e che viene

percorso una sola volta, si provi a dare una giustificazione a tale fenomeno.

Una volta testato il corretto funzionamento dell’oscillatore astabile si procederà ad esaminare il circuito valutandone i limiti funzionali. Si agisca sui componenti del circuito, imponendo

e

, si studi il circuito verificando:

UZ*[49\]

9-^

10. La frequenza di oscillazione simulata e la si confronti con quella teorica che si dovrebbe

riscontrare per tale valore di capacità.

11. Il duty-cycle dell’astabile.

12. Il valore dell’ampiezza di oscillazione.

13. Utilizzando il front-end di Spice si calcoli il valore di slew-rate e si verifichi se corrisponde a

quello imposto dal modello di amplificatore operazionale.

14. L’andamento delle tensioni ai nodi di ingresso dell’amplificatore operazionale e della tensione

e corrente sul condensatore .

U

15. Utilizzando il front-end di Spice, come spiegato in precedenza, si tracci il ciclo limite

dell’oscillatore astabile.

Realizzazione a transistor

Per superare i limiti di banda dell’operazionale, in questa parte dell’esperienza di realizzerà uno

schema equivalente dell’astabile di figura 1 utilizzando però la cella differenziale di figura 3. Sulla

base dell’esperienza precedente si impone come specifica di progetto che:

I transistor BJT abbiano una guadagno statico di corrente

trascurabile.

_` J 4

ed effetto Early

I Ybac " 7d^ , lunghezza ef 7%gh,

kmln J 9gj.Vm^ La temperatura sia di op;7Qq[r (I st J *-,/^ ) ed ( P u

789,v. .

i ;7F49gj,

I transistor MOS abbiano tensione di soglia

e

.

, larghezza

Progettazione del multivibratore astabile

Al fine di poter esaminare e progettare il circuito si dovranno introdurre alcune approssimazioni per

quanto riguarda il carico sull’uscita della cella differenziale, affinché questa possa essere assimilata

all’operazionale di figura 2 e si possano utilizzare le medesime formule per il dimensionamento dei

componenti passivi. Tale approssimazione si traduce nell’imporre

. In questa maniera si

ottengono due notevoli semplificazioni:

#w J 4yx

4

Vcc =10V

Mp1

Mp2

Q1

Vout

Q2

Rz

V+

V−

I0

Vee =−10V

Figura 3: Schema elettrico della cella differenziale realizzata a transistor BJT e MOS.

# E Scegliendo tutte le altre resistenze (

ed ) di almeno due ordini di grandezza superiori

rispetto a

(ad esempio

), nei riguardi del resto del circuito la coppia differenziale

appare come un amplificatore a bassa resistenza di uscita, una specie di operazionale a basso

guadagno.

78 R x

#w

( P ;789,v.

<-= {|>} <-= ~ " > ) della cella differenziale,

16. Si tracci la caratteristica statica ( WXKYz

evidenziando la massima escursione di WXKY .

Con l’aiuto del simulatore si analizzi il circuito di figura 3 per

17. Esistono dei vincoli sulla tensione di modo comune, affinché sia possibile avere la massima

escursione?

18. Si determini il potenziale

P

affinchè il transistor

1

non lavori mai in regione di saturazione.

19. Si determini il guadagno della cella differenziale.

Ricalcando l’esempio precedente, in questa seconda parte dell’esperienza si progetterà e si realizzarà

l’astabile impiegando il bipolo anomalo a caratteristica S realizzato a transistor. A tale scopo lo

schema circuitale che si considerà è quello di figura 4.

20. Si determini il massimo valore di

saturazione.

affinché il transistor

1

non lavori mai in regione di

# , , affinché siano soddisfatti i seguenti requisiti:

Ampiezza del ciclo di isteresi pari a metà dell’escursione della tensione di uscita.

( ) q[49gj. , per " *^ .

Si progettino

5

Vcc =10V

I

V

Mp1

Vout

Mp2

RB

Q1

Q2

RA

R

I0

+ V

− b1

Vee =−10V

Rz

Cz

+

− Vb2

Figura 4: Schema elettrico del multivibratore astabile ottenuto mediante il bipolo anomalo a

caratteristica S realizzato a transistor.

Duty-cylce

01324265

.

( ( ! 32*ygh.

Frequenza di oscillazione <QP ;7F4 ?R SHT .

Imposizione della massima corrente ,

.

Una volta in possesso di tutti i valori dei componenti del circuito si proceda all’analisi del suddetto.

Come fatto in precedenza si esaminerà prima il solo bipolo S dando risposta ai seguenti quesiti:

<-= (?>

21. Si utilizzi il simulatore Spice come aiuto per disegnare la caratteristica corrente-tensione (

) del bipolo , valutando le differenze rispetto a quella teorica.

;

22. Verificare come varia la caratteristica per i seguenti valori di tensione di rifermento

, evidenziando tutti i valori per cui il circuito funziona come astabile.

C "#D?EF"G@EF"JLE EKJ?EGIEND?O

I prossimo passo è quello di considerare il circuito dell’astabile ed esaminarlo con l’aiuto del simulatore Spice dovendo considerare, se necessario, eventuali artifici per far si che la simulazione vada a

buon fine. Purtroppo a causa delle diverse costanti temporali del bipolo anomalo

e del circuito , che determina la frequenza di oscillazione dell’astabile, il simulatore potrebbe non trovare alcuna

soluzione al problema per problemi di convergenza (These devices failed to converge...). Una possibile soluzione al problema ‘e l’introduzione di un polo all’interno del bipolo anomalo

mediante

l’introduzione del condensatore

ai capi della resistenza .

Si consideri ora il circuito dell’astabile e lo si esamini con l’aiuto del simulatore Spice dando risposta

ai seguenti quesiti:

U

Uw7\]

#w

6

23. Si rilevi a frequenza di oscillazione simulata e la si confronti con quella di progetto e si cerchi

di giustificare perchè le due non concordano.

24. Il duty-cycle dell’astabile.

25. L’andamento delle tensioni ai capi dei nodi di ingresso dell’amplificatore operazionale e della

tensione e corrente sul condensatore .

U

26. Utilizzando il front-end di Spice, come spiegato in precedenza, si tracci il ciclo limite

dell’oscillatore.

*4 R x

<mP 784 RLST

U

27. Al fine di valutare i limiti del circuito si modifichi il valore di

e si calcoli per

avere

. Si esamini il circuito con l’aiuto del simulatore Spice e si dica perchè

questa volta il valore della frequenza di oscillazione diverge più di prima, rispetto a quello

teorico.

7

A cura di: Ing. A. Leonardi,

Ing. S. Callegari.

PRIMA NETLIST

Esperienza numero 4

* Multivibratore astabile realizzato con amplificatore

* operazionale

* L’OpAmp è realizzato mediante schematizzazione a

* modello Callegari ad un polo

* Senza polo si avrebbero problemi di convergenza dovuti

* all’enorme differenza

* tra le costanti di tempo dell’OpAmp e del circuito R-C

* Parametri ambientali di simulazione

.TEMP 17

.OPTION TNOM=17 RELTOL=1e-6

* Modello di un amplificatore operazionale

.SUBCKT OPAMP INP INN OUT PARAMS: VUMP=10 VUMN=-10 AD=400K WT=62.8 SR=5Meg

.PARAM IMAX=10M GM={AD*WT*IMAX/SR} CAP={IMAX/SR} ERRE={1/WT/CAP}

.PARAM FS=1K

RINN INN 0 10G

RINP INP 0 10G

G1 0 X VALUE={MAX(MIN(GM*V(INP,INN),IMAX),-IMAX)}

GZ1 X 0 VALUE={MAX(V(X)-VUMP,0)*IMAX/(VUMP-VUMN)*FS}

GZ2 0 X VALUE={MAX(VUMN-V(X),0)*IMAX/(VUMP-VUMN)*FS}

C1 X 0 {CAP}

R1 X 0 {ERRE}

E1 OUT 0 X 0 1

.ENDS

* Un modello di amplificatore operazionale

*.SUBCKT OPAMP INP INN OUT PARAMS: VUMP=10 VUMN=-10 AD=400K

*E1 OUT 0 value={min(max(ad*v(inp,inn),vumn),vump)}

*.ENDS

* NETLIST

* Progettare il circuito affinché si abbia una frequenza di

* oscillazione di 2kHz e duty-cycle 33%

* ed una corrente massima, nella condizione peggiore, sulla rete

* di retroazione negativa di 10mA.

* Progettare l’astabile affinché sulla rete di retroazione

* positiva si abbia una corrente

* massima dell’ordine dei mA --> Ipos=(Vout-Vref)/(R1+R2), si

* può considerare R1=R2=1k

* DALLA SOLUZIONE DEL PROBLEMA SI OTTIENE

X1 Ninp Ninn Nout OPAMP

RB Nout Ninn 1k

RA Ninn Nvb2 1k

8

Vb2 Nvb2 0 DC 0

Cosc Nout Ninp 124n

Rosc Ninp Nvb1 1767

Vb1 Nvb1 0 DC -2.6759

* Simulazione

.PROBE

.TRAN 100n 5m 0 100n

.END

SECONDA NETLIST

Esperienza 4

*f0=100kHz, duty cycle 33%

.OPTIONS reltol 1E-6

.MODEL PMOSX PMOS vto=-1 kp=20u

.MODEL NPNX NPN bf=200

Vdd dd 0 DC 10

Vss ss 0 DC -10

Qsx OUT INN E NPNX

Qdx N1 INP E NPNX

Mpsx N1 N1 dd dd PMOSX L=1u W=100u

MPdx OUT N1 dd dd PMOSX L=1u W=100u

I0 E ss DC 10m

Rz OUT 0 200

Cz OUT 0 1p

Vb2 Nvb2 0 DC -5

Vb1 Nvb1 0 DC -3.035

RA

RB

C1

R1

inn

out

out

inp

Nvb2 5k

inn 5k

inp 395.7p IC=100m

Nvb1 10100

.probe

.tran 1000n 100u 0 1000n

.end

9