DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

Marco D. Santambrogio – [email protected]

Ver. aggiornata al 7 Marzo 2012

1

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

• Modello concettuale, funzionale e architetturale di un calcolatore

• Codifica delle istruzioni e dei dati per l’esecuzione automatica

• Architettura dei calcolatori

• Struttura e principi di funzionamento

▶ della CPU

▶ della memoria centrale

2

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

3

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

• Flessibilità nel calcolo,

▶ architettura non specializzata per un solo tipo di utilizzo ma adatta a svolgere diversi compiti;

• Modularità della struttura

▶ a ogni componente viene demandato lo svolgimento di una funzione specifica del sistema

complessivo;

• Scalabilità dei componenti

▶ ognuno dei quali può essere sostituito con uno funzionalmente equivalente ma in grado di

fornire prestazioni migliori;

• Standardizzazione dei componenti

▶ per facilitarne la sostituzione in caso di malfunzionamenti;

• Abbattimento dei costi

▶ grazie alla produzione su vasta scala dei componenti;

• Semplicità di installazione e di esercizio del sistema

• Disponibilità di applicazioni a basso prezzo di vendita

4

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

1.

Elaborazione

2.

Memorizzazione

Interconnessione

3.

Comunicazione

(interfaccia)

5

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

1.

Elaborazione

Unità Centrale di

Elaborazione

Collegamenti

(BUS/Cavi)

2.

Memoria

Memorizzazione

Memoria

Elettronica

Magnetica

Interconnessione

3.

Comunicazione

(interfaccia)

Periferiche

6

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

Memoria di

massa

PC

Video/tastiera

(terminale)

ALU

Registri

CPU

Memoria

Interfaccia di I/O

Interfaccia di I/O

dati

BUS

indirizzi

controllo

7

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

Connettori per

schede di I/O

aggiuntive

Socket per

la CPU

Connettori per la

memoria

Connettori per

dischi fissi

8

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

Semplicità

▶

un’unica linea di connessione costi ridotti di produzione

Estendibilità

▶

aggiunta di nuovi dispositivi molto semplice

Standardizzabilità

▶

regole per la comunicazione da parte di dispositivi diversi

Lentezza

▶

utilizzo in mutua esclusione del bus

Limitatà capacità

▶

al crescere del numero di dispositivi collegati

Sovraccarico del processore (CPU)

▶

perchè funge da master sul controllo del bus

9

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

RAM

CPU

Scheda madre

(motherboard)

Bus dati

Bus indirizzi

Bus di controllo

Interfacce

di I/O

Interfaccia di I/O

Tastiera e mouse

Altoparlanti

Interfacce

di I/O

Memoria di massa

Schermo

10

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

• Partecipa al progetto ENIAC

• Due intuizioni fondamentali:

▶ memorizzare i programmi in forma digitale nella stessa memoria dei dati

per rendere più semplice la programmazione

(rispetto all’utilizzo di cavi e interruttori)

▶ utilizzare l’aritmetica binaria invece di quella decimale

(due valvole per bit invece di dieci per cifra)

• Il suo progetto (macchina di von Neumann) è ancora oggi

alla base di quasi tutti i calcolatori digitali

11

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

• Inventato ai Bell Labs nel 1948 da John Bardeen, Walter Brattain e William

Shockley:

▶ nel giro di 10 anni rivoluziona la ricerca sui calcolatori;

▶ alla fine degli anni ’50 i calcolatori a valvole sono già obsoleti.

• Digital Equipment Corporation (DEC)

▶ fondata nel 1957 da Kenneth Olsen;

▶ nel 1961 realizza il PDP–1, il primo minicalcolatore.

• Sviluppo della tecnologia d’integrazione:

▶ decine (SSI), centinaia (MSI) e migliaia (LSI) di transistor sono integrati sullo stesso pezzo di

silicio (chip);

▶ possibilità di realizzare calcolatori più piccoli, più veloci e meno costosi dei loro predecessori.

• Due famiglie di calcolatori rappresentative:

▶ 360 di IBM

▶ PDP-11 di DEC

12

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

• 105–107 transistor integrati per chip.

• Passaggio dai minicalcolatori, alle workstation, ai Personal

Computer (PC):

▶ usati per applicazioni fortemente interattive (elaborazione testi, fogli

elettronici, …);

▶ in origine proposti come kit da assemblare, senza software;

▶ due architetture principali:

Apple (basato su CPU Motorola e PowerPC)

primo PC, progettato da Steve Jobs e Steve Wozniak nel ’78,

architettura proprietaria!

IBM e compatibili (CPU Intel e SW Microsoft – “Wintel”)

realizzato utilizzando componenti “off the shelf”,

architettura di dominio pubblico, quindi replicabile da altri (cloni)!

13

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

14

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

• Algoritmo

▶ descrizione della soluzione di problema scritta in modo da poter essere

eseguita da un esecutore (eventualmente diverso dall’autore dell’algoritmo)

▶ sequenza di istruzioni che operano su dati.

• Programma

▶ algoritmo scritto in modo da poter essere eseguito da un calcolatore

(esecutore automatico)

• Per scrivere un programma è necessario rappresentare istruzioni e

dati in un formato tale che l’esecutore automatico sia capace di

memorizzare e manipolare.

15

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

• Alfabeto dei simboli

▶ cifre “0”, “1”, …, “9”, separatore decimale (“,”), separatore delle migliaia (“.”) e segni

positivo (“+”) o negativo (“–”).

• Regole di composizione (sintassi), che definiscono le successioni “ben formate”

▶ “1.234,5” è la rappresentazione di un numero;

▶ “1,23,45” non lo è.

• Codice (semantica)

▶ “1.234,5” = 1×103 + 2×102 + 3×101 + 4×100 + 5×10–1

▶ “1,23,45” = ??

• Lo stesso alfabeto può essere utilizzato con codici diversi:

▶ “123,456” = 1×102 + 2×101 + 3×100 + 4×10–1 + 5×10–2 + 6×10–3, [IT]

▶ “123,456” = 1×105 + 2×104 + 3×103 + 4×102 + 5×101 + 6×100, [UK]

16

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

Chi ha “inventato” il bit?

Claude Shannon nel 1948 nel paper:

“A Mathematical Theory of Communication”

17

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

• Alfabeto binario: usiamo dispositivi con solo due stati

• Problema: assegnare un codice univoco a tutti gli oggetti compresi in un insieme

predefinito (e.g. studenti)

• Quanti oggetti posso codificare con k bit:

▶

▶

▶

▶

▶

1 bit 2 stati (0, 1) 2 oggetti (e.g. Vero/Falso)

2 bit 4 stati (00, 01, 10, 11) 4 oggetti

3 bit 8 stati (000, 001, …, 111) 8 oggetti

…

k bit 2k stati 2k oggetti

• Quanti bit mi servono per codificare N oggetti:

▶ N ≤ 2k k ≥ log2N k = log2N

(intero superiore)

• Attenzione:

ipotesi implicita che i codici abbiano tutti la stessa lunghezza

18

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

• Problema:

assegnare un codice binario univoco a tutti i giorni della settimana

• Giorni della settimana: N = 7 k ≥ log27 k = 3

• Con 3 bit possiamo ottenere 8 diverse configurazioni:

▶ Ne servono 7, quali utilizziamo?

▶ Quale configurazione associamo a quale giorno?

• Attenzione:

ipotesi che i codici abbiano tutti la stessa lunghezza

19

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

Lunedì

Lunedì

Martedì

Domenica

Sabato

Venerdì

Mercoledì

Lunedì

Giovedì

Mercoledì

Martedì

Sabato

Domenica

Martedì

Lunedì

Giovedì

Mercoledì

Sabato

Venerdì

Martedì

Mercoledì

Giovedì

Venerdì

Sabato

Venerdì

Giovedì

Domenica

1 bit

2 “gruppi”

2 bit

4 “gruppi”

Domenica

3 bit

8 “gruppi”

20

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

Lunedì

Martedì

Domenica

Giovedì

Giovedì

Giovedì

Sabato

Sabato

Martedì

Sabato

Martedì

Venerdì

Domenica

Mercoledì

Giovedì

Mercoledì

Sabato

Domenica

Mercoledì

Martedì

Domenica

Mercoledì

Venerdì

Venerdì

Lunedì

Venerdì

Lunedì

Lunedì

1 bit

2 “gruppi”

2 bit

4 “gruppi”

3 bit

8 “gruppi”

21

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

• Quanti sono gli oggetti compresi nell’insieme?

▶ 26 lettere maiuscole + 26 minuscole 52

▶ 10 cifre

▶ Circa 30 segni d’interpunzione

▶ Circa 30 caratteri di controllo (EOF, CR, LF, …)

circa 120 oggetti complessivi k = log2120 = 7

• Codice ASCII: utilizza 7 bit e quindi può rappresentare al massimo

27=128 caratteri

▶ Con 8 bit (= byte) rappresento 256 caratteri (ASCII esteso)

▶ Si stanno diffondendo codici più estesi (e.g. UNICODE) per rappresentare

anche i caratteri delle lingue orientali

22

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

010 sp

011 0

100 @

101 P

110 `

111 p

!

1

A

Q

a

q

"

2

B

R

b

r

#

3

C

S

c

s

$

4

D

T

d

t

%

5

E

U

e

u

&

6

F

V

f

v

'

7

G

W

g

w

(

8

H

X

h

x

)

9

I

Y

I

Y

*

:

J

Z

j

z

+

;

K

[

k

{

,

<

L

\

l

|

=

M

]

m

}

.

/

>

?

N O

^

_

n o

~ canc

1111

0000

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

23

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

bit = solo due stati, “0” oppure “1”.

Byte = 8 bit, quindi 28 = 256 stati

KiloByte [KB]

= 210 Byte = 1024 Byte ~ 103 Byte

MegaByte [MB] = 220 Byte = 1'048'576 Byte ~ 106 Byte

GigaByte [GB] = 230 Byte ~ 109 Byte

TeraByte [TB] = 240 Byte ~ 1012 Byte

PetaByte [PB] = 250 Byte ~ 1015 Byte

ExaByte [EB]

= 260 Byte ~ 1018 Byte

24

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

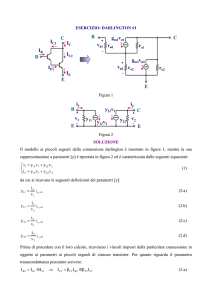

• Si segue lo schema presentato per i caratteri alfanumerici:

▶ quali e quante sono le istruzioni da codificare?

▶ qual è la lunghezza delle successioni di bit da utilizzare ?

▶ qual è la corrispondenza tra istruzioni e successioni di bit ?

Istruzione

Codice

Istruzione

Codice

Istruzione

Codice

ADD

0111 1100

LOAD

1110 1000

IF_EQ

0100 1001

SUB

0111 1101

STORE

1111 1000

GOTO

0100 1000

AND

0111 1110

………

………

RETURN

0100 1100

………

………

………

………

………

………

Istruzioni

aritmetico-logiche

Istruzioni per il

trasferimento dati

Istruzioni di

controllo

25

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

• … è necessario far riferimento ai dati necessari per completare

l’esecuzione dell’istruzione,

▶ e.g. addizione: è necessario che sia specificato (anche implicitamente) dove leggere

i due operandi da sommare e dove scrivere il risultato;

• il numero dei dati da specificare è variabile, in funzione delle

istruzioni.

0

1

2

3

4

5

6

7

8

9

0

1

2

3

4

Codice Operativo

Destinazione

Sorgente 1

Codice Operativo

Destinazione

Sorgente 1

Codice Operativo

5

6

7

8

9

0

1

Sorgente 2

2

3

4

5

6

7

8

9

0

1

Estensione del codice operativo

Operando (immediato)

Operando (immediato)

26

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

27

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

• Supporto alla CPU: deve fornire alla CPU dati e istruzioni il più

rapidamente possibile

• Archivio: deve consentire di archiviare dati e programmi

garantendone la conservazione e la reperibilità anche dopo elevati

periodi di tempo

• Diverse esigenze:

▶ velocità per il supporto alla CPU

▶ non volatilità ed elevate dimensioni per l’archivio

• Diverse tecnologie

▶ elettronica: veloce, ma costosa e volatile

▶ magnetica e ottica: non volatile ed economica, ma molto lenta

28

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

• Velocità

▶ tempo di accesso (access time)

(quanto passa tra una richiesta e la relativa risposta)

▶ velocità di trasferimento (transfer rate)

(quanti byte al secondo si possono trasferire)

• Volatilità

▶ cosa succede quando la memoria non è alimentata?

▶ per quanto tempo i dati vi rimangono immagazzinati?

• Capacità

▶ quanti byte può contenere? qual è la dimensione massima?

• Costo (per bit)

• Modalità di accesso

▶

▶

▶

▶

diretta (o casuale): il tempo di accesso è indipendente dalla posizione

sequenziale: il tempo di accesso dipende dalla posizione

mista: combinazione dei due casi precedenti

associativa: indicato il dato, la memoria risponde indicando l’eventuale posizione che il dato

occupa in memoria.

29

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

30

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

• Mantiene al proprio interno i dati e

le istruzioni dei programmi in esecuzione

• Memoria ad accesso “casuale”

• Tecnologia elettronica

▶ veloce ma volatile e costosa

• Due “eccezioni”

▶ ROM: elettronica ma permanente e di sola lettura

▶ Flash: elettronica ma non volatile e riscrivibile

31

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

• I bit nelle memorie sono raggruppati in celle:

▶ tutte le celle sono formate dallo stesso numero di bit;

▶ una cella composta da k bit, è in grado di contenere una qualunque tra le 2k

combinazioni diverse di bit.

• Ogni cella ha un indirizzo:

▶ serve come accesso all’informazione;

▶ in una memoria con N celle gli indirizzi vanno da 0 a N–1.

• La cella è l’unità indirizzabile più piccola.

In quasi tutti i calcolatori è di 8 bit (un byte).

• I byte vengono raggruppati in parole (che oggi sono di 32/64 bit),

su cui la CPU esegue le operazioni.

32

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

• Anche gli indirizzi della memoria sono rappresentati come numeri

binari:

▶ un indirizzo di M bit consente di indirizzare 2M celle;

▶ per 6 o 8 celle bastano 3 bit, per 12 celle ne servono 4;

▶ il numero di bit nell’indirizzo determina il numero massimo di celle indirizzabili

nella memoria ed è indipendente dal numero di bit per cella

(una memoria con 212 celle richiede sempre 12 bit di indirizzo, quale che sia la

dimensione di una cella).

• Una memoria può essere organizzata in diversi modi:

▶ per esempio, con 96 bit possiamo avere

6 celle di 16 bit (6*16=96),

8 celle di 12 bit (8*12=96)

12 celle di 8 bit (12*8=96).

▶ In genere si considerano celle di 8 bit (1 byte).

33

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

0

0

0

1

1

1

2

2

2

3

3

3

4

4

4

5

5

5

6

6

7

7

8 parole da 12 bit

8

6 parole da 16 bit

9

10

12 parole da 8 bit

11

34

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

linee di

selezione parola

indirizzo 0110due

• il contenuto è 01101100;

• l’operazione è di lettura (load) o

di scrittura (store) a seconda dei

comandi presenti sul bus di

controllo

0110

Bus indirizzi

DECODIFICATORE

• Viene selezionata la parola di

linea 0

0

linea 1

0

linea 2

0

linea 3

0

linea 4

0

linea 5

0

linea 6

1

linea 7

0

linea 8

0

linea 9

0

linea 10

0

linea 11

0

linea 12

0

linea 13

0

linea 14

0

linea 15

0

16 celle di memoria

di 8 bit ciascuna

0

1

1

0

1

1

0

0

0

1

1

0

1

1

0

0

parola

selezionata

leggi/scrivi

Bus di

controllo

Dato

(letto o da scrivere)

Bus dati

35

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

• Le CPU sono sempre state più veloci delle memorie

▶ l’aumento di integrazione ha consentito di realizzare CPU pipeline e super

scalari, molto efficienti e veloci;

▶ nelle memorie è aumentata la capacità più che la velocità.

• L’accesso alla memoria passa attraverso il bus

▶ la frequenza di funzionamento del bus è molto più bassa di quella della CPU;

▶ il bus può essere impegnato ad effettuare trasferimenti controllati da

dispositivi di I/O “autonomi” (e.g. DMA).

• È difficile riordinare le istruzioni in modo da poter sfruttare i tempi

di attesa della memoria.

• È possibile fare memorie molto veloci se stanno nel chip della CPU,

ma sono piccole e costose.

36

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

• Memorie di gran capacità, relativamente lente, economiche ed

accessibili tramite il bus:

▶ MGL ovvero Memoria Grossa e Lenta;

▶ dimensioni pari a circa 10 unità;

▶ tempo di accesso (TA) di circa 10 unità.

• Memorie veloci, integrate nello stesso chip della CPU, ma costose:

▶ MPV ovvero Memoria Piccola e Veloce;

▶ dimensioni pari a circa 1 unità;

▶ tempo di accesso pari a circa 1 unità.

• Obiettivo: realizzare una memoria grossa e veloce

▶ dimensioni pari a circa quelle della memoria grossa;

▶ prestazioni pari a circa quelle della memoria veloce.

37

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

Sistema di

memoria

CPU

Memoria piccola

e veloce

Livello 1

Trasferimento

di dati

Livello 2

Memoria grande

e lenta

38

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

• Località spaziale:

quando si accede all’indirizzo A, è molto probabile che gli accessi

successivi richiedano celle vicine ad A.

▶ le istruzioni del codice vengono in genere lette da locazioni consecutive della

memoria;

▶ gli accessi ad array o a strutture dati sono “vicini”.

• Località temporale:

quando si accede all’indirizzo A, è molto probabile negli accessi

successivi si richieda di nuovo la cella A.

▶ cicli di istruzioni accedono ripetutamente alle stesse locazioni di memoria;

▶ istruzioni vicine tendono ad utilizzare le stesse variabili.

39

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

• Tecnologia elettronica (veloce ma volatile)

• Gerarchia di memoria:

ai livelli più alti corrispondono le tecnologie più veloci ma anche più

costose

▶ cache interna (Static RAM – SRAM)

▶ cache esterna (SRAM)

▶ memoria RAM

(Dynamic RAM – DRAM e sue varianti)

▶ area di swap su memoria di massa

40

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

Ottenuta per “generalizzazione” dell’applicazione del principio di

località e tipicamente costituita da

1.

2.

3.

4.

5.

registri contenuti nella CPU (qualche KB)

cache (da circa 32KB a circa 4096KB)

memoria principale (da circa 512MB a qualche GB)

dischi fissi (da qualche centinaio di GB a qualche TB)

nastri magnetici e dischi ottici (da qualche centinaio di GB a qualche TB

per ogni supporto)

Man mano che ci si sposta verso il basso nella gerarchia aumenta il

valore dei parametri fondamentali:

▶

▶

▶

aumenta il tempo di accesso;

aumenta la capacità di memorizzazione;

ma diminuisce il costo per bit.

41

RAM

Supporti esterni

tecnologia tecnologia

magnetica

ottica

(HD esterni) (CD, DVD)

tecnologia

elettronica

(flash disk)

Involucro esterno del calcolatore (case)

Cache II liv

Scheda madre (motherboard)

Cache I liv

Circuito Integrato (chip)

Registri

CPU

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

Disco fisso (hard disk)

tecnologia magnetica

42

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

Livello

Capacità

Tempo di accesso

Transfer rate (GB/s)

Registri

~ 1 KB

~ 0.2 ns (1 ciclo di clock)

–

Cache I livello

~ 32 KB

~ 0.4 ns (2/4 cicli di clock)

–

Cache II livello

~ 1/2 MB

~ 1/2 ns (5/10 cicli di clock)

~ 100

Cache III livello

~ 2/8 MB

~ 5 ns

~ 50

Memoria centrale

~ 2/8 GB

~ 50 ns (1ª parola richiesta)

~ 10 ns (parole successive)

~ 5/10

Dischi interni

> 300 GB

~ 10 ms

0.15/0.6

Dischi esterni

> 300 GB

~ 10 ms

~ 0.05

43

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

Unità Centrale di Elaborazione

44

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

CPU

Dispositivi di I/O

Unità di

controllo

Unità

aritmetico

logica (ALU)

Terminale

Stampante

Registri

CPU

Memoria

centrale

Unità

disco

Bus

45

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

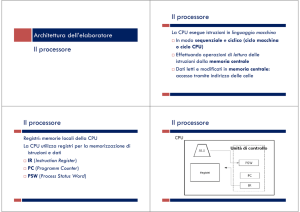

• Un calcolatore basato sull’architettura di Von Neumann esegue un programma sulla base

dei seguenti principi:

▶ dati e istruzioni sono memorizzati in una memoria unica che permette sia la scrittura che la lettura;

▶ i contenuti della memoria sono indirizzati in base alla loro posizione, indipendentemente dal tipo di

dato o istruzione contenuto;

▶ le istruzioni vengono eseguite in modo sequenziale.

• Il linguaggio per cui la CPU si comporta da esecutore è detto linguaggio macchina. Le

istruzioni scritte in linguaggio macchina sono piuttosto rudimentali:

▶ il concetto di tipo di dato è quasi assente,

▶ il numero di operandi è limitato (in genere non più di due),

▶ il numero di operazioni previste è ridotto.

Struttura istruzione

codice operativo

dest

src1

src2

Linguaggio assemblatore

add

R01

R02

R03

Linguaggio macchina

25/06/2017

000000 00000 100000 00001 00010 00011

Informatica e cultura dell’informazione – capitolo 1 – Il sistema di elaborazione

46

46

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

Fetch

Decode

Execute

47

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

Tempo

Istruzione 1

Lettura

Istruzione 2

Istruzione 3

Decodifica

Esecuzione

Lettura

Decodifica

Esecuzione

Lettura

Decodifica

Esecuzione

Ordine di esecuzione

delle istruzioni

48

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

• Data path (o percorso dei dati)

▶ è la parte che si occupa dell’effettiva elaborazione dei dati;

▶ comprende dispositivi diversi

una o più unità aritmetico-logiche, dette ALU (Arithmetic Logic Unit);

alcune unità di memorizzazione temporanea, i registri, memoria ad alta velocità usata per risultati temporanei

e informazioni di controllo (il valore massimo memorizzabile in un registro è determinato dalle dimensioni del

registro).

• Unità di controllo

▶ coordina le operazioni di tutto il processore (anche quelle del data path!);

▶ regola il flusso dei dati e indica quali registri debbano essere collegati agli ingressi e all’uscita dell’ALU;

▶ invia all’ALU il codice dell’operazione da eseguire;

▶ riceve indicazioni sull’esito dell’operazione appena eseguita dall’ALU e gestisce opportunamente queste

informazioni;

▶ comprende alcuni registri di uso specifico

Program Counter (PC) – qual è l’istruzione successiva;

Instruction Register (IR) – istruzione in corso d’esecuzione;

Program Status Word (PSW)

…

49

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

Istruzione

(e.g. add)

Registri

R00

R01

R02

X

R03

Y

…

…

…

…

Registri

ingresso ALU

Registro

uscita ALU

X

A

L

U

X

+

Y

esito

X

+

Y

Y

50

Bus indirizzi

Data path

Unità di

controllo

Bus dati

CPU

Bus controllo

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

Collegamenti per il

trasferimento dati

PSW

Collegamenti per il

trasferimento

istruzioni

ALU

IR

Registri

PC

Memoria

Collegamenti di

controllo

51

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

• Ipotizziamo che

▶ si debba eseguire l’istruzione A ⟵ A + B + C (assegna alla variabile A la somma del

contenuto delle variabili A, B e C);

▶ le corrispondenti istruzioni in linguaggio macchina si trovino all’indirizzo 789, 790, 791,

… (come riportato nella tabella sottostante);

▶ le variabili A, B e C si trovino rispettivamente nelle celle di memoria 4000 (A), 4004 (B) e

4008 (C).

Num

Istruzione

Commento

…

… … …

789

load

R02,4000

trasferisce il contenuto della cella 4000 (A) nel registro R02

790

load

R03,4004

trasferisce il contenuto della cella 4004 (B) nel registro R03

791

add

R01,R02,R03

somma il contenuto dei registri R02 e R03 e scrive il risultato in R01

792

load

R02,4008

trasferisce il contenuto della cella 4008 (C) nel registro R02

793

add

R01,R01,R02

somma il contenuto dei registri R01 e R02 e scrive il risultato in R01

794

store R01,4000

…

trasferisce il contenuto del registro R01 nella cella 4000 (A)

… … …

52

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

Data path

Unità di controllo

… …

… … …

0789

load

R02,4000

0790

load

R03,4004

0791

add

R01,R02,R03

0792

load

R02,4008

0793

add

R01,R01,R02

0794

store R01,4000

… …

… … …

… …

… … …

4000

1492

R02

4004

1918

R01

4008

2006

… …

… … …

ALU

PSW

Registri

IR

…

Istruzioni

Memoria

CPU

R05

R03

0789

Bus indirizzi

Collegamenti per il

trasferimento istruzioni

Bus dati

Collegamenti per il

trasferimento dati

Bus

controllo

R00

Dati

PC

R04

Collegamenti

di controllo

53

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

Data path

Unità di controllo

… …

… … …

0789

load R02,4000

R02,4000

load

0790

load

R03,4004

0791

add

R01,R02,R03

0792

load

R02,4008

0793

add

R01,R01,R02

0794

store R01,4000

… …

… … …

… …

… … …

4000

1492

R02

4004

1918

R01

4008

2006

… …

… … …

lettura

ALU

Registri

PSW

IR

…

Istruzioni

Memoria

CPU

R05

R03

PC

0789 +1

0790

Bus indirizzi

Bus dati

Bus

controllo

R00

Dati

R04

54

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

Data path

Unità di controllo

… …

… … …

0789

load

R02,4000

0790

load

R03,4004

0791

add

R01,R02,R03

0792

load

R02,4008

0793

add

R01,R01,R02

0794

store R01,4000

… …

… … …

… …

… … …

4000

1492

1492

R02

4004

1918

R01

4008

2006

… …

… … …

lettura

ALU

PSW

Registri

…

IR

load

R02,4000

4000

Istruzioni

Memoria

CPU

R05

R03

0790

Bus indirizzi

Bus dati

Bus

controllo

R00

Dati

PC

R04

55

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

Memoria

Data path

Unità di controllo

lettura

ALU

PSW

Registri

…

IR

load

R02,4000

… …

… … …

0789

load

0790

load R03,4004

R03,4004

load

0791

add

R01,R02,R03

0792

load

R02,4008

0793

add

R01,R01,R02

0794

store R01,4000

… …

… … …

… …

… … …

4000

1492

4004

1918

4008

2006

… …

… … …

R02,4000

Istruzioni

CPU

R05

R03

R02

0790

0791 +1

1492

R01

Bus indirizzi

Bus dati

Bus

controllo

R00

Dati

PC

R04

56

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

Data path

Unità di controllo

lettura

ALU

PSW

Registri

…

IR

load

R03,4004

4004

… …

… … …

0789

load

R02,4000

0790

load

R03,4004

0791

add

R01,R02,R03

0792

load

R02,4008

0793

add

R01,R01,R02

0794

store R01,4000

… …

… … …

… …

… … …

4000

1492

4004

1918

1918

4008

2006

… …

… … …

Istruzioni

Memoria

CPU

R05

R03

R02

0791

1492

R01

Bus indirizzi

Bus dati

Bus

controllo

R00

Dati

PC

R04

57

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

Data path

Unità di controllo

lettura

ALU

PSW

Registri

…

IR

load

R03,4004

… …

… … …

0789

load

R02,4000

0790

load

R03,4004

0791

addadd R01,R02,R03

R01,R02,R03

0792

load

R02,4008

0793

add

R01,R01,R02

0794

store R01,4000

… …

… … …

… …

… … …

4000

1492

4004

1918

4008

2006

… …

… … …

Istruzioni

Memoria

CPU

R05

R03

R02

1918

0792

0791 +1

1492

R01

Bus indirizzi

Bus dati

Bus

controllo

R00

Dati

PC

R04

58

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

Data path

Unità di controllo

esito

3410

ALU

Registri

…

PSW

add

IR

add R01,R02,R03

… …

… … …

0789

load

R02,4000

0790

load

R03,4004

0791

add

R01,R02,R03

0792

load

R02,4008

0793

add

R01,R01,R02

0794

store R01,4000

… …

… … …

… …

… … …

4000

1492

4004

1918

4008

2006

… …

… … …

Istruzioni

Memoria

CPU

R05

R03

R02

1918

0792

1492

R01

Bus indirizzi

Bus dati

Bus

controllo

R00

Dati

PC

R04

59

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

Data path

Unità di controllo

lettura

ALU

Registri

…

PSW

IR

add R01,R02,R03

… …

… … …

0789

load

R02,4000

0790

load

R03,4004

0791

add

R01,R02,R03

0792

load R02,4008

R02,4008

load

0793

add

0794

store R01,4000

… …

… … …

… …

… … …

4000

1492

4004

1918

4008

2006

… …

… … …

R01,R01,R02

Istruzioni

Memoria

CPU

R05

R03

1918

1492

R02

R01

0793

0792 +1

3410

Bus indirizzi

Bus dati

Bus

controllo

R00

Dati

PC

R04

60

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

Data path

Unità di controllo

lettura

ALU

PSW

Registri

…

IR

load

R02,4008

4008

… …

… … …

0789

load

R02,4000

0790

load

R03,4004

0791

add

R01,R02,R03

0792

load

R02,4008

0793

add

R01,R01,R02

0794

store R01,4000

… …

… … …

… …

… … …

4000

1492

4004

1918

4008

2006

2006

… …

… … …

Istruzioni

Memoria

CPU

R05

R03

1918

1492

R02

R01

0793

3410

Bus indirizzi

Bus dati

Bus

controllo

R00

Dati

PC

R04

61

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

Data path

Unità di controllo

lettura

ALU

PSW

Registri

…

IR

load

R02,4008

… …

… … …

0789

load

R02,4000

0790

load

R03,4004

0791

add

R01,R02,R03

0792

load

R02,4008

0793

R01,R01,R02

addadd R01,R01,R02

0794

store R01,4000

… …

… … …

… …

… … …

4000

1492

4004

1918

4008

2006

… …

… … …

Istruzioni

Memoria

CPU

R05

R03

1918

2006

R02

R01

0793 +1

0794

3410

Bus indirizzi

Bus dati

Bus

controllo

R00

Dati

PC

R04

62

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

Data path

5416

Unità di controllo

esito

ALU

Registri

…

PSW

add

IR

add R01,R01,R02

… …

… … …

0789

load

R02,4000

0790

load

R03,4004

0791

add

R01,R02,R03

0792

load

R02,4008

0793

add

R01,R01,R02

0794

store R01,4000

… …

… … …

… …

… … …

4000

1492

4004

1918

4008

2006

… …

… … …

Istruzioni

Memoria

CPU

R05

R03

1918

2006

R02

R01

0794

3410

Bus indirizzi

Bus dati

Bus

controllo

R00

Dati

PC

R04

63

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

Data path

Unità di controllo

lettura

ALU

Registri

…

PSW

IR

add R01,R01,R02

… …

… … …

0789

load

R02,4000

0790

load

R03,4004

0791

add

R01,R02,R03

0792

load

R02,4008

0793

add

R01,R01,R02

0794

store R01,4000

R01,4000

store

… …

… … …

… …

… … …

4000

1492

4004

1918

4008

2006

… …

… … …

Istruzioni

Memoria

CPU

R05

R03

1918

2006

R02

R01

0795

0794 +1

5416

Bus indirizzi

Bus dati

Bus

controllo

R00

Dati

PC

R04

64

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

Data path

Unità di controllo

scrittura

ALU

PSW

Registri

…

IR

store R01,4000

4000

… …

… … …

0789

load

R02,4000

0790

load

R03,4004

0791

add

R01,R02,R03

0792

load

R02,4008

0793

add

R01,R01,R02

0794

store R01,4000

… …

… … …

… …

… … …

4000

1492

4004

1918

4008

2006

… …

… … …

Istruzioni

Memoria

CPU

R05

R03

1918

2006

R02

R01

0795

5416

5416

Bus indirizzi

Bus dati

Bus

controllo

R00

Dati

PC

R04

65

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

Famiglia di CPU

Anno

Frequenza

CPU (MHz)

Registri/bus

dati (bit)

Frequenza

bus (MT/s)

Numero di

transistor

8086

1978

4.77 12

8/16

4 12

29 000

80286

1982

8 16

16/16

8 16

134 000

80386

1986

16 33

32/32

16 33

275 000

80486

1989

16 50

32/32

16 33

1 200 000

Pentium

1993

60 200

32/64

60 66

3 100 000

Pentium II

1997

233 400

32/64

66 100

7 500 000

Pentium III

1999

450 1133

32/64

100 133

24 000 000

(Willamette)

2000

1300 2000

32/64

400 533

42 000 000

(Northwood)

2002

2000 3400

32/64

400 533

55 000 000

(Prescott)

2004

2800 3800

32/64

533 800

125 000 000

(Smithfield)

2005

2800 3200

64/64

533 800

230 000 000

(Presler)

2006

2800 3600

64/64

800 1066

376 000 000

(Conroe)

2006

2400 3200

64/64

1066

291 000 000

(Merom)

2006

1666 2333

64/64

667

291 000 000

Pentium 4

Pentium D

Core 2 Duo

66

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

Osservazione fatta da Gordon Moore nel 1965:

il numero dei transistor per cm2

raddoppia ogni X mesi

In origine X era 12/18. Correzioni successive hanno portato a fissare X=18/24. Questo

vuol dire che c’è un incremento di circa il 40/60% all’anno.

67

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

Numero di transistor integrati

1'000'000'000

100'000'000

10'000'000

1'000'000

Andamento previsto dalla legge di Moore: il

numero di transistor integrati in un chip

raddoppia ogni 24 mesi

100'000

Anno

10'000

1978

1982

1986

1990

1994

1998

2002

2006

68

• SISD: Single Instruction Single Data

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

• MISD: Multiple Instruction Single Data

• SIMD: Single Instruction Multiple Data

• MIMD: Multiple Instruction Multiple Data

69

69

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

N Cores

#Cores

1000 cores

64 cores

32

Sun IBM Cell Larrabee

8-24

cores

Intel

4

Quad

core

2

Il mondo

dell’informatica è

pronto per una

rivoluzione

Dual

core

1

2005

70

2006

2007

2014 Time

70

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

• Il progresso della tecnologia provoca un aumento del numero di

•

•

•

•

transistor per cm2 e quindi per chip.

Un maggior numero di transistor per chip permette di produrre

prodotti migliori (sia in termini di prestazioni che di funzionalità) a

prezzi ridotti.

I prezzi bassi stimolano la nascita di nuove applicazioni (e.g. non si

fanno video game per computer da milioni di €).

Nuove applicazioni aprono nuovi mercati e fanno nascere nuove

aziende.

L’esistenza di tante aziende fa crescere la competitività che, a sua

volta, stimola il progresso della tecnologia e lo sviluppo di nuove

tecnologie.

71

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

• Fonti per lo studio

▶ Informatica arte e mestiere, S. Ceri, D. Mandrioli, L. Sbattella, McGrawHill

Capitolo 2

▶ Introduzione ai sistemi informatici, D. Sciuto, G. Buonanno, L. Mari, 4a Ed,

McGrawHill

Capitolo 1, 2, 5

▶ The Art & Craft of Computing, S. Ceri, D. Mandrioli, L. Sbattella, Addison-Wesley

Capitolo 2

• Approfondimenti

▶ Struttura e progetto dei calcolatori, D. A. Patterson, J. Hennessy, 3a Ed, Zanichelli

Capitolo 1, 2

• Credits

▶ Prof. G. Buonanno e D. Sciuto, LIUC

72