Logica CMOS dinamica

Ing. Ivan Blunno

21 aprile 2005

1

Introduzione

In quessta dispensa verrà presentata la logica CMOS dinamica evidenziandone

i principi di funzionamento, la tecnica di progetto i vantaggi e gli svantaggi

rispetto alla logica CMOS statica.

2

Principio di funzionamento

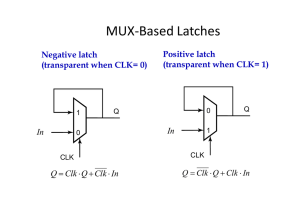

In figura 1 è mostrato lo schema di principio di un circuito in logica dinamica.

In questo particolare esempio la funzione logica viene implementata da un blocco di logica composto da transistor NMOS (n-logic block). Il funzionamento

dell’equivalente circuito implementato con transistor PMOS è analogo. La logica dinamica si basa su due elementi fondamentali: la presenza di una capacità

sull’uscita e di un segnale di clock. In generale la capacità di carico non sarà

un condensatore aggiunto appositamente, ma più semplicemente la capacità parassita della logica che segue il circuito in esame. Più precisamente si tratterà

della capacità di gate del transistor MOS di ingresso del dispositivo successivo.

Analizziamo ora il funzionamento del circuito di figura 1 mettendo in evidenza

due fasi: quella di precarica e quella di valutazione (precharge e evaluation

in inglese).

• clk = 0: PRECARICA. In questa fase il transistor NMOS è interdetto e

pertanto non vi è alcun possibile cammino verso massa (qualunque sia la

il comportamento del blocco n-logic. Il transistor PMOS, viceversa, è in

conduzione. Il circuito si comporta pertanto come l’equivalente di figura

2.a ed il condensatore si carica alla tensione di alimentazione. Durante

tutta la fase di precarica Y = 1.

• clk = 1: VALUTAZIONE. Durante la fase di valutazione il PMOS è interdetto mentre il NMOS conduce. Il circuito si comporta come l’equivalente

di figura 2.b dove il blocco n-block è stato sostituito da un interruttore

controllato dai segnali di input. Durante la fase di valutazione possono

succedere due cose:

1

Y

input

n−logic

block

clk

Figura 1: Logica CMOS dinamica: schema di principio.

Y

Y

a)

b)

Figura 2: Circuito equivalente durante la fase di a) precarica e b) valutazione.

2

– Il blocco n-block è in conduzione (per effetto degli ingressi) e la

capacità si scarica verso massa. In questo caso, trascorso il breve

transitorio, si avrà Y = 0.

– Il blocco n-block è interdetto. In questo caso il nodo Y risulterà

scollegato sia dall’alimentazione che da massa e manterrà pertanto

la carica accumulata durante la fase di precarica. Si avrà dunque

Y = 1.

2.1

Logica dinamica tipo P

Il caso in cui il blocco di logica fosse di tipo P, è assolutamente analogo. In questo

caso però si avrebbe una fase di prescarica in corrispondenza del clock a valore

1, ed una fase di valutazione, in corrispondenza del clock a 0, dove il nodo di

uscita verrebbe condizionalmente portato a valore logico alto dipendentemente

dal valore degli ingressi.

3

Progetto della rete del n-block

Abbiamo visto come il valore dell’uscita Y dipende, nelle varie fasi, dal segnale

clk (clock) e dalla rete interna al n-block pilotata dagli ingressi della porta logica. Questa rete coincide esattamente con il blocco di pull-down di una porta

in logica CMOS statica e pertanto per il suo progetto si utilizzeranno le stesse

tecniche viste per quei tipi di circuiti. In modo analogo nel caso di logica di

tipo P la rete interna al p-block coinciderà con il blocco di pull-up di una porta

logica CMOS statica. A scopo di esempio, supponiamo di voler progettare un

circuito realizzante la seguente funzione logica:

Y = A · (B + C) + D · E

Si noti come, anche nel caso di logica CMOS dinamica, le funzioni che si

possono realizzare sono solo funzioni negate (a meno di utilizzare un ulteriore

inverter in cascata).

Il risultato sarà quello mostraato in figura 3 dove è stato omesso il condensatore in quanto, essendo intrinsecamente presente in ogni circuito, non deve

essere considerato in fase di progetto.

È importante sottolineare che i segnali di ingresso devono stabilizzarsi durante la fase di precarica, perché eventuali variazioni durante la fase di valutazione

potrebbero portare alla metastabilità o addirittura a dei valori inesatti di Y.

Si supponga, ad esempio, che nel circuito di figura 3, A, B, C e D siano tutti

posti a 0, mentre E sia posto a 1. Evidentemente, in questa condizione, ci si

aspetterebbe una uscita Y = 1. Se però durante la fase di valutazione anche

solo per un istante D passa ad 1, il condensatore comincia a scaricarsi perdendo

presto la carica immagazzinata nella precedente fase di precarica e portando

3

clk

Y

D

E

A

B

C

clk

Figura 3: Ciurcuito che implementa la funzione Y = A · (B + C) + D · E.

cosı̀ l’uscita Y a valore 0 o ad un valore indeterminato (metastabilità). Un altro

problema deriva dal fatto che la capacità parassita è molto piccolo (nell’ordine

di pochi fF) e inoltre presenta inevitabilmente delle perdite. Per questa ragione,

se il tempo che intercorre tra la fase di precarica e quella di valutazione è troppo

lungo il valore di Y finirà sempre per essere nullo, a prescindere dal valore dei

segnali di ingresso.

4

Charge sharing

È il fenomento che si verifica quando, a seguito della chiusura di un interruttore,

due capacità con tensione diverse vengono a trovarsi in parallelo. Il risultato

è che le due capacità si porteranno ad un valore di tensione uguale ed intemedio tra i valori che avevano prima della chiusura dell’interrutore. Per meglio

comprendere questo fenomeno, analizziamolo riferendoci alla figura 4

Si ricordi che in un condensatore, capacità, quantità di carica immagazzinata e tensione sono legati dalla relazione Q = CV . Siano Vi e Vz i valori di

tensione iniziale. Le quantità di carica immagazzinate nei due condensatori saranno allora

4

t=0

Vi

Ci

Cz

Vz

Figura 4: Fenomeno del charge sharing.

Qz = Cz Vz e Qi = Ci Vi

Al momento della chiusura dell’interrutore la quantità di carica totale sarà

data dalla somma delle due quantità di carica

QT = Qz + Qi = Cz Vz + Ci Vi

Inoltre i due condensatori si troveranno in parallelo, formando un unico condensatore di capacità equivalente

CT = Cz + Ci

La tensione dopo la chiusura dell’interruttore sarà dunque

VT =

QT

C Z VZ + C i Vi

=

CT

Cz + Ci

Supponiamo, a titolo di esempio, Vi = 0 e Vz = VDD

Alla chiusura dell’interrutore

VT =

Cz VDD

Cz

= VDD

Cz + Ci

Cz + Ci

In pratica si ha un partitore capacitivo. In una porta logica dinamica il

variare di un ingresso può portare in conduzione un transistor mettendo in

parallelo al condensatore parassita di uscita, un altro condensatore, andando

cosı̀ ad abbassarne, anche notevolmente la tensione e rendendo irriconoscibile

(o addirittura sbagliato) il valore logico dell’uscita come mostrato in figura 5.

5

T

5V

T

5V

0V

a)

T

0V

b)

?

?

c)

Figura 5: Charge sharing in una porta logica dinamica (a), con interrutori

equivalenti e T aperto (b) e con T chiuso (c).

5

Confronto tra logiche CMOS statiche e dinamiche

L’esigenza di utilizzare la logica dinamica nasce dal desiderio di ridurre l’area

necessaria all’implementazione di una certa funzione logica. La logica CMOS

statica è fortemente ridondante: per ogni segnale di ingresso è necessario inserire un transistor NMOS ed uno PMOS. La logica dinamica è invece decisamente

più compatta. In questo secondo caso i transistor utilizzati sono solo la metà più

2 (i due pilotati dal clock). Evidentemente il vantaggio diventa tanto maggiore

quanto più sono i segnali di ingresso impiegati. A fronte di questo evidente vantaggio c’è però lo svantaggio di dover gestire e distribuire un segnale di

clock. La fase di progetto inoltre viene a complicarsi notevolmente, dovendo

essere affrontate problematiche di temporizzazione dei segnali di ingresso che,

come già detto, non devono variare il loro valore durante la fase di valutazione. La convenienza di una dell’altra famiglia logica dipenderà pertanto dalle

applicazioni.

6

Connessione di porte logiche dinamiche

Nei paragrafi precedenti è stato descritto il funzionamento delle logiche dinamiche in generale. In realtà, per potere completare l’analisi di questa famiglia di

circuiti è necessario analizzare anche l’interconnessione tra blocchi di logica.

A questo propossito si esamini l’esempio di figura 6. Consideriamo il caso

6

Y1

Y2

IN1

clk

clk

Figura 6: Cascata di due celle di logica dinamica.

semplice in cui i blocchi abbiano un solo ingresso. In particolare la seconda cella

dipende solo dalla prima (anche se le conclusioni a cui arriveremo valgono per

qualunque caso). Poiché i blocchi che realizzano le due celle sono composti solo

di transistor NMOS, è evidente che, qualunnque sia la funzione che implementano, se l’ingresso è a 1 logico l’uscita dovrà essere, a regime, di zero logico.

Analogamente se l’ingresso è a 0 logico l’uscita sarà pari a 1 logico (ovviamente,

trantandosi di porte ad un solo ingresso che implementano funzioni invertenti,

non è possibile ottenere altro che un inverter!). Il funzionamento, che per una

porta sola “isolata” dal mondo esterno è già stato analizzato, in questo caso non

è quello previsto. Infatti durante la fase di precarica entrambe le uscite (Y1 ed

Y2) sono ad 1 logico. Quando poi si passa alla fase di valutazione, Y1 dovrebbe

scaricarsi e diventare uno 0 mentre Y2 dovrebbe mantenere il suo valore di 1

logico. Quello che in realtà succedde è che all’inizio della fase di valutazione

Y1 è ancora ad 1 e pertanto porta in conduzione il n-logic block della seconda

cella che comincerà pertanto a scaricare Y2. La scarica di Y2 continuerà fin

tanto che Y1 non avrà raggiunto un valore sufficientemente prossimo allo 0. In

generale potrebbe essere totale. In ogni caso si verifica esattamente ciò che nel

paragrafo precedente avevamo detto essere proibito: gli ingressi di una porta

cambiano di valore durante la fase di valutazione. Questo fenomeno si presenta a prescindere dalla funzione logica implementata dalla porta e dal numero

di ingressi. La natura stessa della rete logica (implementata da NMOS) che

conduce sicuramente quando tutti gli ingressi sono ad 1 (ed all’inizio della fase

di valutazione è sempre cosı̀) rende questo tipo di connessione in cascata non

attuabile nei casi reali, rendendo necessario il ricorso ad alcune piccole varianti.

7

Y1

Z1

d1

clk

Y2

Z2

d2

clk

Y3

Z3

d3

clk

Figura 7: Logica domino.

6.1

Logica domino

Una prima possibile soluzione al problema visto nel paragrafo precedente consiste nell’inserire un inverter all’uscita di ogni stadio della cascata. Il risultato

è che al termina della fase di precarica, tutte le uscite sono allo zero logico e

non portando pertanto in conduzione lo stadio successivo fin tanto che la valutazione non sia terminata ed abbia determinato un 1 (che però a questo punto

è corretto) sull’uscita. Analizziamo allora l’esempio di figura 7 dove d1 , d2 ed3

rappresentano i ritardi (in fase di valutazione) dei tre stadi di logica dinamica.

Supponiamo che a regime l’uscita Z1 del primo stadio debba valere 1. Durante

la fase di precarica tutti i nodi Yi sono ad 1 e di conseguenza tutti i nodi Zi

sono a 0. Al tempo t = 0 inizia la fase di valutazione che però ha effetto solo sul primo stadio in quanto tutti quelli successivi hanno gli ingressi a 0 che

interdicono il blocco NMOS. Dopo un tempo t = d1 l’uscita Z1 sarà salita ad

1 ed anche il secondo stadio comincerà a scaricare il nodo Y2 . Stesso discroso

può essere ripetuto al tempo t = d1 + d2 e t = d1 + d2 + d3 . In pratica, quello

che succede, è che il termine della fase di valutazione di uno stadio fa partire

(se necessario) la fase di valutazione dello stadio successivo. Si ottiene cosı̀ una

propagazione in cascata dei risultati proprio come nel gioco del domino (da cui

il nome di questa particolare implementazione di logica dinamica). Sebbene il

problema iniziale sia stato risolto, sono ancora presenti alcuni inconvenienti:

• Ogni porta ha bisogno di una inverter aggiuntivo (al costo di due transistor

in più).

• Resta ancora il problema de charge sharing.

Per risolvere il problema del charge sharing è possibile aggiungere un transistore PMOS di pull-up “debole” (vedi figura 8.a) cioè a basso guadagno che

8

Y

inputs

n−logic

block

Y

inputs

clk

n−logic

block

clk

a)

b)

Figura 8: Possibili soluzioni al problema del charge sharing.

interviene a ripristinare la carica persa solo nel caso che l’uscita debba rimanere a 1. Lo stesso transistor, proprio perché debole, non riuscirà a contrastare

l’azione della rete di pull-down nel caso questa cercasse di portare l’uscita a 0.

Alternativamente è possibile collegare il pmos debole all’uscita dell’inverter in modo che, nel momento in cui la rete di pull-down comincia a portare

l’ingresso dell’inverter a livello basso, l’uscita sale a 1 spegnendo il transistor

di pull-up (figura 8.b). Il transistor cosı̀ aggiunto permette inoltre di lavorare

anche a frequenze più basse compensando le correnti di perdita.

6.2

Logica domino NP

Un’idea alternativa alla precedente è qulle mostrata in figura 9 dove le porte in

logica N si alternano a quelle in logica P.

In questo caso, al fine di sincronizzare tra di loro le fasi di precarica e prescarica, i blocchi in logica P avranno il clock negato. Il vantaggio di questo

tipo di architettura è che si risparmia l’inverter da interporre tra una porta e

la successsiva, lo svantaggio è che bisognerà di stribuire due segnali di clock (il

negato ed il non negato).

7

Logica a 2 fasi

L’ultima architettura di logica dinamica che viene presentata in questa dispensa

è la logica a 2 fasi, il cui schema elettrico è mostrato in figura 10 nel caso di

un solo ingresso. Ancora una volta si fa notare che i condensatori evidenziati

esplicitamente nello schema elettrico sono in realtà condensatori parassiti.

Esaminiamo il funzionamento di questo tipo di logica.

9

Y1

Y2

N

logic

IN1

clk

Y3

P

logic

clk

N

logic

clk

Figura 9: Logica domino NP.

Φ1

Φ2

Φ1

Φ2

T1

N

logic

Φ1

T2

L1

N

logic

Φ2

Φ1

Φ2

Figura 10: Logica a 2 fasi: schema circuitale.

10

L2

Φ1

Φ2

Figura 11: Logica a 2 fasi:segnali di clock.

• φ1 = 1.

T1 fa passare il dato mentre L1 è in precarica. Il dato viene memorizzato

nel condensatore.

• φ1 = 0.

T1 si apre garantendo che l’ingresso non cambi più. Contemporaneamente

L1 va in valutazione.

• φ2 = 1.

T2 fa passare il dato mentre L2 è in precarica. Il dato viene memorizzato

nel condensatore.

• φ2 = 0.

T2 si apre garantendo che l’ingresso non cambi più. Contemporaneamente

L2 va in valutazione.

È molto importante che le due fasi del clock (φ1 e φ2 ) non siano mai ad 1

contemporaneamente, come mostrato in figura 11 per evitare che gli ingressi di

uno stadio possano cambiare valore durante la fase di valutazione.

Ogni blocco comandato dalla fase φ1 è preceduto e seguito da uno comandato

dalla fase φ2 e viceversa.

11