Laboratorio 3: Celle di memoria RAM

Ing. Ivan Blunno

21 aprile 2005

1

Cella RAM statica a 4 transistor

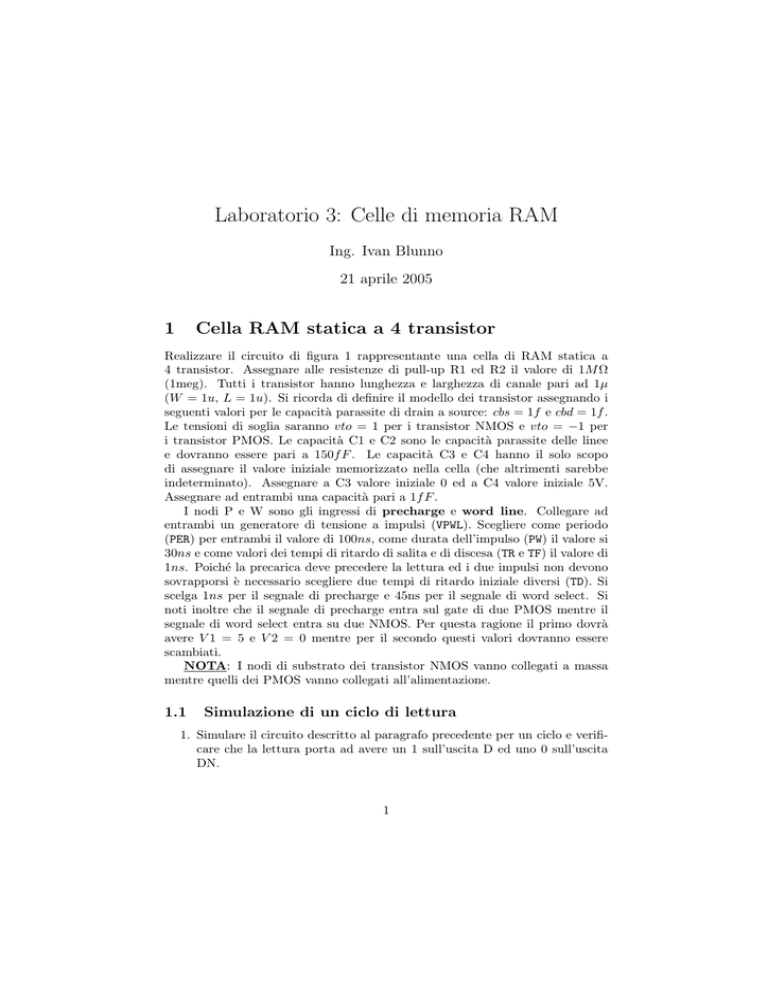

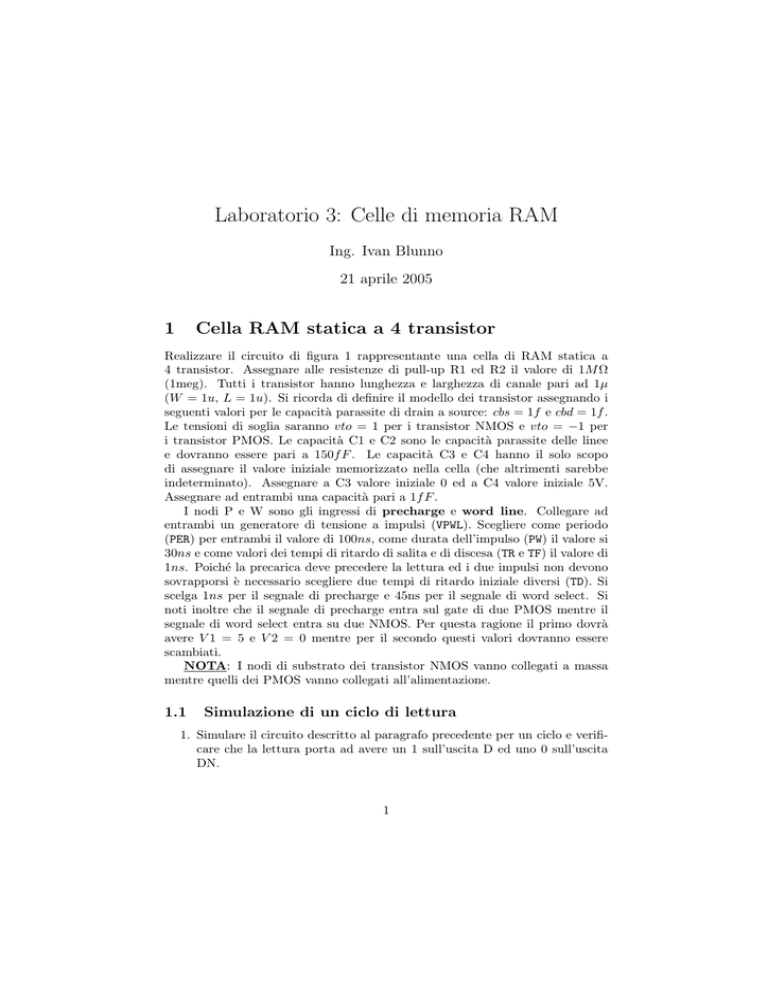

Realizzare il circuito di figura 1 rappresentante una cella di RAM statica a

4 transistor. Assegnare alle resistenze di pull-up R1 ed R2 il valore di 1M Ω

(1meg). Tutti i transistor hanno lunghezza e larghezza di canale pari ad 1µ

(W = 1u, L = 1u). Si ricorda di definire il modello dei transistor assegnando i

seguenti valori per le capacità parassite di drain a source: cbs = 1f e cbd = 1f .

Le tensioni di soglia saranno vto = 1 per i transistor NMOS e vto = −1 per

i transistor PMOS. Le capacità C1 e C2 sono le capacità parassite delle linee

e dovranno essere pari a 150f F . Le capacità C3 e C4 hanno il solo scopo

di assegnare il valore iniziale memorizzato nella cella (che altrimenti sarebbe

indeterminato). Assegnare a C3 valore iniziale 0 ed a C4 valore iniziale 5V.

Assegnare ad entrambi una capacità pari a 1f F .

I nodi P e W sono gli ingressi di precharge e word line. Collegare ad

entrambi un generatore di tensione a impulsi (VPWL). Scegliere come periodo

(PER) per entrambi il valore di 100ns, come durata dell’impulso (PW) il valore si

30ns e come valori dei tempi di ritardo di salita e di discesa (TR e TF) il valore di

1ns. Poiché la precarica deve precedere la lettura ed i due impulsi non devono

sovrapporsi è necessario scegliere due tempi di ritardo iniziale diversi (TD). Si

scelga 1ns per il segnale di precharge e 45ns per il segnale di word select. Si

noti inoltre che il segnale di precharge entra sul gate di due PMOS mentre il

segnale di word select entra su due NMOS. Per questa ragione il primo dovrà

avere V 1 = 5 e V 2 = 0 mentre per il secondo questi valori dovranno essere

scambiati.

NOTA: I nodi di substrato dei transistor NMOS vanno collegati a massa

mentre quelli dei PMOS vanno collegati all’alimentazione.

1.1

Simulazione di un ciclo di lettura

1. Simulare il circuito descritto al paragrafo precedente per un ciclo e verificare che la lettura porta ad avere un 1 sull’uscita D ed uno 0 sull’uscita

DN.

1

P

R1

R2

C1

C2

C3

C4

W

D

DN

Figura 1: Cella RAM statica a 4 transistor

2. Collegare l’ingresso di precarica P all’alimentazione (precarica interdetta)

e assegnare ai condensatori parassiti delle linee C1 e C2 il valore iniziale

0. Verificare come il tempo durante il quale il segnale W resta ad 1 non è

suffciente a portare le due linee ai valori di regime.

1.2

Simulazione di un ciclo di scrittura

Mantenendo la precarica interdetta (nel ciclo di scrittura questa fase non è necessaria) collegare la linea D a massa e la linea DN all’alimentazione e verificare

che al termine del ciclo di scrittura il valore contenuto nella cella (tensioni ai

capi delle capacità parassite C3 e C4) è cambiato.

2

Cella RAM statica a 6 transistor

Modificare il circuito di figura 1 sostituendo alle due resistenze due transitor

PMOS con gli ingressi collegati a quelli dei rispettivi NMOS.

2.1

Simulazione di un ciclo di lettura

Ripetere le simulazioni del paragrafo 1.1. In particolar modo verificare che per

questo tipo di cella il ciclo di precarica non è necessario, ma può essere utile

per avere il valore alto sulle linee di dato pari a 5 volt (senza precarica il valore

2

massimo che si può raggiungere sarà pari a VDD − VT n = 4V per via del pass

transistor).

2.2

Simulazione di un ciclo di scrittura

Ripetere la simulazione del paragrafo 1.2

3

Cella RAM dinamica a 4 transistor

La cella dinamica a 4 transistor può essere ottenuta semplicamente dalla cella

statica a 6 transistor eliminando i due transistor PMOS di pull-up.

3.1

Simulazione di un ciclo di lettura

1. Ripetere le simulazione del paragrafo 1.1 e verificare come il ciclo di precarica sia necessario a garantire il corretto funzionamento della cella in

fase di lettura.

2. Provare a deteriorare il contenuto della cella di memoria, assegnando ad

esempio un valore iniziale al condensatore C4 pari a 3V invece di 5V.

Verificare che il ciclo di lettura ripristina un valore corretto di tensione

nella capacità.

3.2

Simulazione di un ciclo di scrittura

Ripetere la simulazione del paragrafo 1.2

4

Cella RAM dinamica a 1 transistor

Si realizzi il circuito di figura 2. Si utilizzino come capacità di linea (C1 e C2) un

valore di 150f F . Si utilizzi come capacità di memoria C3 un valore di 50f F . Non

potendo utilizzare più di 10 transistor non è possibile precaricare il condensatore

C2. È dunque necessario dare a questo condensatore un valore iniziale di 2.5V .

Realizzare gli inverter tri-state che compongono il sense amplifier come mostrato

in figura 3.

ATTENZIONE: questa volta il transistor di precharge è collegato a 2.5V

e NON a 5V !!!

4.1

Simulazione di un ciclo di lettura

Per poter effettuarre la simulazione è necessario generarsi i segnali di sense (S e

S) che attivano gli inverter tri-state. Questi segnali devono iniziare dopo l’inizio

della fase di word select e terminare contemporaneamente al termine della fase

3

2.5V

P

C1

C3

C2

W

S

S

Figura 2: Cella RAM dinamica ad 1 transistor

S

S

Figura 3: Inverter tri-state

4

di word select. È possibile che alcuni condensatori non riescano a raggiungere

il valore di regime perché i tempi di carica sono troppo brevi. Per risolvere il

problema si possono allungare i tempi di carica oppure aumentare le larghezze

di canale (W) dei transistor.

1. Simulare il ciclo di lettura ponendo la condizione iniziale di C3 prima a

5V e poi a 0V . Verificare come sulla linea, prima della fase di sense, il

salto di tensione sia molto basso.

2. ripetere la simulazione precedente ponendo la condizione iniziale di C3

pari a 2.7V e verificare se il circuito funziona ancora. Verificare che al

termine della fase di sense il valore presente nel condensatore C3 è stato

ripristinato a 5V.

3. Ripetere le simulazioni precedenti utilizzando un condensatore di memoria

(C3) più piccolo e verificare che il circuito funzioni ancora.

5