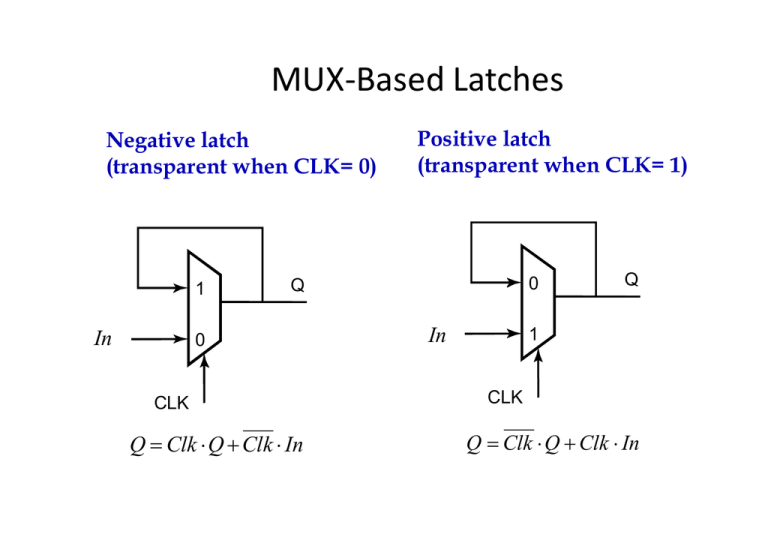

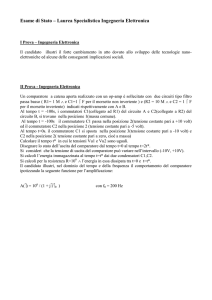

MUX-Based Latches

Negative latch

(transparent when CLK= 0)

1

InD

Positive latch

(transparent when CLK= 1)

0

Q

0

CLK

Q Clk Q Clk In

InD

Q

1

CLK

Q Clk Q Clk In

MUX-Based Latch

- quando il clock è basso, il circuito è un latch

- quando il clock è alto, l’anello è aperto

CLK

QM

CLK

QM

D

CLK

CLK

NMOS only

Non-overlapping clocks

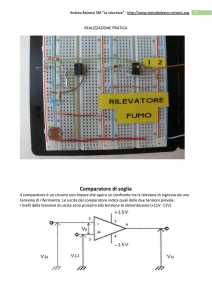

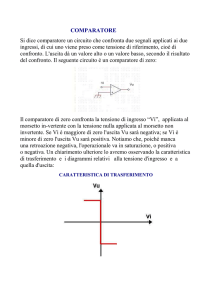

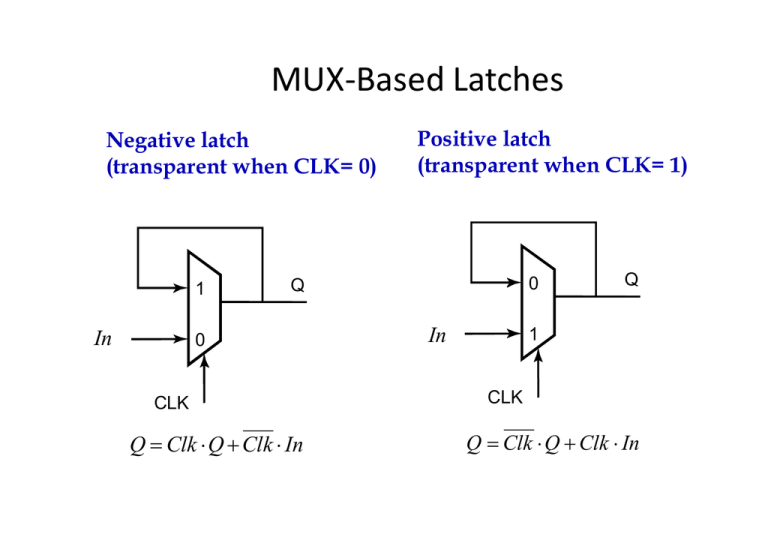

Trigger di Schmitt (comparatore con isteresi)

In molte situazioni pratiche, è possibile che sulla linea d’ingresso compaiano

delle fluttuazioni di tensione indesiderate (rumore)

Segnale sinusoidale a bassa frequenza applicato all’ingresso di un comparatore

utilizzato come rivelatore di livello zero

L’andamento irregolare della

tensione d’uscita si verifica perché,

a causa del rumore, il comparatore

è costretto a commutazioni

improprie.

L’instabilità si innesca ogni volta

che la Vin si avvicina alla tensione

di riferimento.

Non-Bistable Sequential Circuits

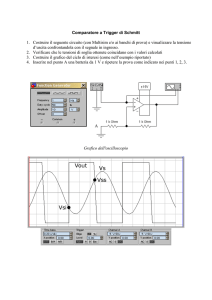

Schmitt Trigger

In

V OH

Vou t

Out

Per rendere il comparatore

meno sensibile al rumore si

può

impiegare

la

tecnica

V OL

chiamata isteresi, basata sulla

retroazione positiva

VM–

VM+

Vi n

transcaratteristica con isteresi

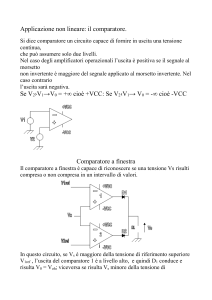

Noise Suppression using Schmitt Trigger

Vin

Vout

VM

VM

t0

t

t0 + tp

Quando la tensione d’ingresso sale (passa da un livello minore a uno maggiore), il

livello della tensione di riferimento risulta più elevato di quando la tensione

d’ingresso scende (passa da un livello maggiore ad uno minore)

t