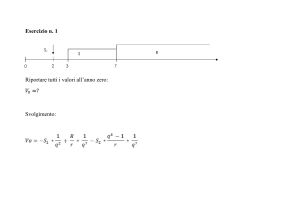

Prova scritta C.I.D. 10/1/06

1/3

Studente:

1) Riportare lo schema elettrico di una porta complessa CMOS che realizza la funzione

Y A (B C) (D E F )

b) riportare i due grafi ad archi rispettivamente delle reti NMOS e PMOS che realizzano la porta

c) ricercare gli eventuali percorsi di Eulero per i due grafi realizzati

d) indicare sinteticamente, in base ai percorsi indicati, il lay-out della struttura, riportando le linee

poly di gate, le regioni di diffusione e le interconnessioni metalliche (indicate con linee

schematiche)

a) schema elettrico

b)grafi ad archi e percorsi di Eulero scelti per il lay-out:

c) lay-out schematico:

Prova scritta C.I.D. 10/1/06

2/3

Studente:

2) Per la porta complessa CMOS della domanda n. 1, che si suppone pilotare una generica capacità

CL: a) identificare le transizioni dei segnali all’ingresso della porta che determinano le condizioni

peggiori rispettivamente per il tPHL W.C e il tPLH W.C.; b) Dimensionare i PMOS e gli NMOS della

porta affinchè i due tempi di propagazione tPHL W.C e tPLH W.C. precedentemente determinati siano

uguali.

a) per tPHL W.C :

A

B

C

D

E

F

per tPLH W.C :

A

B

C

D

E

F

b) Procedimento per il dimensionamento dei PMOS e NMOS:

3) Riportare gli schemi elettrici di a) una porta AND a due ingressi e b) di una porta OR a due

ingressi, realizzate con pass transistors P e N, riportando nelle rispettive tabelle di verità i valori

effettivi di tensione relativi ai livelli logici in uscita per ciascuno dei casi previsti dalla tabella,

assumendo in ingresso valori logici standard CMOS.

a) AND

A

B

Y

Tensione

b) OR

A

B

Y

Tensione

Prova scritta C.I.D. 10/1/06

3/3

Studente:

4) a) Riportare lo schema logico di un latch SR sincronizzato dal livello del clock.

b) riportare i diagrammi di temporizzazione (si trascurino i tempi di salita e discesa) delle grandezze

coinvolte nei due casi: S=1, R=0 e S=0, R=1, con le condizioni iniziali indicate per le uscite, e

tenendo conto di un ritardo di propagazione tP uguale per tutte le porte.

a) schema logico:

Temporizzazione dei segnali per S=1, R=0:

Ck

Q

Q

tP

Temporizzazione dei segnali per S=0, R=1:

Ck

Q

Q

tP