Tecnologia CMOS

Ing. Ivan Blunno

21 aprile 2005

1

Introduzione

In questa dispensa verranno presentati i circuiti CMOS (Complementary MOS).

Nella prima parte verrà analizzato in dettaglio il funzionamento di un circuito

CMOS molto semplice (inverter); in seguito si analizzerà la tecnica di progetto

di circuiti in grado di implementare funzioni logiche più complesse.

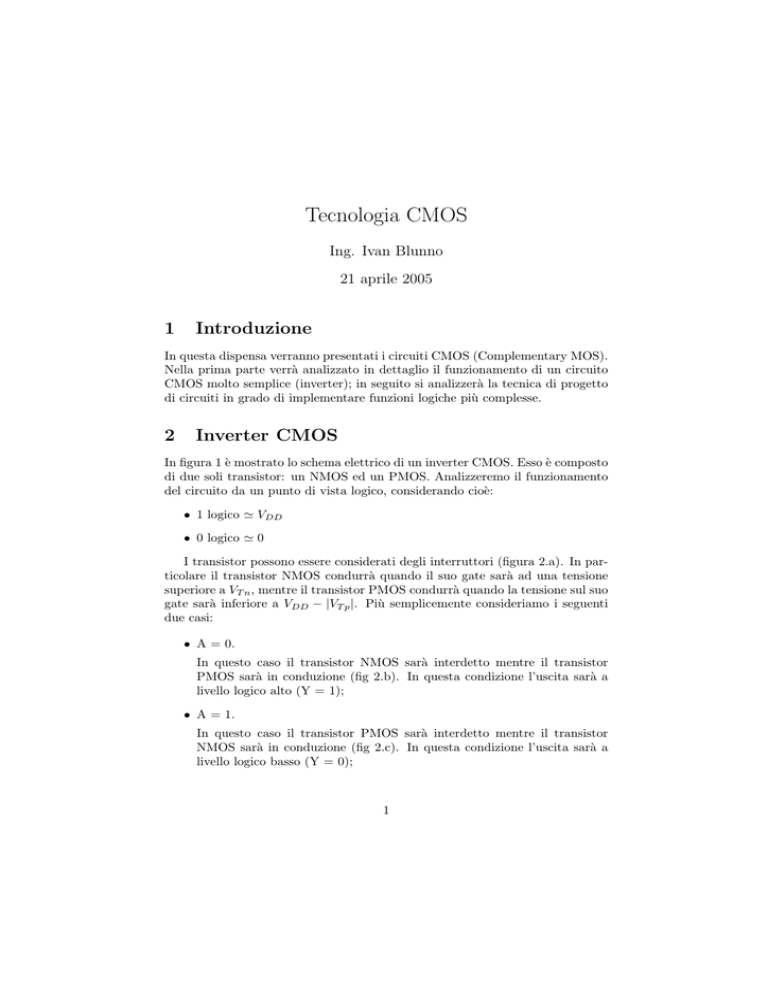

2

Inverter CMOS

In figura 1 è mostrato lo schema elettrico di un inverter CMOS. Esso è composto

di due soli transistor: un NMOS ed un PMOS. Analizzeremo il funzionamento

del circuito da un punto di vista logico, considerando cioè:

• 1 logico ' VDD

• 0 logico ' 0

I transistor possono essere considerati degli interruttori (figura 2.a). In particolare il transistor NMOS condurrà quando il suo gate sarà ad una tensione

superiore a VT n , mentre il transistor PMOS condurrà quando la tensione sul suo

gate sarà inferiore a VDD − |VT p |. Più semplicemente consideriamo i seguenti

due casi:

• A = 0.

In questo caso il transistor NMOS sarà interdetto mentre il transistor

PMOS sarà in conduzione (fig 2.b). In questa condizione l’uscita sarà a

livello logico alto (Y = 1);

• A = 1.

In questo caso il transistor PMOS sarà interdetto mentre il transistor

NMOS sarà in conduzione (fig 2.c). In questa condizione l’uscita sarà a

livello logico basso (Y = 0);

1

Y

A

Figura 1: Inverter CMOS: schema elettrico.

Y

a)

Y

b)

Y

c)

Figura 2: Inverter CMOS: a)equivalente elettrico, b)ingresso a 0 logico, c)

ingresso a 1 logico.

2

B

A

Y

A

B

A B

Y

0

0

1

1

1

1

1

0

0

1

0

1

Figura 3: Porta logica NAND.

Da questa semplice analisi è possibile verificare il corretto funzionamento del

circuito in questione: un ingresso a 1 porta l’uscita a 0, un ingresso a 0 porta

l’uscita a 1.

Già in questo semplice circuito è possibile notare la struttura complementare dei circuiti CMOS (che verrà meglio evidenziata nel seguito): quando il

transistor NMOS conduce, il PMOS è interdetto e viceversa.

3

Porta logica NAND

In figura 3 è mostrato lo schema elettrico di una porta logica NAND CMOS e la

sua tavola di verità. Considerando i transistor ancora una volta come se fossero

degli interrutori è facile analizzare il comporatmento del circuito.

• A = 0, B = 0. I transistor NMOS sono entrambi interdetti, mentre i

transistor PMOS conducono entrambi. In questa condizione l’uscita Y

non può che valere 1.

• A = 0, B = 1. Il transistor NMOS controllato da B adesso conduce, ma

si trova comunque in serie ad un altro transistor NMOS interdetto (quello

controllato da A). Il cammino verso massa risulta dunque interdetto. Per

quanto riguarda i PMOS invece, il transistor controllato da B è interdetto,

ma si trova in parallelo ad un transistor che conduce (quello controllato

da A). L’uscita Y varrà pertanto 1.

3

A

B

Y

B

A

A B

Y

0

0

1

1

1

0

0

0

0

1

0

1

Figura 4: Porta logica NOR.

• A = 1, B = 0. Questo caso è assolutamente identico al precedente e l’uscita

Y varrà ancora 1.

• A = 1, B = 1. In quest’ultima configurazione entrambi i transistor NMOS

sono in conduzione (permettendo un cammino verso massa) mentre i

transistor PMOS sono entrambi interdetti. L’uscita Y varrà dunque 0.

4

Porta logica NOR

Un’analisi del tutto analoga a quella condotta nel paragrafo precedente può

essere utilizzata per verificare il corretto funzionamento della porta NOR CMOS

mostrata in figura 4. Si noti come la strutura è assolutamente la duale della

precedente: i transistor che prima erano in serie ora sono in parallelo e viceversa.

5

Generiche funzioni logiche in tecnologia CMOS

La struttura di un circuito CMOS che implementi una generica funzione logica

è visualizzata in figura 5. Essa è essenzialmente composta di due reti, una

di pull-up ed una di pull-down le quali devono essere mutualmente esclusive,

non devono cioè mai condurre contemporaneamente (da qui il nome di logica

complementare).

4

V1

V2

V3

Vn

PULL

UP

Y

V1

V2

V3

Vn

PULL

DOWN

Figura 5: Schema di un generico circuito CMOS

Per progettare le due reti è sufficiente seguire tre semplici regole pratiche che possono essere derivate direttamente dall’analisi delle tre porte logiche

elementari condotte nei paragrafi precedenti:

• La tecnologia CMOS permette di realizzare direttamente solo funzioni

negate (not, nand, nor). Il problema può ovviamente essere ovviato inserendo un ulteriore inverter in cascata alla funzione logica stessa. Questo

ovviamente comporta un costo aggiuntivo.

• Per realizzare un’operazione di and si dovranno porre dei transistor NMOS

in serie (uno per ogni operando) nel ramo di pull-down e lo stesso numero

di transistor PMOS in parallelo nel ramo di pull-up.

• Per realizzare un’operazione di or si dovranno porre dei transistor NMOS

in parallelo (uno per ogni operando) nel ramo di pull-down e lo stesso

numero di transistor PMOS in serie nel ramo di pull-up.

6

Esercizio

Allo scopo di meglio chiarire quanto detto fin’ora, consideriamo un semplice

esempio. Si progetti un circuiti CMOS che realizzi la seguente funzione logica:

Y = (A + B) · (C + D) + E

5

A

C

B

D

E

Y

A

B

E

C

D

Figura 6: Esempio: Y = (A + B) · (C + D) + E

Poiché, come detto, in tecnologia CMOS si possono solo reealizzare funzioni

negate, noi saremo in grado di realizzare la funzione

Y = (A + B) · (C + D) + E

e poi dovremo porre un inverter in cascata.

Seguendo le regole descritte in precedenza sarà semplice ottenere il circuito

di fugura 6.

6