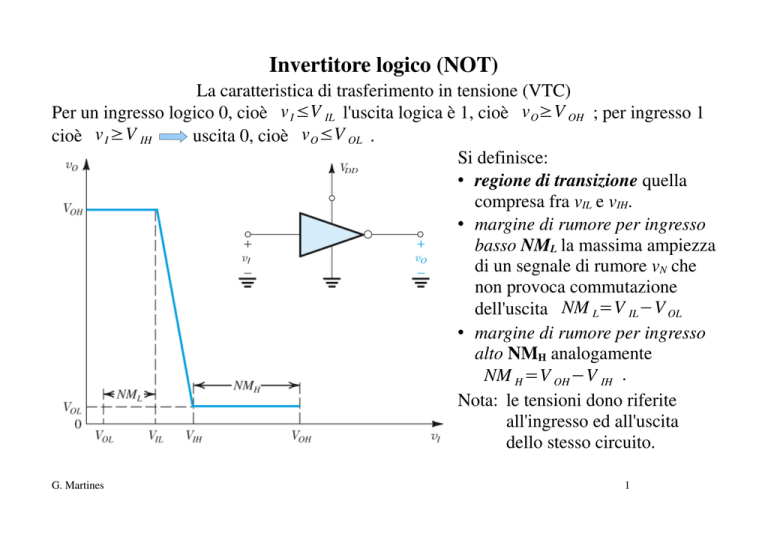

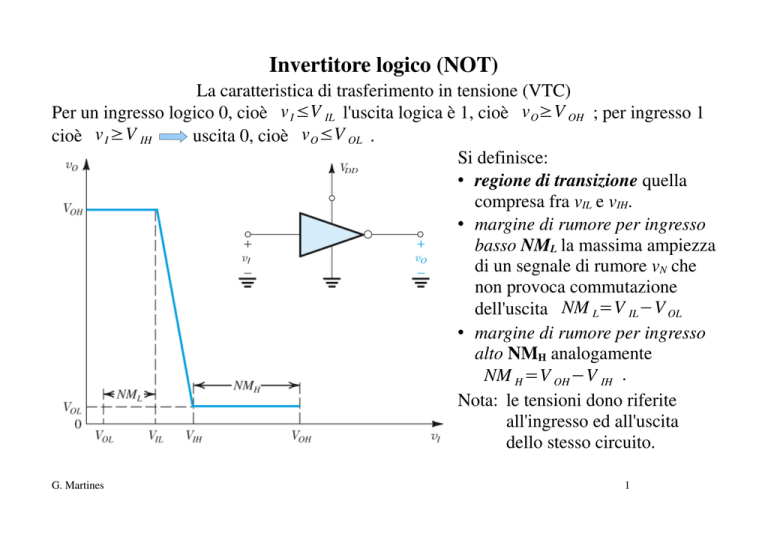

Invertitore logico (NOT)

La caratteristica di trasferimento in tensione (VTC)

Per un ingresso logico 0, cioè v I ≤V IL l'uscita logica è 1, cioè v O≥V OH ; per ingresso 1

cioè v I ≥V IH

uscita 0, cioè v O ≤V OL .

Si definisce:

• regione di transizione quella

compresa fra vIL e vIH.

• margine di rumore per ingresso

basso NML la massima ampiezza

di un segnale di rumore vN che

non provoca commutazione

dell'uscita NM L=V IL V OL

• margine di rumore per ingresso

alto NMH analogamente

NM H =V OH V IH .

Nota: le tensioni dono riferite

all'ingresso ed all'uscita

dello stesso circuito.

G. Martines

1

Esempio di Invertitore logico MOS

La trans-caratteristica di uno stadio CS approssima la VTC di un invertitore.

La regione di transizione coincide con il funzionamento in regione di saturazione.

G. Martines

2

Invertitore logico

Definizione delle soglie e degli altri valori critici

• VIL e VIH sono definiti come i

punti cui corrisponde una

pendenza -1 della VTC.

• VM, la tensione di soglia

logica corrisponde alla

condizione v I =v O sulla

VTC e si considera il punto

in cui l'invertitore cambia

stato

• Immunità al rumore si

definisce il valore minimo

dei margini di rumore

G. Martines

3

VTC di un inverter MOS a carico resistivo

si noti che, in base alle definizioni, la VIL è in regione di saturazione e VIH in regione di

triodo.

G. Martines

4

Caratteristica di trasferimento in tensione (VTC)

di un inverter logico ideale

G. Martines

5

Figure di merito dell'inverter

Se il punto di commutazione dell'uscita è

l'istante in cui la tensione in uscita

raggiunge il 50% della sua escursione,

allora il tempo di propagazione tPHL e quello

tPLH sono mostrati con riferimento ad un

segnale di ingresso ideale. Si definisce:

• tempo di propagazione:

t PLH +t PHL

tP=

2

• massima frequenza di commutazione

1

f max =

2t p

• prodotto ritardo-potenza (power-delay

product) PDP=P D t P

• prodotto ritardo-energia (energy-delay

2

product) EDP=CV DD t P /2

G. Martines

6

Misura dei tempi di propagazione

spesso come generatore del segnale di ingresso si usa una porta della stessa famiglia logica

G. Martines

7

Inverter logico con singolo interruttore controllato in tensione

La rete di pull-up (PUN) è costituita dalla resistenza R, la rete di pull-down (PDN) da un

interruttore controllato in tensione con resistenza Ron quando è chiuso.

Il circuito consuma potenza statica quando l'uscita è bassa.

G. Martines

8

Circuiti equivalenti per il funzionamento dinamico

a) per la transizione low-high:

✗ C rappresenta l'insieme delle capacità associate agli

ingressi delle porte connesse all'uscita dell'inverter che

deve caricarsi perché la tensione di uscita possa passare

da VOL a VOH.

✗ RPU è la resistenza equivalente della rete di pull-up

dell'inverter.

b) per la transizione high-low:

✗ C rappresenta la capacità equivalente che deve caricarsi

perché la tensione di uscita possa passare da VOH a VOL.

✗ RPD è la resistenza equivalente della rete di pull-down

dell'inverter.

G. Martines

9

Funzionamento dinamico dell'inverter con singolo interruttore

G. Martines

10

Inverter logico con doppio interruttore controllato in tensione

La rete di pull-up è costituita da un interruttore controllato in tensione che si chiude

quando vI è bassa. La rete di pull-down è costituita da un interruttore controllato in

tensione che si apre quando vI è bassa.

G. Martines

11

Invertitore CMOS

G. Martines

12

Funzionamento inverter CMOS con ingresso alto

G. Martines

13

Funzionamento inverter CMOS con ingresso basso

G. Martines

14

Caratteristica di trasferimento in tensione dell'inverter CMOS

G. Martines

15

Corrente nell'inverter CMOS

G. Martines

16

Classificazione gerarchica dei circuiti logici

G. Martines

17

Gli invertitori ripristinano il segnale digitale

G. Martines

18

Le famiglie logiche attualmente più diffuse

G. Martines

19

Porte logiche elementari

Simboli e tabelle di verità

G. Martines

20

Realizzazione porta NOR con rete di pull-up resistiva e interruttori

l'interruttore è chiuso quando la relativa variabile di controllo è vera (1)

G. Martines

21

Rete di pull-down CMOS per una porta NOR

Equivale a quella con interruttori; il transistore conduce quando il gate è al livello alto di

tensione. L'uscita è a livello basso se almeno uno dei transistori conduce.

Ricorda che Ȳ = A+ B equivale a Y = A+ B

G. Martines

22

Rete di pull-up CMOS per una porta NOR

Il transistore conduce quando il gate è al livello basso di tensione. Y è a livello alto solo se

entrambi i transistori conducono.

̄

Ricorda la legge di De Morgan: A+ B= ̄A B

G. Martines

23

Struttura base delle porte logiche elementari CMOS

La rete di pull-up contiene transistori MOS a canale P

mentre quella di pull-down contiene transistori MOS a

canale N.

Nell'esempio si considera una porta logica a tre ingressi.

Se si considera una porta logica con un solo ingresso si

ottiene il NOT CMOS.

I simboli più utilizzati per i MOSFET nei circuiti digitali

G. Martines

24

Porta NOR CMOS a due ingressi

G. Martines

25

Realizzazione porta NAND con rete di pull-up resistiva e interruttori

l'interruttore è chiuso quando la relativa variabile di controllo è vera (1)

G. Martines

26

Rete di pull-down CMOS per una porta NAND

Equivale a quella con interruttori; il transistore conduce quando il gate è al livello alto di

tensione. L'uscita è a livello basso solo se entrambi i transistori conducono.

Ricorda che Ȳ = A B equivale a Y = A B

G. Martines

27

Rete di pull-up CMOS per una porta NAND

Il transistore conduce quando il gate è al livello basso di tensione. Y è a livello alto se

almeno uno dei transistori conduce.

̄

A+ B

Ricorda la legge di De Morgan: A B= ̄

G. Martines

28

Porta NAND CMOS a due ingressi

G. Martines

29

Esempio di realizzazione di

una Rete Combinatoria

Rete a quattro ingressi ed una uscita

G. Martines

30