ESERCIZI II PROVA IN ITINERE di SISTEMI ELETTRONICI -2011-2012

1) Progettare la porta logica CMOS (modello interruttore con resistenza in serie) che

implementa la seguente funzione e calcolare il tempo di propagazione con fan out uguale

a 20, sapendo che la tensione di alimentazione è uguale a 5V, che la capacità di ingresso

delle singole porte logiche a cui è collegata la porta logica oggetto dell’esercizio è CT=

100fF e che la resistenza di on del modello CMOS è Rn= Rp =5KΩ.

___________

Y= A·B+(C·D+E)

a) Definire e valutare analiticamente e numericamente il tempo di propagazione

della porta logica, riportando e commentando i passaggi per arrivare

all’espressione finale.

b) Definire il fan out di una porta logica in generale.

2) Progettare la porta logica CMOS (modello interruttore con resistenza in serie) che

implementa la seguente funzione e dimensionare la resistenza prevista nel modello in

modo che il tempo di propagazione sia minore o uguale a 10 ns con fan out uguale a 30,

sapendo che la tensione di alimentazione è uguale a 5V e che la capacità di ingresso delle

singole porte logiche a cui è collegata la porta logica oggetto dell’esercizio è CT= 200fF.

___________

Y= A+B+(C·D·E)

Dimostrare simbolicamente la formula che esprime la potenza dinamica per la carica e

scarica della capacità di carico nella porta logica e trovarne il valore numerico,

supponendo che la tensione di uscita vari con una frequenza operativa massima uguale a

30MHz e sapendo, come suddetto, che la tensione di alimentazione è 5V e CL=6 pF.

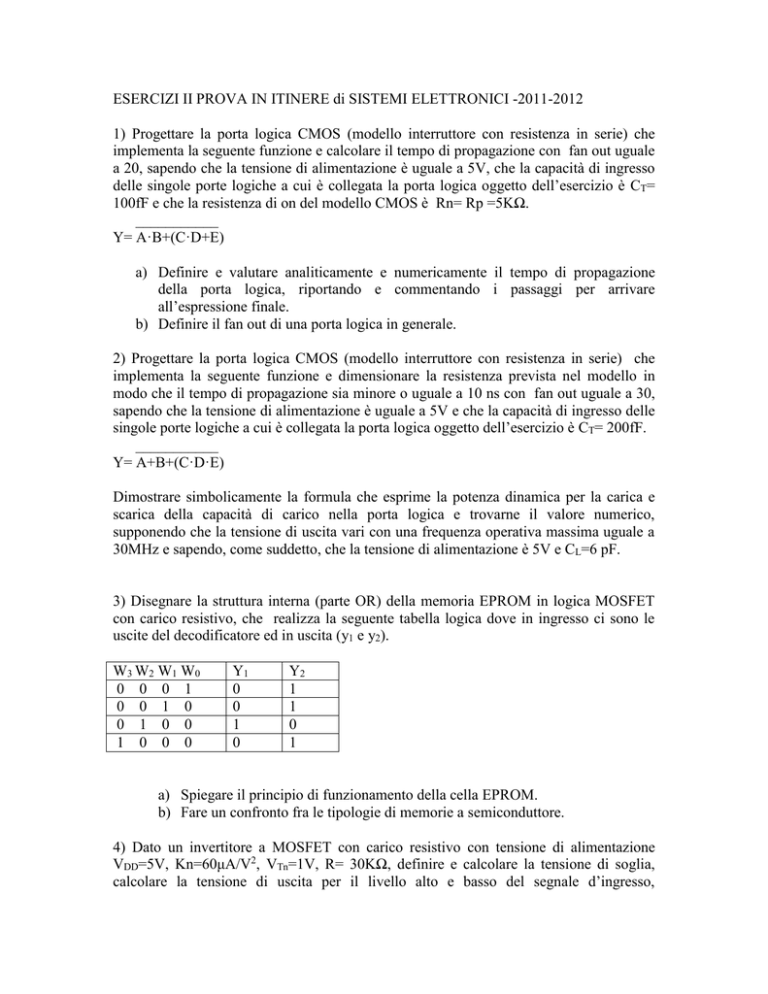

3) Disegnare la struttura interna (parte OR) della memoria EPROM in logica MOSFET

con carico resistivo, che realizza la seguente tabella logica dove in ingresso ci sono le

uscite del decodificatore ed in uscita (y1 e y2).

W3 W2 W1 W0

0 0 0 1

0 0 1 0

0 1 0 0

1 0 0 0

Y1

0

0

1

0

Y2

1

1

0

1

a) Spiegare il principio di funzionamento della cella EPROM.

b) Fare un confronto fra le tipologie di memorie a semiconduttore.

4) Dato un invertitore a MOSFET con carico resistivo con tensione di alimentazione

VDD=5V, Kn=60μA/V2, VTn=1V, R= 30KΩ, definire e calcolare la tensione di soglia,

calcolare la tensione di uscita per il livello alto e basso del segnale d’ingresso,

individuare e confrontare i margini di rumore per il livello alto e basso. Definire e

calcolare in forma analitica il tempo di propagazione con il supporto del metodo grafico.

Definire e trovare il fan out dell’invertitore suddetto nel rispetto di un tempo di

propagazione tp≤ 50 ns, sapendo che la capacità di ingresso delle singole porte logiche a

cui l’uscita dell’invertitore è collegata è CT=1pF; stimare la frequenza massima

utilizzabile nel circuito.

5) Disegnare una cella RAM ad un solo transistor, descrivere la fase di lettura e trovare

l’espressione della tensione sulla linea di bit quando nella cella è memorizzato un 1

logico (4V) e quando è memorizzato uno 0 logico (0V). Si supponga in questo caso che

l’amplificatore di rinfresco non sia presente e si consideri CM=55fF, CL=20pF.

6) Progettare la porta logica CMOS (modello interruttore con resistenza in serie) che

implementa la seguente funzione e dimensionare le resistenze previste nei modelli del

MOSFET n e del MOSFET p, non necessariamente uguali, in modo che i tempi di

propagazione HL e LH sia uguali –si consideri il caso peggiore-, sapendo che la tensione

di alimentazione è uguale a 5V e che la capacità di carico della porta logica oggetto

dell’esercizio è CL= 10pF.

________________

Y= A·B·C+(D·E+F)+G

Calcolare il tempo di propagazione (esiste un grado di libertà, scegliere arbitrariamente il

valore). Indicare il criterio per determinare la frequenza massima dei segnali di ingresso

alla porta e calcolarla.

7) Un segnale analogico compreso tra 0 e 10 V con frequenza massima uguale a 20 KHz

deve essere digitalizzato con un errore di quantizzazione minore di 0.5 mV.

Determinare quanti bit deve avere il convertitore analogico digitale e la frequenza

minima del circuito campionatore.