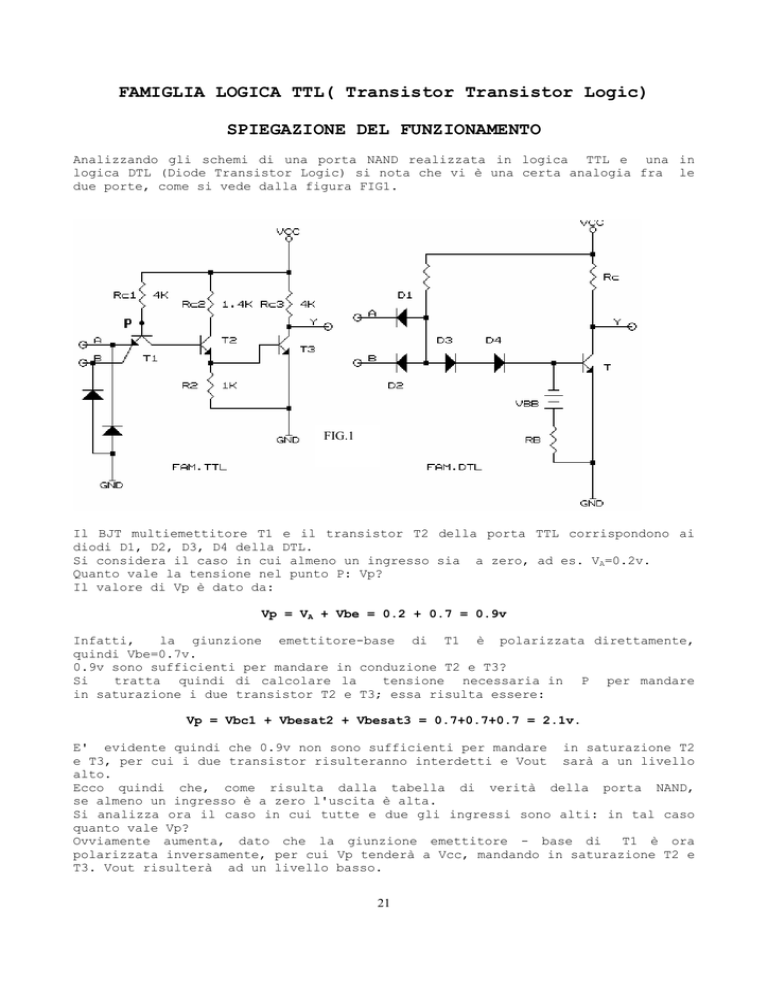

FAMIGLIA LOGICA TTL( Transistor Transistor Logic)

SPIEGAZIONE DEL FUNZIONAMENTO

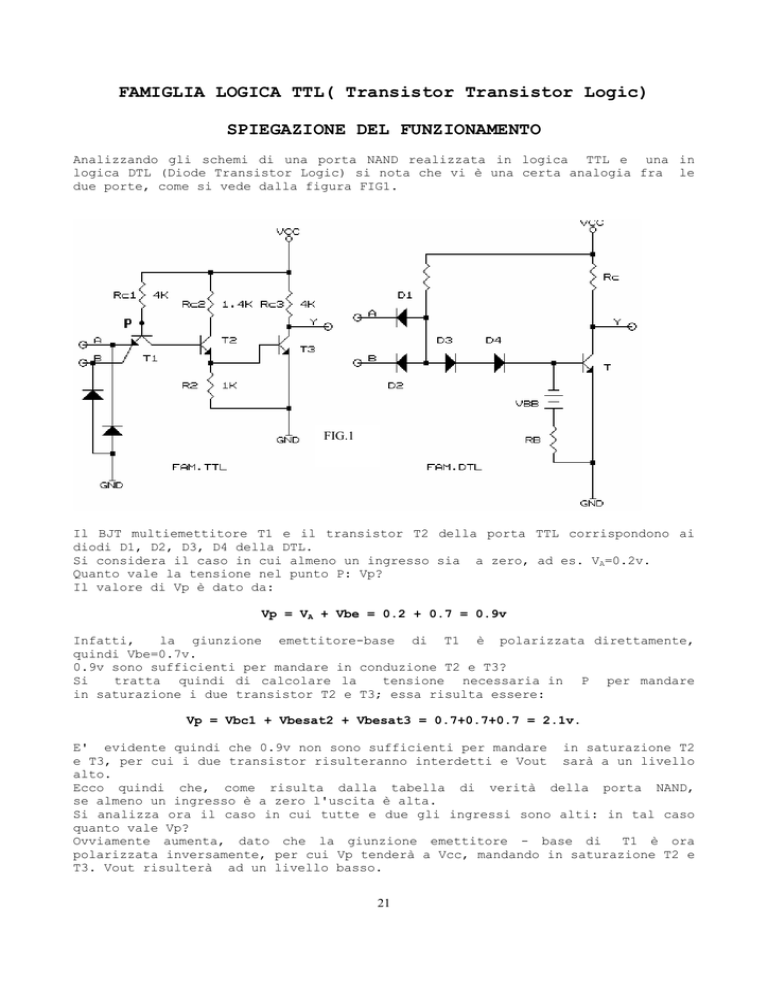

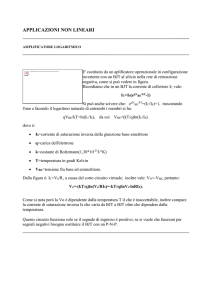

Analizzando gli schemi di una porta NAND realizzata in logica TTL e una in

logica DTL (Diode Transistor Logic) si nota che vi è una certa analogia fra le

due porte, come si vede dalla figura FIG1.

FIG.1

Il BJT multiemettitore T1 e il transistor T2 della porta TTL corrispondono ai

diodi D1, D2, D3, D4 della DTL.

Si considera il caso in cui almeno un ingresso sia a zero, ad es. VA=0.2v.

Quanto vale la tensione nel punto P: Vp?

Il valore di Vp è dato da:

Vp = VA + Vbe = 0.2 + 0.7 = 0.9v

Infatti,

la giunzione emettitore-base di T1 è polarizzata direttamente,

quindi Vbe=0.7v.

0.9v sono sufficienti per mandare in conduzione T2 e T3?

Si

tratta quindi di calcolare la

tensione necessaria in P per mandare

in saturazione i due transistor T2 e T3; essa risulta essere:

Vp = Vbc1 + Vbesat2 + Vbesat3 = 0.7+0.7+0.7 = 2.1v.

E' evidente quindi che 0.9v non sono sufficienti per mandare in saturazione T2

e T3, per cui i due transistor risulteranno interdetti e Vout sarà a un livello

alto.

Ecco quindi che, come risulta dalla tabella di verità della porta NAND,

se almeno un ingresso è a zero l'uscita è alta.

Si analizza ora il caso in cui tutte e due gli ingressi sono alti: in tal caso

quanto vale Vp?

Ovviamente aumenta, dato che la giunzione emettitore - base di

T1 è ora

polarizzata inversamente, per cui Vp tenderà a Vcc, mandando in saturazione T2 e

T3. Vout risulterà ad un livello basso.

21

Sarà quindi sufficiente dimensionare Rc1 in modo che in P vi siano almeno 2,3v,

in modo che sia garantita una corrente sufficiente per la saturazione dei

transistor.

Dal funzionamento della porta risulta evidente la sua analogia con la porta

DTL, allora che differenza c'è fra le due famiglie?

La novità essenziale introdotta dalla logica TTL sta nel fatto che quando gli

ingressi A o B commutano da 1 a 0,

il

BJT T1 si porta con la JBE dalla

polarizzazione inversa alla diretta con JBC sempre polarizzata inversamente

quindi transita

velocemente attraverso

la zona

attiva

e

in

questa

situazione, avendo un elevato valore della corrente di collettore, risucchia

tutta le cariche addensate nella base di T2 e T3 che nel frattempo commutano

dalla saturazione all'interdizione, riducendo così notevolmente i loro tempi

di immagazzinamento, mandandoli quindi prima in interdizione.

E' quindi quest'intervento di T1 che assicura alla porta TTL

la maggiore

velocità tra le logiche di tipo saturato (nel senso che i BJT lavorano in

saturazione).

Al circuito vengono poi aggiunti su ogni ingresso dei

diodi con l'anodo

collegato a massa, utili

nel caso in cui agli ingressi siano presenti degli

spike di tensione negativi, limitandoli ad un valore di sicurezza.

TTL TOTEM POLE

All'ingresso di una qualsiasi porta si hanno delle capacità parassite dovute ai

diodi, al BJT e ai collegamenti (FIG2).

FIG.2

Se ho più porte in cascata il primo NAND vede in uscita questa capacità. Se

Vout va ad es. da 1 a 0 il transistor T3 entra in saturazione, la capacità si

scarica attraverso il transistor T3 saturo che offre resistenza molto bassa. La

costante di tempo di scarica del condensatore è in tal caso molto piccola e non

crea pertanto disagi. Per quanto riguarda invece la commutazione da 0 a 1 il

transistor T3 entrerà in interdizione e la capacità si caricherà attraverso la

resistenza Rc3 (indicata generalmente col nome di pull-up passivo, perché

solleva la tensione di uscita con

legge esponenziale). In tal caso la

tensione ai capi della capacità CL passerà dal valore Vcesat

a

Vcc con una

costante di tempo data da :

τ = Rc3 * CL

Questo fenomeno può introdurre tempi di commutazione troppo lunghi, si

deve quindi fare in modo di ridurre il più possibile il tempo di carica di CL

diminuendo appunto la τ .

22

Si potrebbe diminuire la Rc3, ma non si può abbassarla troppo perché quando

T3 è saturo e Vout=0 nel ramo di uscita scorre una corrente che, se troppo

elevata, può creare problemi di dissipazione di potenza oppure portare T3 fuori

dalla saturazione.

Si deve quindi realizzare un circuito in cui, quando T3 è saturo, non scorra

corrente nel ramo di uscita quindi, pur diminuendo la Rc3,

non

sorgano

problemi di dissipazione di potenza o di uscita dalla saturazione.

Il

problema si risolve utilizzando la configurazione TOTEM-POLE (FIG3.),

vediamone il funzionamento:

FIG.3

Si analizza la commutazione in uscita dallo stato 1 a 0: in tal caso T3 passa

dalla interdizione alla saturazione.

In questa situazione occorrere che T4 sia interdetto in modo che nel ramo di

uscita non circoli corrente.

Si verifica ora la veridicità di quanto appena asserito:

- calcolo della tensione nel punto A: VA:

VA = Vcesat2 + Vbesat3 = 0.2 + 0.8 = 1v

- E' sufficiente 1v per mandare in conduzione T4 e D0?

Ovviamente no, occorrerebbero almeno

VA = Vbesat4 + Vd0 + Vout = 0.8 + 0.7 + 0.2 = 1.7v

pertanto

T4

e

D0 sono interdetti; si sottolinea l'importanza di

D0 che

garantisce l'interdizione di T4.

Si considera ora il caso in cui l'uscita passa da 0 a 1; in tal caso si è già

visto che T2 e T3 sono interdetti, accade però che Vout non va immediatamente

a 1 ma impiega un certo tempo dovuto all'inerzia del condensatore CL.

Ora avendo T2 in interdizione si ha che il punto A tende a Vcc per cui T4 e

D0 iniziano a condurre.

23

Si è già visto che in Va sono sufficienti 1,7v per mandare in conduzione sia

T4 che Do.

Ora quindi T4 fornisce corrente a CL, che può quindi iniziare a caricarsi,

portando Vout a 1,con una costante di tempo τ pari a :

τ = Cl(Rc3 + Rsat4 + RD0)

In questo caso la τ risulta più piccola che nella configurazione precedente.

Infatti ora Rc3 può essere diminuita, in genere viene presa intorno ai 100Ω,

inoltre la resistenza del

BJT e del diodo in conduzione sono

molto

piccoli, praticamente trascurabili rispetto a Rc3.

Come già accennato,

non si hanno problemi di dissipazione di potenza; infatti

T4

risulta

sempre interdetto, tranne che

nel breve momento in cui deve

caricare CL , dopo di che s'interdice di nuovo.

Una volta caricata CL la tensione in uscita aumenta e

la VAC non è più

sufficiente a mantenere T4 e Do in conduzione.

Rc3 può essere diminuita ma non oltre un certo limite, perché durante i

transitori dei BJT vi è un attimo in cui conducono entrambi(mentre l'uno

entra in conduzione l'altro non si è ancora interdetto). In questa situazione

passa corrente nel ramo di uscita, che può produrre danni e che quindi deve

essere limitata da Rc3.

Questo è il motivo per cui in questa famiglia nonostante gli accorgimenti

adottati, si avranno comunque problemi alle alte frequenze.

Con questo tipo di configurazione si ottiene un'impedenza di uscita pari a

qualche decina di Ω (con conseguente aumento del FAN-OUT rispetto alla DTL).

TTL SCHOTTKY

Si può aumentare ulteriormente la velocità di commutazione di questa famiglia

inserendo BJT di tipo Schottky. Questo tipo di BJT è realizzato come in fig.4:

FIG.4

Come si può vedere fra base e collettore viene collegato un diodo Schottky che

ha il compito di non far mai raggiungere al BJT la piena saturazione.

Infatti avendo una tensione di soglia molto inferiore a un comune diodo,

0.35v, esso

inizia a condurre prima

che

la

base diventi

fortemente

positiva, portando verso il

collettore l'eccesso di carica accumulata in

base durante la saturazione del BJT. Ciò diminuisce fortemente il tempo di

immagazzinamento, quindi il tempo di commutazione del componente.

Vi è però l'inconveniente che aumenta la Vcesat = 0.5v, peggiorando l'immunità

al rumore della porta. Per aumentare ulteriormente la velocità della porta

s'inserisce al posto di T4 un Darlington (elevato guadagno), in modo da

24

aumentare la corrente di uscita e velocizzare la carica di CL (FIG5).Viene anche

inserita una rete squadratrice con un BJT, per rendere simmetrico il segnale in

uscita, in tal modo infatti il BJT inserito crea un ramo a bassa impedenza

attraverso cui scaricare velocemente la base del transistor Q3 e quindi

velocizzare la commutazione da 0 a 1.

FIG.5

Q1

Q4

Q2

Q6

Q3

Q5

Per diminuire la dissipazione di potenza si è realizzata la TTLLS (low Schottky)

che ha resistenze di valore più elevato e tempi di commutazione più alti

rispetto alla TTLS(FIG.6).

FIG.6

Vi sono poi anche la Fam. TTLALS e TTLAS che usano tecnologie avanzate per quel

che riguarda l'isolamento dei componenti ( Tecnologia Isoplanare ).

25

SCHEMI DELLE PORTE LOGICHE TTL

SPIEGAZIONE TTL - AND

TAB. DI VERITA'

A

0

0

1

1

B OUT

0 0

1 0

0 0

1 1

Se A o B sono uguali a 0 (Vcesat=0,2v di una porta precedente), Q2 e Q3

rimangono interdetti perchè il potenziale nel punto P non è tale da garantirne

la saturazione. La Vp dovrebbe infatti essere ( come nel caso della NAND) 2.1V.

D3 entra in conduzione e invia corrente alla base di Q4 saturandolo, così come

viene mandato in saturazione Q6 mentre Q5 rimane interdetto, per cui Y=0.

Se A e B sono entrambi a 1, Vp si alza e si porta ad un valore prossimo a Vcc

per cui Q2 e Q3 vanno in saturazione . Il potenziale sulla base di Q4 è pari

alla Vcesat di Q3 ed è quindi troppo basso per mandare Q4 in saturazione che

rimane quindi interdetto come Q6, di conseguenza il potenziale sulla base di Q5

si alza mandandolo in saturazione quindi Y=1. (vedi FIG.7)

FIG.7

Q1

Q2

Q4

Q5

D0

Q6

D1

D2

Q3

26

SPIEGAZIONE TTL - NOR

TAB. DI VERITA'

A

0

0

1

1

B OUT

0 1

1 0

0 0

1 0

Se A e B sono entrambi uguali a 0 (Vcesat = 0.2 porta precedente), sulla base di

Q1

e di Q2 ci sono 0,6v, tale tensione è insufficiente per mandare in

saturazione Q3 e Q4, i quali rimangono interdetti, così come Q6. Si alza quindi

la tensione sulla base di Q5 che tende a Vcc, tensione che ne assicura la

saturazione , per cui Y=1.

Se A o B o entrambi sono uguali a 1 la tensione sulla base di Q1 e Q2 si alza

tendendo a Vcc mandando in saturazione Q3 e Q4 che a loro volta mandano in

saturazione Q6, di conseguenza la tensione sulla base di Q5 si abbassa

portandolo in interdizione quindi Y=0.(vedi FIG.8)

FIG.8

Circuito di una porta NOR TTL

27

SPIEGAZIONE TTL - OR

TAB. DI VERITA'

A

0

0

1

1

B OUT

0 0

1 1

0 1

1 1

Se entranbi gli ingressi A e B sono a 0 (Vcesat = 0,2v di una porta precedente),

la tensione sulla base di Q1 e Q2 è 0,6v, tensione insufficiente a mandare in

saturazione Q3 e Q4 che rimangono quindi interdetti come Q5. Q6 invece viene

mandato in saturazione attraverso il ramo contenente R3 e D3 e a sua volta manda

in saturazione Q8 mentre Q7 è interdetto, per cui Y=0.

Se A=0 e B=1 la tensione sulla base di Q1 è 0.6v per cui Q3 è interdetto e Q4 e

Q5 vanno in saturazione.Q6 è interdetto perché ha in base una tensione di 0.2v,

quindi rimane interdetto anche Q8.

La tensione sulla base di Q7 si alza

mandandolo in saturazione per cui Y=1.

Se A=1 e B=0 la tensione sulla base di Q2 è 0.6v per cui Q4 rimane interdetto e

Q3 e Q5 vanno in saturazione mantre Q6 rimane interdetto come Q8. Q7 viene

mandato in saturazione allora Y=1.

Se A=B=1 la tensione sulla base di Q1 e Q2 si alza tendendo alla Vcc per cui Q3

e Q4 vanno in saturazione come Q5.

La tensione sulla base di Q6 è troppa bassa e Q6 rimane interdetto come Q8. Si

alza invece la tensione sulla base di Q7 che si satura per cui Y=1.(vedi FIG.9)

FIG.9

Circuito di una porta OR TTL

28

AND CABLATO O WIRE-AND

CONFIGURAZIONI SPECIALI

Si

tratta

di un particolare collegamento. Consiste nel collegare tra loro

tramite un nodo le uscite di più porte logiche, ottenendo come risultato l'AND

fra le uscite stesse. Si prendono

le uscite di

due

porte NAND realizzate

tramite la prima configurazione analizzata della fam. TTL e si collegano

insieme tramite un nodo (FIG10).

FIG.10

E' facile verificare che se si ha y1=y2=1 allora sarà anche y=1 e se y1=y2=0

allora si avrà y=0.

Se si ha poi una delle uscite a zero e l'altra a uno, ad esempio y1=0 e y2=1

accade che il transistor T3 è in saturazione mentre T3' è interdetto, per cui

T3 cortocircuiterà T3', portando l'uscita y a zero.

Questo

non

è

altro che il comportamento di una

porta

AND

in logica

positiva oppure di una porta OR in logica negativa.

Con questo tipo di collegamento quindi si può risparmiare una porta logica.

Vi è però un problema e cioè questa soluzione non è applicabile ad una porta

logica TTL con uscita a totem-pole.

29

Si colleghino due porte con uscita a totem-pole come in FIG.11.:

FIG.11

Si può verificare facilmente che nel caso in cui y1=0 e y2=1 nei BJI T3 e T4',

entrambi saturi, per la durata della carica di CL scorre una corrente che vale:

I = (Vcc - VcesaT4' - VDo - VcesaT3)/Rc3'= (5-0.2-0.7-0.2)/100 =39mA

Tale valore di I va ben oltre il limite sopportabile da un BJT perché y

risulti ad un livello basso. In questo caso T3 rischia di andare in zona

attiva, aumentando quindi la tensione ai suoi capi. Si rischia di cadere in

zona di indeterminazione e vi sono i

anche

problemi

di dissipazione di

potenza. Come risolvere pertanto questo problema? Vedi FIG.12:

FIG.12

30

In tale configurazione il BJT T3 è lasciato senza carico è quindi compito

dell'utilizzatore determinarne il valore e collegarlo esternamente all'uscita.

Per quanto riguarda il valore di Rext i manuali indicano due valori uno min e

uno max. Se si sceglie il valore

più vicino a

Rextmax si avrà un minor

dispendio di energia e quindi una minore dissipazione di potenza ma anche tempi

di commutazione

più lunghi, viceversa se si sceglie un valore prossimo a

Rextmin.

THREE-STATE

Questo tipo

di soluzione permette di eliminare

la

perdita

di velocità

dell'open-collector.

Il three-state è un elemento logico definito da tre stati possibili di

funzionamento:0,1,Z

Questo tipo di elemento ha un ulteriore ingresso detto di abilitazione che se

attivato mette in alta impedenza l'uscita. La realizzazione circuitale per la

porta NAND è evidenziata in fig.13:

Come si può facilmente notare si sono aggiunti due diodi D1 e D2.

Ora se EN=0 (0.2v) D1 e D2 sono in conduzione e la base di T2 e T4 sono pertanto

a 0.9v, tensione insufficiente per far condurre da un lato T2 e T3 e dall'altro

T4 e Do.

Si

avrà

quindi

un uscita equivalente

ad

un

circuito aperto infatti

è

scollegata sia dalla massa

che

dall'alimentazione.

Questo tipo di porta nella situazione OFF può quindi subire il livello logico

imposto da altre porte ad essa

collegate attraverso una linea comune.

Questa

configurazione viene utilizzata per inviare ad es. l'informazione

sul BUS DATI di un qualsiasi sistema a microprocessore.

FIG.13

31

L'ASSORBIMENTO E L'EROGAZIONE DI CORRENTE

NELLE PORTE TTL

Il concetto di assorbimento di corrente, (corrente di Sink IOL) e di erogazione

di corrente (corrente di Source IOH), è già stato introdotto all'inizio di questi

appunti.

Ora avendo acquisito maggiori conoscenze, verrà esaminato più in dettaglio.

In FIG.14 è rappresentata una NOT TTLSTD con uscita totem-pole collegata

all'uscita di un'altra NOT dello stesso tipo.

FIG.14

32

Quando l'uscita della porta pilota si trova allo stato alto (FIG.14a), tale

porta eroga corrente fino ad un valore massimo di IOH=400µΑ a quella di carico.

L'ingresso della porta di carico agisce come un diodo polarizzato inversamente,

quindi non assorbe corrente. In realtà un po’ di corrente scorre, del valore

massimo di IIH=40µA, dovuta alla corrente inversa che scorre nel diodo. Da ciò si

deduce che al massimo la porta può pilotare 10 porte in parallelo sulla sua

uscita(F.O.=10)

Quando l'uscita della porta pilota si trova a livello basso, tale porta assorbe

corrente dal carico (FIG14b). Questa corrente può raggiungere un valore massimo

di 16mA(IOL)ma se la porta è collegata ad una sola altra porta attraverso Q3

della porta pilota scorre una corrente IIL=1,6mA definita dal ramo indicato in

figura, infatti in tal caso il transistor Q3 è saturo.

PARAMETRI DELLE SOTTOFAMIGLIE TTL:

VIH(MIN)

VIL(MAX)

VOH(MIN)

VOL(MAX)

NMH/L

IIH(MAX)

IIL(MAX)

IOH(MAX)

IOL(MAX)

P(mW)Statica

P(mW)100KHz

Fmax(MHz)

pJ(100KHz)

tp(nsec)

Vcc(V)

F.O.H/L

STD

2V

0,8V

2,4V

0,4V

0,4/0,4V

40µA

-1,6mA

-400µA

16mA

10

10

35

100

10

5

10/10

S

2V

0,8V

2,7V

0,5V

0,7/0,3V

50µA

-2mA

-1mA

20mA

20

20

125

57

3

5

20/10

LS

2V

0,8V

2,7V

0,5V

0,7/03V

20µA

-400µA

-400µA

8mA

2

2

40

20

10

5

20/20

33

ALS

2V

0,8V

2,7V

0,5V

0,7/0,3V

20µA

-100µA

-400µA

8mA

1

1

70

4

4

5

20/80

AS

2V

0,8V

2,7V

0,5V

0,7/0,3V

20µA

-0,5mA

-2mA

20mA

8

8

200

13

1,5

5

100/40