Esercizi di

Laboratorio di Segnali e Sistemi

A.NIGRO

Dipartimento di Fisica, Università La Sapienza di Roma

(settembre 2016)

2

Introduzione

Gli esercizi qui raccolti sono stati in massima parte tratti dalle prove in classe proposte agli studenti negli anni

scorsi. Sono quindi abbastanza rappresentativi del tipo di preparazione richiesto per affrontare con successo le

suddette prove. Il grado di difficolta’ di questi esercizi e’ abbastanza variabile; alcuni sono mere applicazioni

di formule o leggi illustrate nel corso delle lezioni in aula, altri sono viceversa un po’ piu’ complessi e mettono

alla prova la capacita’ dello studente di progettare concretamente un piccolo circuito, ovvero di diagnosticare

correttamente il comportamento di un dispositivo elettronico. Ovviamente si raccomanda al lettore di provare

a risolvere per proprio conto ogni problema e, solo dopo, confrontare la propria soluzione con quella riportata

nell’ultimo capitolo.

3

4

Indice

1 Reti lineari

7

2 Circuiti con transistor

11

3 Amplificatori operazionali

21

4 Circuiti logici e Convertitori

33

5 Soluzioni

5.1 Reti . . . . . . . . . . . . .

5.2 Circuiti con transistor . . .

5.3 Amplificatori operazionali .

5.4 Circuiti logici e convertitori

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

5

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

43

43

45

54

65

6

INDICE

+

5V

10k

5k

_

A

10k

5k

Capitolo 1

+

_

10V

Reti lineari

B

Esercizio 4

Costruire un partitore da aggiungere a questo generatore per ottenere una tensione di 5 V con una resistenza

d’uscita di 50Ω

Esercizio 1

Calcolare la resistenza d’uscita del circuito in figura.

50

+

50k

25k

_

10V

+

_

50k

V

50k

Esercizio 5

Trovare il circuito equivalente di Thevenin (visto tra i

punti A e B) della rete riportata in figura.

A

Esercizio 2

Trovare il circuito equivalente di Thevenin (visto tra i

punti A e B) della rete riportata in figura.

5k

5mA

10k

10k

_

10k

5V

A

+

_

+

10k

5V

Esercizio 6

Trovare il circuito equivalente di Thevenin (visto tra i

punti A e B) della rete riportata in figura.

5k

B

10k

10V

+

_

B

5V

_

+

5k

A

_

Esercizio 3

Trovare il circuito equivalente di Thevenin (visto tra i

punti A e B) della rete riportata in figura.

+

5V

10k

B

7

8

CAPITOLO 1. RETI LINEARI

Esercizio 7

La tensione d’uscita del circuito in figura e’ stata misurata con due diversi valori del resistore RL , ottenendo:

Vo = 10V con RL = 10K

Vo = 15V con RL = 100K

Quanto vale la resistenza d’uscita del circuito?

Esercizio 11

Trovare il circuito equivalente di Thevenin (fra i punti

A e B) della rete riportata in figura

A

R1

+

RL

Esercizio 8

Trovare il circuito equivalente di Thevenin (fra i punti

A e B) della rete riportata in figura

5K

_

+

10V

1.7K

+

_

R3

R4

B

A

10K

5K

_

?

R2

Vg

15V

Esercizio 12

Trovare il circuito equivalente di Thevenin (fra i

terminali A e B) della rete riportata in figura.

Valori: Ig = 2mA, R1 = 2K, R2 = 2K, R3 = 1K,

R4 = 2K.

B

A

B

Esercizio 9

Calcolare l’impedenza d’ingresso del circuito in figura

R1

Ig

100k

10k

R3

R4

R2

50

Esercizio 10

Qual e’ la minima impedenza d’ingresso del circuito riportato in figura? Qual e’ la massima impedenza d’uscita (nel momento in cui il generatore d’ingresso e’

connesso)?

Esercizio 13

Trovare il circuito equivalente di Thevenin (fra i

terminali A e B) della rete riportata in figura.

Valori: Ig = 2mA, R1 = 500 Ω, R2 = 500 Ω, R3 = 1K,

R4 = 2K.

A

100nF

R4

R2

50

+

_

10k

R1

Ig

R3

B

9

Esercizio 14

Determinare la risposta del circuito in figura alla

Trovare il circuito equivalente di Thevenin (fra i funzione di ingresso

terminali A e B) della rete riportata in figura.

vi (t) = ku(t)

Valori: Ig = 2mA, R1 = 500 Ω, R2 = 500 Ω, R3 = 1K,

R4 = 2K.

dove u(t) e’ la funzione di Heaviside, utilizzando il

metodo delle trasformate di Laplace.

R

4

R

2

R1

A

R3

Ig

B

Esercizio 15

Determinare la tensione ai capi del generatore ideale di

corrente J.

Dati:

R1 = 100 Ω, R2 = 50 Ω, R3 = 100 Ω

R4 = 200 Ω, R5 = 200 Ω, J = 10 mA

Esercizio 16

Determinare la tensione e la resistenza equivalente di

Thevenin tra i punti B e massa del circuito in figura.

Dati numerici: V1 = 4 V ; V2 = 1 V ; R0 = 50 Ω;

R1 = 100 Ω; R2 = 15 Ω; R3 = 85 Ω;

Esercizio 17

Esercizio 18

Calcolare, utilizzando il teorema di Thevenin, la

tensione d’uscita, Vo , per il circuito in figura.

10

CAPITOLO 1. RETI LINEARI

12V

15k

4k

3k

1k

Capitolo 2

Circuiti con

transistor

100nF

Esercizio 19

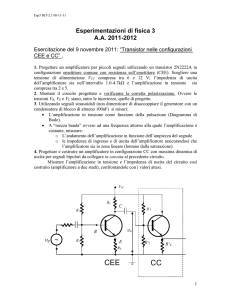

Esercizio 21

Il transistor utilizzato in questo amplificatore ha un La resistenza R è tale per cui il transistor è in saturaguadagno di corrente βF = 100.

zione. Quanto è, approssimativamente, la corrente del

a) Verificare lo stato del transistor, cioè se esso è nella collettore, IC ?

regione attiva, o in saturazione;

b) Stimare la resistenza d’ingresso del circuito.

10V

10V

1k

R

1k

100k

Esercizio 20

Esercizio 22

Trovare il punto di lavoro del transistor (tipo 2N2222A) Scegliere i valori di RE ed RC necessari per ottenere

nel circuito in figura.

un’amplificazione di tensione Av = −5.

11

12

CAPITOLO 2. CIRCUITI CON TRANSISTOR

15V

VCC

RC

RC

9k

Rs

1k

RE

vs

+

_

RE

VEE

Esercizio 25

Si è costruito questo circuito con l’idea di realizzare un

amplificatore con Av = −10. Verificare se il progetto

è corretto (cioè verificare che il transistor è effettivamente nella regione attiva). Qualora ciò non fosse, coEsercizio 23

Nel circuito in figura l’amplificazione di tensione e’ me potremmo modificarlo, per ottenere effettivamente

AV = 8. Calcolare l’ampiezza della tensione d’usci- l’amplificazione di tensione di progetto?

ta v0 , quando il segnale del generatore d’ingresso, vs , Nota: Il generatore di tensione è fisso e non può essere

modificato.

ha un’ampiezza di 300 mV.

10V

500

vs

1k

32k

10k

8k

1k

10

Av

Esercizio 24

Si vuole realizzare un amplificatore ad emettitore comune, con amplificazione di tensione AV = −5 e con

doppia alimentazione, che possa quindi essere utilizzato senza capacitore d’ingresso. Inoltre si richiede

VCE ≥ 5V . Si hanno a disposizione due alimentatori indipendenti in grado di fornire tensioni variabili

tra 0 e +15 V e tra 0 e –15V.

Trovare un possibile insieme di valori di RC , RE , VCC

e VEE adatti a fornire le prestazioni richieste.

Esercizio 26

Calcolare i valori di RB ed RC necessari per realizzare un amplificatore con amplificazione di tensione

Av = −200, sapendo che il transistor ha un guadagno

di corrente βF = 150.

Qual è il massimo segnale sinusoidale d’ingresso che è

possibile amplificare senza distorsione?

Nota: considerare il transistor a temperatura ambiente

13

15V

10V

RC

RB

14.4k

R

T1

T2

Esercizio 27

E’ stato costruito un amplificatore ad emettitore comune come in figura. Trovare i valori di IC e VCE e stimare, con ragionevoli approssimazioni, l’amplificazione di Esercizio 29

tensione per piccoli segnali. Valori di progetto:

Nell’amplificatore in figura il generatore di corrente

della maglia d’uscita è dato da i0 = gm vi . Il segnaVCC = 10 V

le d’ingresso proviene da un generatore di corrente is .

RC = 2.2k

Calcolare il valore della tensione d’uscita vo , sapendo

RB = 100k

che:

Si assuma inoltre βF = 100.

is = 10 µA; Rs = 100k; Ri = 100k; gm = 0.01 Ω−1 ;

Ro = 10k.

VCC

RB

RC

is

Esercizio 28

Due transistori sono montati come in figura. Calcolare, con ragionevole approssimazione, il valore della

corrente di collettore del transistore T2 (si noti che essa non dipende dal valore di R). Si ipotizzi che i due

transistori siano identici ed alla stessa temperatura.

Rs

vi

Ri

io

Ro

vo

Esercizio 30

Nell’amplificatore in figura vi è stato un difetto di montaggio: il resistore tra base e massa non fa contatto.

Determinare lo stato del transistor in questa situazione anomala, sapendo che il parametro βF del transistor

è pari ad almeno 100.

14

CAPITOLO 2. CIRCUITI CON TRANSISTOR

12V

15V

5k

9k

10nF

1k

1k

vi

Esercizio 31

E’ stato costruito un amplificatore ad emettitore comune come in figura. Trovare i valori di IC e VCE e stimare, con ragionevoli approssimazioni, l’amplificazione di

tensione per piccoli segnali. Valori di progetto:

VCC = +15 V

RC = 8.2k

R1 = 68k

R2 = 6.8k

400k

4k

vo

Esercizio 33

In figura è rappresentato un amplificatore a due stadi.

Determinare il punto di lavoro statico dei due transistor. Costruire il circuito equivalente con parametri h;

determinare l’amplificazione di tensione a media frequenza (cioè a frequenza per cui i due capacitori sono

assimilabili a dei corti circuiti).

VCC

R1

RC

R2

Esercizio 32

Determinare il punto di lavoro statico del transistor.

Costruire il circuito equivalente con parametri h; calcolare l’amplificazione di tensione a media frequenza e

la frequenza di taglio dovuta al capacitore d’ingresso.

(Il transistor ha un guadagno di corrente hf e = 100)

Esercizio 34

Nell’amplificatore in figura il segnale d’ingresso viene

inviato all’emettitore e l’uscita prelevata dal collettore. Calcolare l’amplificazione di tensione per frequenze

medio - alte (f > 105 Hz). Si faccia l’ipotesi che il

transistor sia a temperatura ambiente.

15

20V

+15V

930k

10k

vo

Rs

vs

100nF

vi

100nF

250k

vo

+

_

2k

-15V

3.3k

Esercizio 37

Calcolare (approssimativamente) i valori statici delle

correnti e delle tensioni relative ai due transistori (supposti identici) che costituiscono l’amplificatore differenziale riportato nel disegno. Stimare il valore del CMRR

di questo circuito.

+12V

Esercizio 35

Determinare lo stato del transistor in figura e calcolare

la corrente di collettore.

10k

10k

+5V

5K

470

470

10k

-12V

2k

-5V

Esercizio 38

Calcolare l’impedenza d’ingresso del circuito in figura,

sapendo che AV = −100.

1M

1k

1k

A vvi

Esercizio 36

Nell’inseguitore di tensione in figura vi è stato un difetto di montaggio: la linea di alimentazione del collettore

non fa contatto. Determinare lo stato del transistor in

questa situazione anomala, e quale tensione verrà os- Esercizio 39

servata in uscita (vs è un segnale sinusoidale di 1V Determinare il punto di lavoro statico dell’amplificatopicco-picco e Rs = 50Ω)

re in figura. Calcolare la frequenza di taglio del passa

vi

100k

16

CAPITOLO 2. CIRCUITI CON TRANSISTOR

VCC

alto d’ingresso e il valore dell’amplificazione di tensione effettiva per piccoli segnali, ovvero il rapporto vo /vs

a media frequenza (cioe’ sopra la suddetta frequenza di taglio). Si supponga il transistor a temperatura

ambiente.

R1

RBB

Valori: VEE = −5 V , VCC = 10 V , RE = 1k, RC = 1k,

Rs = 50 Ω, C = 10 µF

vi

R2

C

Rs

RC

RE

vs

VEE

CB

RE

vo

vo

VCC

Esercizio 40

L’amplificatore in figura e’ costituito da una coppia di

transistor ed e’ il cosiddetto amplificatore Darlington.

Determinare l’amplificazione di corrente per piccoli segnali, ovvero il rapporto tra la corrente d’uscita, io , e

la corrente fornita dal generatore di segnale, is . Per

semplicita’ si puo’ ipotizzare che i due transistor siano

identici.

Esercizio 42

Calcolare il punto di lavoro statico e lo stato dei due

transistor per i due casi:

a) interruttore I chiuso;

b) interruttore I aperto.

Valori: VCC = 9 V , R1 = 129k,R2 = 58k, RC1 = 4.4k,

RE1 = 2.2k, RE2 = 8.kK, βF 1 = βF 2 = 80.

VCC

R1

RC1

T2

T1

VCC

io

RC

R2

iS

RE1

I

RE2

T1

Rs

T2

vs

RE

VEE

Esercizio 41

Determinare l’amplificazione di tensione e la resistenza d’ingresso dell’amplificatore in figura per segnali a

media frequenza, cioe’ quando il capacitore CB puo’

essere assimilato ad un corto circuito.

Valori: VCC = 10 V , R1 = R2 = 10k, RBB = 1k,

RE = 1k.

Si assuma anche hf e = 150.

Esercizio 43

In figura e’ mostrato un amplificatore ad emettitore

comune.

1. Determinare il punto di lavoro statico del transistor,

ovvero VBE , VCE , IC ;

2. Calcolare l’amplificazione di tensione per segnali a

media frequenza (ovvero quando l’impedenza di tutti i

capacitori esterni puo’ essere trascurata, cosi’ come le

capacita’ parassite del transistor);

3. Calcolare (anche approssimativamente) la resistenza d’ingresso e la resistenza d’uscita dell’amplificatore

(nella medesima regione a media frequenza).

Valori: VCC = 12 V , RC = 4.7k, RE = 1.2k, RB =

100, βF > 50.

Si assuma che il transistor sia a temperatura ambiente.

17

VCC

RC

RB

vo

vi

Co

Determinare la massima ampiezza di un segnale sinusoidale d’ingresso che tale amplificatore e’ in grado di

amplificare senza distorsione.

Si hanno a disposizione due alimentazioni fisse, VCC =

+10 V , VEE = −10 V .

Si assuma che il transistor sia a temperatura ambiente.

Ci

VCC

RE

RC

CE

vo

vi

1k

Esercizio 44

CE

RE

In figura e’ mostrato un amplificatore a base comune.

1. Determinare il punto di lavoro statico del transistor,

ovvero VBE , VCE , IC ;

VEE

2. Calcolare l’amplificazione di tensione per segnali a

media frequenza (ovvero quando l’impedenza di tutti i

capacitori esterni puo’ essere trascurata, cosi’ come le

capacita’ parassite del transistor).

Esercizio 46

Valori: VCC = 12 V , RC = 1k, RE = 2.2k, R1 = R2 =

Determinare l’espressione della resistenza d’ingresso,

10k, hf e = 100.

Ri , del circuito in figura, in funzione dei parametri dei

Si assuma che il transistor sia a temperatura ambiente.

transistor e di RE .

VCC

VCC

RC

R1

vo

T1

Co

vi

T2

vi

R2

RE

Ci

RE

VEE

Esercizio 45

Progettare un amplificatore ad emettitore comune con

doppia alimentazione e capacita’ di emettitore che abbia una amplificazione di tensione a vuoto (senza carico

esterno) Av = −200.

Determinare il valore di CE in modo che la frequenza

di taglio inferiore, fL , sia di circa 1KHz, ricordando

che

1

fL ≃

2πre CE

Esercizio 47

Calcolare, a media frequenza (ovvero quando l’impedenza dei due condensatori e’ trascurabile) , l’amplificazione di potenza dell’amplificatore in figura, cioe’

il rapporto tra la potenza immessa nel carico RL e la

potenza fornita dal generatore vs .

Si assuma hf e del transistor uguale a 100.

18

Esercizio 48

Calcolare l’amplificazione di tensione complessiva

(a media frequenza) dell’amplificatore a due stadi

riportato in figura.

Si assuma che entrambi i transistor siano a temperatura ambiente e che il loro hf e sia uguale a

100.

(VCC = 10 V ).

Esercizio 49

Per l’amplificatore riportato in figura si trovino valori

opportuni per R1 , R2 , R3 , RC ed RE in modo da rispettare i seguenti vincoli:

a) VCC = 15 V ;

b) tensione tra emettitore e massa VE = 0.1VCC ;

c) IC = 1.5 mA;

d) amplificazione a centro banda (ovvero a frequenze per cui CE è assimilabile a un corto circuito) A =

vout /vin = 25;

e) dinamica del segnale di uscita più grande possibile;

f) corrente del partitore di base IP ≃ 0.5 mA.

Si assuma che il transistor sia a temperatura ambiente.

CAPITOLO 2. CIRCUITI CON TRANSISTOR

Esercizio 50

Determinare il punto di lavoro statico VC ,VB ,VE ,IC dei

due transistor del circuito in figura.

Si assuma che entrambi i transistor sono a temperatura

ambiente e che il loro βF sia uguale a 100.

(VCC = 10 V ).

Esercizio 51

Calcolare l’amplificazione di tensione

Avs =

vo

vs

e la resistenza d’uscita, Ro , per l’amplificatore a due

stadi riportato in figura, a media frequenza (ovvero trascurando l’impedenza dei due capacitori). Si assuma

hf e = 100 per entrambi i transistor.

19

Esercizio 52

Calcolare l’amplificazione di tensione a media frequenza, Av , e la frequenza di taglio, ft , per l’amplificatore

riportato in figura. Si consideri comunque trascurabile

la resistenza Rs .

Esercizio 53

Calcolare l’amplificazione di tensione

Avs =

vo

vs

e la resistenza d’ingresso, Ri , per l’amplificatore

riportato in figura.

Esercizio 54

Determinare la risposta in frequenza del circuito, ovvero le frequenze di taglio e l’amplificazione massima.

Per semplicita’ si consideri comunque trascurabile la

resistenza Rs , e si assuma che hf e > 100.

20

CAPITOLO 2. CIRCUITI CON TRANSISTOR

Esercizio 58

Calcolare il valore di vo per le due possibili posizioni

dell’interruttore.

vi = 1.5 V , VCC = 12 V , VEE = −12 V

Capitolo 3

Amplificatori

operazionali

Esercizio 59

Trovare la risposta del circuito in figura nei due casi:

Esercizio 55

a) interruttore verso massa aperto;

Utilizzando degli amplificatori operazionali realizzare b) interruttore verso massa chiuso.

un circuito in grado di produrre un’uscita

100k

vout = (va + 2vb − 3vc )/3

100k

va

vi

vb

vout

vo

5.1k

vc

Esercizio 56

Realizzare, con un amplificatore operazionale, un circuito che fornisca un’amplificazione A=15, con una resistenza d’ingresso di almeno 20 kOhm. Quale sara’ la

banda passante, nell’ipotesi che il nostro operazionale

ha un prodotto banda x guadagno di 106 ?

Esercizio 57

All’ingresso di questo circuito è inviata un’onda quadra con ampiezza 2V e valor medio 0V . Quale sara’ la

forma della tensione d’uscita?

+1V

Esercizio 60

Qual è l’amplificazione di tensione del circuito riportato in figura? Qual è la sua resistenza d’ingresso?

Se l’operazionale è alimentato con +15V/-15V, qual è

la massima ampiezza di un segnale sinusoidale in ingresso che il circuito è in grado di amplificare senza

distorsione?

470k

vi

+15V

10k

vo

-1V

10k

100k

-15V

Esercizio 61

Trovare la risposta del circuito in figura

21

22

CAPITOLO 3. AMPLIFICATORI OPERAZIONALI

10k

vi

105k

10k

v2

10k

vo

2k

vo

v1

8k

10k

100k

Esercizio 62

Qual è la funzione di trasferimento del circuito riportato in figura? Qual è la sua minima impedenza di

ingresso?

Esercizio 65

Calcolare l’amplificazione di tensione del circuito in

figura.

100k

10nF

Esercizio 66

L’amplificatore in figura è alimentato con 0 e +10V.

Trovare la forma d’onda del segnale di uscita se si inEsercizio 63

L’amplificatore in figura è alimentato con +12 e –12 V. via all’ingresso positivo un segnale sinusoidale con valor

All’ingresso A si applica una tensione costante pari a medio nullo e semi-ampiezza di 1V.

+1 V, mentre all’ingresso B si applica un’onda rettan+10V

golare con valore medio nullo e semi ampiezza 0.5 V.

Qual è la forma d’onda del segnale d’uscita?

+1V

-1V

500k

500k

vA

0V

100k

vo

vB

Esercizio 64

Valutare il Common Mode Rejection Ratio dell’amplificatore differenziale in figura.

Si assuma che

l’operazionale abbia un CMRR intrinseco infinito.

Esercizio 67

Il circuito in figura fornisce un’uscita di tensione linearmente dipendente dalla corrente Is del generatore

di corrente. Scegliere i valori di R ed R’ in modo che

risulti:

V0 = 0V per Is = 50µA

V0 = 5V per Is = 150µA

23

+15V

Esercizio 71

Il circuito in figura dovrebbe teoricamente funzionare da integratore. Quali problemi incontreremmo se

utilizzassimo davvero questo circuito?

R’

R

vo

Is

-15V

Esercizio 68

Un generatore fornisce un segnale vs di ampiezza variabile. Progettare con un amplificatore operazionale

un comparatore in grado di fornire un’uscita di +5V

quando vs > +1V , e un’uscita di 0 V altrimenti. Si

hanno a disposizione due alimentatori rispettivamente

da +10V e –10V.

Esercizio 72

L’operazionale utilizzato in questo circuito ha un prodotto guadagno x banda pari a 107 . Calcolare il guadagno di tensione e la banda passante ottenibile con i

valori usati in figura.

Esercizio 69

Calcolare l’amplificazione di tensione del circuito in

figura

750k

150k

500K

vo

vs

50K

vo

vs

100k

100k

Esercizio 73

Trovare il valore della tensione di uscita v0 del circuito

in figura, in funzione delle due tensioni di ingresso, v1

e v2

470k

100k

Esercizio 70

Il circuito in figura dovrebbe teoricamente fornire un’uscita di 0V. Viceversa, se realizzato effettivamente, si

constaterebbe che l’uscita va in saturazione dopo breve

tempo. Per quale motivo?

vo

v1

v2

47k

47k

Esercizio 74

Dimostrare, nel circuito in figura, che la corrente

IL , circolante nel resistore RL , è proporzionale alla

tensione d’ingresso vi .

24

CAPITOLO 3. AMPLIFICATORI OPERAZIONALI

R’

vi

Esercizio 78

Scegliere dei ragionevoli valori per i resistori R, R′ e

R1 in modo che nel circuito in figura si abbia:

R

v0 = 5(v1 + v2 )

R

R’

RL

R

R’

vo

v1

v2

R1

R2

Esercizio 75

All’ingresso di questo circuito e’ inviata un’onda quadra con ampiezza 3V e valor medio 0V. Quale sara’ la

forma della tensione d’uscita?

Esercizio 79

Il guadagno di tensione ad anello aperto ( in continua)

+1.5V

+10V

di un amplificatore operazionale compensato interna-1.5V

mente viene misurato e si trova il valore di 80 dB. A

100 kHz si trova invece il valore di 40 dB. Stimare il

valore della frequenza di taglio di questo amplificatore.

470k

0V

Esercizio 76

Qual è l’amplificazione di questo circuito in funzione della frequenza del segnale?

Quanto vale

l’amplificazione in continua?

Esercizio 80

Calcolare il guadagno di tensione dell’amplificatore differenziale mostrato in figura (assumendo che i resistori con eguale nome siano identici tra loro e che gli

operazionali utilizzati siano ideali).

v1

R4

20k

2k

R2

vo

4700nF

R3

R1

vo

R2

vs

R3

R4

v2

Esercizio 77

Un generatore vs fornisce una tensione di ampiezza variabile tra 0 e +10V. Con un amplificatore operazionale

realizzare un comparatore in grado di fornire un’uscita

di 0V quando vs > +5V e un’uscita di +5V quando

vs < +5V .

Esercizio 81

Calcolare il guadagno di tensione dell’amplificatore mostrato in figura (assumendo che l’operazionale

utilizzato sia ideale).

25

R1

vo

R

R3

vi

R1

R

R2

R4

R2

R

vi

Esercizio 82

Un amplificatore operazionale ha una slew rate di

60V /µs. Qual è la massima frequenza a cui una sinusoide di 20V (picco – picco) può essere prodotta all’uscita

senza distorsione?

vo

R

Esercizio 86

Qual è la massima frequenza di un’onda triangolare di

20V di ampiezza (picco-picco) che può essere riprodotta senza distorsione da un amplificatore operazionale

con una slew rate di 10V /µs?

Esercizio 83

Il guadagno di tensione ad anello aperto di un amplificatore operazionale compensato internamente viene

misurato e si trova che esso vale 5x103 a 100 kHz e

5x106 a 50 Hz. Stimare il guadagno in continua e la

Esercizio 87

frequenza di taglio di questo amplificatore.

Trovare l’espressione della tensione d’uscita in funzione

delle 4 tensioni di ingresso. (L’operazionale puo’ essere

Esercizio 84

considerato ideale; inoltre si assuma che i 4 resistori R

Calcolare il guadagno di tensione dell’amplificatore dif- sono identici tra loro, cosi’ come i due resistori R’.)

ferenziale mostrato in figura (assumendo che i resistori con eguale nome siano identici tra loro e che

R’

R

l’operazionale utilizzato sia ideale).

v1

R1

R2

v2

v2

R2

RG

v3

vo

v1

R1

R2

v4

R

vo

R

R’

R

R2

Esercizio 85

Calcolare il guadagno di tensione dell’amplificatore mostrato in figura (assumendo che i resistori con eguale nome siano identici tra loro e che gli operazionali

utilizzati siano ideali).

Esercizio 88

Il circuito in figura costituisce un buon generatore di

corrente (quasi ideale) per il carico RL . Completare il

progetto determinando una ragionevole terna di valori

per i resistori R1 , R2 e RE in modo da avere IL = 5mA.

(L’operazionale puo’ essere considerato ideale)

26

CAPITOLO 3. AMPLIFICATORI OPERAZIONALI

+15V

R2

R1

vi

R1

RE

R2

RL

R1

R2

RL

Esercizio 91

Costruire un circuito (con un amplificatore operazionale ideale) che, partendo da un’onda sinusoidale di

6 V picco picco, con valor medio nullo, generi un’onda

sinusoidale di 5 V , picco picco, con valor medio 2.5 V .

Esercizio 89

Calcolare il guadagno di tensione dell’amplificatore differenziale mostrato in figura (assumendo che i resistori con eguale nome siano identici tra loro e che

l’operazionale utilizzato sia ideale).

R1

R2

v2

R

R2

+3V

+5V

-3V

0V

Esercizio 92

Il circuito in figura rappresenta un ohmetro, con cui e’

possibile misurare la resistenza Rx : la tensione letta

sul voltmetro (che ha un fondo scala di 1 V ) e’ infatti

proporzionale ad Rx . Dato Vref = −10 V completare

il progetto determinando il valore di R in modo che sia

possibile misurare resistenze fino ad un valore massimo

10 kΩ. Si supponga ideale l’amplificatore operazionale.

vo

v1

R1

Rx

R

R2

R2

Vref

Voltmetro

Esercizio 93

Esercizio 90

Trovare la relazione che lega la corrente che circola

nel resistore RL alla tensione vi (assumendo che i resistori con eguale nome siano identici tra loro e che

l’operazionale utilizzato sia ideale).

Trovare qual e’ la condizione minima da imporre a R1 ,

R2 , R3 e R4 affinche’ la corrente iL sia unicamente

proporzionale a vs . Si supponga ideale l’amplificatore

operazionale.

27

R2

R3

R2

R1

+

v1

vs

R1

vo

_

R4

iL

ZL

R3

R4

I2

Esercizio 96

Determinare il valore della tensione di uscita vo

Valori:

1) vs e’ un segnale sinusoidale a media nulla e valore R1 = 20k

di picco 200 mV ; quale valore deve avere la tensione R2 = 30k

continua VDC affinche’ vo assuma un valore minimo di R3 = 10k

RG = 10k

0V?

2) La slew rate dell’operazionale utilizzato e’ di IG = 200 µA

10 V /µs : qual e’ la massima frequenza del segnale

sinusoidale amplificabile senza distorsione?

R2

R1

(NB L’amplificatore operazionale puo’ essere considerato ideale, con eccezione della slew rate)

Valori: R1 = 10k, R2 = 120k

IG

RG

vo

R3

Esercizio 94

vs

vo

R2

R1

VDC

Esercizio 97

Un dispositivo di misura fornisce una tensione vin che

può variare tra −200 mV e +300 mV .

Progettare, con uno o più amplificatori operazionali, un circuito che fornisca in uscita una tensione vo

proporzionale a vin e variabile tra 0 V e +10 V .

Esercizio 98

Calcolare l’amplificazione di tensione del circuito in

figura.

Valori:

Esercizio 95

R = 2.5k

R1 = 22.5k

Determinare la tensione di uscita vo in funzione dei R2 = 2k

parametri e dei generatori d’ingresso per il circuito in R3 = 4k

figura, assumendo come ideale l’operazionale utilizzato. R4 = 0.5k

28

CAPITOLO 3. AMPLIFICATORI OPERAZIONALI

R4

vS

vo

R1

R2

R3

R4

R3

Vi

io

R2

R1

RL

R

Esercizio 99

Trovare l’espressione della tensione di uscita vo in

funzione di v1 e v2 nell’ipotesi in cui

R3

R2

=

R1

R4

Esercizio 102

Determinare vo e la resistenza d’ingresso Rin per il

circuito in figura.

R1 = 10k, R2 = 30k, R3 = 15k, R4 = 30k,R5 = 120k,

vi = 9 V .

R2

R1

R1

V1

iL

R5

R4

R2

Vi

R3

Vo

Vo

V2

R3

R4

Esercizio 100

Un dispositivo di misura fornisce un segnale di tensione variabile tra 20 mV e 220 mV . Progettare, con uno

o più amplificatori operazionali, un circuito che amplifichi tale segnale e lo porti nell’intervallo −5 V / 5 V

(ovvero un segnale di 20 mV deve dare in uscita −5 V ,

mentre un segnale di 220 mV deve dare in uscita 5 V ). Esercizio 103

Determinare Vo per il circuito in figura.

R1 = 10k, R2 = 1k, R3 = 12k, R4 = 100k

Esercizio 101

Calcolare, nel circuito in figura, iL e io .

R1 = 5k, R2 = 15k, R3 = 5k, R4 = 20k,RL = 600Ω,

vi = 1.5 V .

V1 = 0.1 V , V2 = 0.05 V , Ig = 0.1 mA.

29

Si consideri Ci assimilabile ad un corto circuito a

qualunque frequenza.

VCC = 12 V , RA = 10 kΩ, RB = 10 kΩ, R1 = 10 kΩ,

R2 = 100 kΩ,

Slew rate: 1 V /µsec

L’operazionale può essere considerato ideale.

R4

V1

R1

R2

Vo

V2

Ig

R3

Esercizio 104

Un dispositivo di misura fornisce un segnale di tensione variabile tra −200 mV e +200 mV . Progettare,

con uno o più amplificatori operazionali, un circuito

che amplifichi tale segnale e lo porti nell’intervallo 0 V

/ +10 V (ovvero un segnale di -200 mV deve dare in

uscita 0 V , mentre un segnale di 200 mV deve dare in

uscita +10 V ).

Esercizio 105

Calcolare l’amplificazione di tensione e la resistenza

d’ingresso, Ri , per il circuito in figura.

R1 = 1 kΩ, R2 = 2 kΩ, R3 = 2 kΩ, R4 = 10 kΩ,

L’operazionale può essere considerato ideale.

Esercizio 106

Il segnale d’ingresso, vi , nel circuito in figura e’ sinusoidale, a frequenza variabile, con ampiezza 500 mV e

valor medio nullo. Calcolare:

a) l’ampiezza di oscillazione e il valor medio di vo ;

b) la massima frequenza del segnale d’ingresso amplificabile senza che intervenga deformazione dovuta alla

slew rate finita dell’operazionale.

Esercizio 107

Scrivere l’espressione dell’amplificazione di tensione,

Av , per l’amplificatore in figura. Trovare i valori

asintotici di Av per ω → 0 e ω → ∞.

L’operazionale può essere considerato ideale.

Esercizio 108

Calcolare la potenza totale dissipata nei resistori del

circuito in figura.

R1 = 120 kΩ, R2 = 120 kΩ, RL = 1 kΩ, vi = 6 V ,

L’operazionale può essere considerato ideale.

30

CAPITOLO 3. AMPLIFICATORI OPERAZIONALI

Esercizio 111

Calcolare l’amplificazione di di tensione, Av , del

circuito in figura.

Esercizio 109

Il segnale d’ingresso, vi , nel circuito in figura e’ sinu- Valori:

soidale, a frequenza variabile, con ampiezza 500 mV e

R1 = R2 ; R3 = R4 = 2R1

valor medio nullo. Calcolare:

a) l’ampiezza di oscillazione e il valor medio di vo ;

b) la massima frequenza del segnale d’ingresso amplificabile senza che intervenga deformazione dovuta alla

slew rate finita dell’operazionale.

Per semplicità, si consideri Ci assimilabile ad un corto

circuito alle frequenze del segnale vi .

VCC = 12 V , RA = 10 kΩ, RB = 10 kΩ, R1 = 10 kΩ,

R2 = 100 kΩ,

Slew rate: 1 V /µsec

(A parte la slew rate, l’operazionale può essere

considerato ideale).

Esercizio 112

Esercizio 110

Calcolare l’amplificazione di tensione e la resistenza

d’ingresso dell’amplificatore in figura.

L’operazionale può essere considerato ideale.

Progettare, con un operazionale LM358, in grado quindi di funzionare con alimentazione singola, un amplificatore con |Av | ≃ 100; il segnale sinusoidale d’ingresso, vs = vm sin(2πf t), ha un’ampiezza prevista

vm < 50 mV e una frequenza f ∼ 1 kHz.

Si hanno a disposizione un solo LM358, resistenze, condensatori e un solo alimentatore positivo con V =

0 ÷ 15 V .

Esercizio 113

31

Esercizio 116

Determinare l’andamento in frequenza dell’amplificazione di tensione del circuito in figura, disegnando il

diagramma di Bode del modulo con indicati i valori di

guadagno nelle varie regioni, le frequenze di taglio e le

eventuali pendenze.

Come si modifica la risposta del circuito se si aggiunge un secondo stadio, identico al primo, in cascata?

Valori:

R1 = 10k R2 = 100k C1 = 800 nF C2 = 80 pF

Esercizio 114

L’uscita dell’amplificatore in figura viene inviata ad un

carico RL = 500 Ω. Il segnale d’ingresso è sinusoidale,

vs = vm sin(2πf t), con ampiezza vm = 100 mV e frequenza f = 1 kHz. Calcolare la tensione massima ai

capi del carico e la corrente massima che vi scorre.

Valori:

R1 = 1k R2 = 10k R3 = 1k R4 = 10k

Esercizio 115

Si vuole costruire con un operazionale un amplificatore

con Av = 40 dB, da utilizzare con segnali d’ingresso

sinusoidali vs = vm sin(2πf t), con ampiezza prevista

vm < 50 mV e frequenza f fino a 100 kHz.

Quali devono essere le prestazioni dell’operazionale, in

termini di prodotto GuadagnoXBanda e Slew Rate,

per soddisfare quelle richieste?

Determinare l’andamento in frequenza dell’amplificazione di tensione del circuito in figura, disegnando il

diagramma di Bode del modulo con indicati i valori di

guadagno nelle varie regioni, le frequenze di taglio e le

eventuali pendenze.

Valori:

R1 = 10k R2 = 10k R3 = 1k R4 = 10k R5 = 100k R6 = 100k

C1 = 1 µF C2 = 0.8 nF

32

CAPITOLO 3. AMPLIFICATORI OPERAZIONALI

Esercizio 121

Due sonde di temperatura forniscono ciascuna una

uscita in tensione con una legge:

V = .05 · T + 1.0

Capitolo 4

(con T in °C e V in Volt) Costruire un dispositivo elettronico, utilizzando porte logiche standard, in grado di

fornire due segnali logici A e B, tali che:

A = 1 se entrambe le temperature superano i 30 °C;

B = 1 se solo una delle due supera i 30 °C.

Circuiti logici e

Convertitori

V1

A

B

V2

Esercizio 117

Costruire la tavola della verita’ della funzione logica

Y = ABC + ABC

Esercizio 122

Costruire la tavola della verita’ della funzione logica

Esercizio 118

Costruire il circuito che realizza la funzione logica

Y = (AB + BC)

Y = AB + AC + (A + B)

Esercizio 119

Scrivere in forma canonica la funzione logica rappresentata dalla seguente tavola della verita’

A

B

C

Y

0

0

0

1

0

0

1

0

0

1

0

1

0

1

1

0

1

0

0

0

1

0

1

0

1

1

0

1

1

1

1

1

Esercizio 123

Costruire il circuito che realizza la funzione logica

Y = (A + B + C) + AB

Esercizio 124

Scrivere in forma canonica la funzione logica rappresentata dalla seguente tavola della verita’

Esercizio 120

Che funzione logica realizza il circuito in figura?

A

B

Y

A

B

C

Y

0

0

0

0

0

0

1

0

0

1

0

0

0

1

1

0

1

0

0

0

1

0

1

1

1

1

0

0

1

1

1

1

Esercizio 125

Che funzione logica realizza il circuito in figura?

33

34

CAPITOLO 4. CIRCUITI LOGICI E CONVERTITORI

(con P è in atmosfere e I in mA).

Progettare un dispositivo di allarme in grado di dare

un livello logico “0” quando la pressione è compresa tra

1 e 10 atmosfere e di dare un livello logico “1” quando

la pressione esce da quell’intervallo.

Nota: si consideri il trasduttore come un generatore

ideale di corrente.

A

B

C

Y

Esercizio 126

Nel circuito in figura (realizzato con porte logiche TTL

in logica positiva) l’ingresso I è inizialmente a “0” logico; all’istante t=0 l’ingresso viene portato a livello logico “1”. Descrivere qualitativamente con un diagramma

il comportamento temporale dell’uscita Y ( in una scala temporale arbitraria).

Nota: si considerino trascurabili i tempi di commutazione intrinseci delle porte logiche; si tenga invece conto

delle soglie reali di commutazione dei circuiti TTL.

Esercizio 129

Il numero di persone, n, presenti in una stanza, viene

continuamente sorvegliato, grazie a cellule fotoelettriche poste all’ingresso e ad un contatore up/down a 8

bit. Se una persona entra il contenuto del contatore aumenta; se una persona esce il contenuto del contatore

diminuisce. Utilizzando le uscite del contatore costruire una variabile logica A ed una variabile logica B tali

che:

A = 1 se n ≥ 192

B = 1 se n < 192

Esercizio 130

Si ha un circuito NAND a due ingressi della famiglia

TTL in logica positiva. Uno degli ingressi (ingresso A)

viene connesso e riceve un regolare livello logico, mentre l’altro (ingresso B) viene lasciato volante (cioè non

connesso). Cosa succede? Quali livelli logici avremo in

uscita in funzione dell’ingresso A?

R

I

C

Y

Esercizio 131

Un contatore binario a 8 bit e un Flip-Flop JK ‘edge

triggered’ (sensibile al fronte di salita del Clock) sono

collegati come in figura. Inizialmente il contatore conEsercizio 127

Progettare un convertitore digitale analogico (DAC) a tiene il numero 00000000 e l’uscita Q e’ ugualmente

8 bit, con rete R-2R, che fornisca una uscita di tensione a 0. Il contatore comincia a ricevere all’ingresso una

negativa compresa tra 0 e -15 V. Questo significa che lunga sequenza di 200 impulsi. Descrivere cosa avviequando gli 8 ingressi sono tutti 0 l’uscita è 0 V, men- ne all’uscita Q del Flip-Flop. (N.B: MSB è il bit più

tre quando tutti gli ingressi sono 1, l’uscita e’ -15 V. Il significativo del contatore, J e K sono a 1 fisso)

numero a 8 bit da convertire e’ fornito da un normale

Ingresso

CONTATORE AD 8 BIT

registro a 8 bit, con uscite TTL in logica positiva ( 0 –

5 V).

MSB

LSB

Nota: è naturalmente possibile utilizzare più operazionali, se necessario.

Esercizio 128

In un certo impianto industriale è necessario mantenere sotto controllo la pressione interna di un serbatoio

di gas: quindi si desidera ricevere un segnale di allarme quando la pressione esce da un certo intervallo. La

pressione è misurata con un trasduttore che fornisce

una corrente I proporzionale alla pressione:

I = (1.0 · P + 4.0)

1

Q

J

Ck

1

K

Q

Esercizio 132

Si hanno quattro variabili logiche, A, B, C e D, che provengono da altrettanti dispositivi di misura. Costruire,

35

con le porte logiche standard, un circuito ‘rivelatore di

uguaglianza’, cioè un circuito che riceve agli ingressi

A,B,C,D e fornisce all’uscita un valore 1 quando due e

solo due dei suo ingressi valgono 1.

A B C

Y

Esercizio 133

Si hanno tre variabili logiche, A, B e C, che provengono

da altrettanti dispositivi di misura. Costruire, con le

porte logiche standard, un circuito ‘rivelatore di maggioranza’, cioè un circuito che riceve agli ingressi A,B,C Esercizio 138

e fornisce all’uscita un valore 1 quando la maggioranza Un multiplexer digitale e’ un dispositivo che consente

dei suo ingressi vale 1.

di connettere uno tra molti ingressi digitali all’uscita,

sulla base di un comando opportuno. Realizzare, con

porte logiche elementari TTL, lo schema di un multiEsercizio 134

Il c gate di Muller è un circuito a due ingressi che rea- plexer a 4 ingressi. La selezione dell’ingresso da collizza la tavola della verità riportata in figura. Pro- legare all’uscita è effettuata inviando un numero binagettare tale circuito utilizzando elementi circuitali che rio a 2 bit agli ingressi di selezione S0, S1. Inoltre il

multiplexer è controllato da un ingresso di abilitazione

conoscete.

(attivo basso): in assenza di abilitazione il multiplexer

A B Y

non trasmette all’uscita nessun ingresso.

A

0 0 0

0 1 non cambia

Y

X0

B

1 0 non cambia

X1

1 1 1

Y

X2

Esercizio 135

Due trasduttori misurano la velocità di rotazione di

due alberi, e forniscono ciascuno un’uscita

X3

S 0 S1 En

V = 0.5ω + 0.5

(con V in Volt e ω in rad/sec) Le suddette velocità

possono variare tra 0 e 5 rad/sec. Costruire un dispositivo elettronico in grado di fornire un segnale logico

TTL di allarme quando le due velocità mostrano una

differenza superiore a 0.1 rad/sec, ovvero

|ω1 − ω2 | > 0.1

Inoltre è richiesto un segnale logico che consenta di individuare in modo univoco quale dei due alberi gira a

velocità maggiore.

Esercizio 136

Progettare un circuito che realizzi il prodotto (aritmetico) di due numeri binari a 2 bit, utilizzando porte

logiche elementari e semi-sommatori.

Esercizio 139

Il “priority encoder” è un circuito che presenta in uscita

l’indirizzo più alto tra gli ingressi che sono attivi (cioè

con 1 logico). Realizzare tale circuito (a 4 ingressi),

utilizzando porte logiche elementari.

X0

X1

Y0

X2

Y1

X3

Esercizio 140

Un demultiplexer digitale e’ un dispositivo che consente

di connettere un ingresso digitale ad una sola, tra molte

uscite, sulla base di un comando opportuno. RealizzaEsercizio 137

re, con porte logiche elementari TTL, lo schema di un

Scrivere in forma canonica la funzione F realizzata dal demultiplexer a 4 uscite. La selezione dell’uscita da

circuito in figura. Progettare un circuito che realizza la collegare all’ingresso è effettuata inviando un numero

stessa funzione, utilizzando solo porte logiche NAND. binario a 2 bit agli ingressi di selezione S0, S1.

36

CAPITOLO 4. CIRCUITI LOGICI E CONVERTITORI

U0

b) quando C=1 fa un test di disuguaglianza ovvero restituisce 1 se A e B sono diversi e 0 altrimenti.

Realizzare il circuito mediante porte logiche qualunque;

U1

Input

U2

Esercizio 144

Un multiplexer è un dispositivo capace di selezionare

un singolo ingresso fra tanti e trasmetterlo in uscita,

S1 S0

in base al valore degli ingressi di selezione (vedi figura

in cui e’ mostrato un esempio a 8 ingressi). Lo stesso dispositivo puo’ anche essere utilizzato per costruire

facilmente qualunque funzione logica, con un numero

Esercizio 141

L’uscita Y di un circuito logico a 4 ingressi rispetta la di variabili pari al numero di ingressi di selezione.

seguente tavola della verità (x vuol dire “qualunque”): Utilizzando un multiplexer a 8 ingressi costruire la

funzione logica

E

SEL

A

B

Y

U3

H

x

x

x

L

L

L

L

x

L

L

L

H

x

H

L

H

x

L

L

L

H

x

H

H

Y = ABC + ABC + ABC

A0

Costruire lo schema di questo circuito utilizzando le

porte logiche elementari.

Esercizio 142

Vogliamo realizzare un dispositivo in grado di fornire

in uscita un segnale logico TTL di durata temporale

pari alla differenza tra i tempi di arrivo di due segnali

(vedi figura).

Per semplicità possiamo fare l’ipotesi che il segnale di Stop arriva sicuramente dopo uno Start; inoltre possiamo considerare trascurabili tutti i tempi di

commutazione intrinseci dell’elettronica che abbiamo

a disposizione.

A1

I0

I1

I2

I3

I4

I5

I6

I7

Y

A2

Esercizio 145

Determinare il comportamento del circuito in figura,

ovvero lo stato dell’uscita Y , tenendo conto che ogni

porta NOT ha un tempo di propagazione finito (ovvero ogni l’uscita commuta con un certo ritardo rispetto

alla commutazione del suo ingresso)

Y

Start

t

Stop

t

Output

T

t

Esercizio 143

Si vuole realizzare un circuito combinatorio che ha in

ingresso tre variabili logiche, A, B e C, e che si comporta come segue:

a) quando C=0 fa un test di uguaglianza ovvero restituisce 1 se A e B sono uguali e 0 altrimenti;

Esercizio 146

In un certo impianto industriale vengono tenuti sotto

controllo due parametri, A e B, codificati come due numeri binari a 4 bit ciascuno. Si progetti un circuito in

grado di dare un allarme (inteso come livello logico che

passa da zero a uno) quando sia A che B sono inferiori

ad 8, cioe’ A < 8 e B < 8. Il segnale di allarme deve

essere memorizzato, ovvero non deve scomparire se la

condizione anormale cessa, e deve poter essere azzerato

manualmente

Esercizio 147

Costruire un circuito per fare la somma o la sottrazione

di due numeri a 4 bit, A e B, in base al valore di un

37

ingresso di selezione, SEL.

Esercizio 150

Se SEL = 0 esegue A + B; se SEL = 1 esegue A − B. In molti paesi i semafori stradali operano con una

sequenza a 4 fasi, (Verde) - (Giallo) - (Rosso) - (RosEsercizio 148

so+Giallo), che si ripete ciclicamente. Utilizzando

Nel circuito in figura (realizzato con porte logiche TTL componenti noti progettare il circuito di controllo

in logica positiva) l’ingresso I è inizialmente a "0" lo- necessario per operare il semaforo in tale modo. Si

gico; all’istante t=0 l’ingresso viene portato a livello supponga di ricevere un idoneo impulso di clock che

logico "1", e dopo un tempo T torna al livello logico scandisce le transizioni; inoltre si supponga che ogni

"0".

lanterna del semaforo ha un interruttore comandato

Descrivere qualitativamente con un diagramma il com- che accende quando riceve un livello logico alto e speportamento temporale dell’uscita Y ( in una scala gne quando riceve un livello logico basso.

temporale arbitraria).

Nota: si considerino trascurabili i tempi di commutazione intrinseci delle porte logiche; si tenga invece

conto delle soglie reali di commutazione dei circuiti

TTL. Si ipotizzi inoltre che T >> RC.

R

I

C

Y

Esercizio 149

Un decoder e’ un circuito con n ingressi e 2n uscite: lo

stato logico degli ingressi determina quale delle uscite

viene attivata, cioe’ posta ad 1 logico. In Figura e’

riportato un esempio di decoder a 3 ingressi e 8 uscite:

I0 e’ attiva quando agli ingressi si ha A0 = 0, A1 = 0,

A2 = 0, I1 e’ attiva quando agli ingressi si ha A0 = 1,

A1 = 0, A2 = 0, e cosi’ via.

Esercizio 151

Il priority encoder è un circuito che presenta in uscita

l’indirizzo piu’ alto tra gli ingressi che sono attivi. Vogliamo realizzare un priority encoder a 4 ingressi e due

uscite . Il circuito devo inoltre avere:

- ingresso EI (Enable Input):a livello basso abilita il

dispositivo, a livello alto pone le uscite a livello alto;

- uscita EO (Enable Output): a livello basso indica che

il dispositvo e’ abilitato, ma che non e’ stata attivata

nessuna linea di ingresso;

- uscita GS (Group Signal) : a livello basso indica che il

dispositivo e’ abilitato, insieme ad almeno un ingresso.

Tutti i livelli di ingresso e uscita si intendono

attivi-bassi.

Costruite la tavola della verità di questo dispositivo.

I0

A0

A1

I1

I2

A2

I 0 I 1 I2 I3 I4 I5 I6 I7

Y1

Y2

=

=

A0 A1 A2 + A0 A1 A2

A0 A1 A2 + A0 A1 A2

A1

I3

GS

EI

Un decoder, usato insieme a opportune porte logiche, consente anche di costruire simultaneamente e

indipendentemente piu’ funzione logiche degli ingressi.

Utilizzando un decoder a 3 ingressi e quant’altro

necessario costruire le 2 funzioni logiche:

A0

EO

Esercizio 152

Esistono circuiti logici bidirezionali (necessari in molti

casi), in cui cioe’ l’ingresso e l’uscita sono intercambiabili; questo può essere realizzato con dispositivi logici

3-state. Progettate un dispositivo di questo tipo, con

gli elementi logici che conoscete, in cui:

38

CAPITOLO 4. CIRCUITI LOGICI E CONVERTITORI

Se SEL = H il livello logico A e’ trasferito all’uscita

B;

se SEL = L il livello logico B e’ trasferito all’uscita A

Si suggerisce di utilizzare flip-flop di tipo D (3-state).

A

B

A0

A0

A1

A1

A2

A2

P

SEL

Esercizio 156

La pressione di un certo impianto industriale deve essere mantenuta all’interno di un intervallo ottimale di

A

funzionamento. Essa e’ misurata, convertita in numero

B

binario, n, e memorizzata in un registro a 8 bit.

Progettare un circuito che, in base al valore di n, coInizialmente A è a livello logico 0. All’istante t = T

manda accensione e spegnimento dell’impianto (accenil livello logico di A passa da 0 a 1. Descrivete con

sione e spegnimento sono ottenuti fornendo ad un inun grafico l’andamento temporale del livello logico di

terruttore comandato un livello logico TTL, "1" per

B, supponendo che il ritardo di propagazione di ogni

accensione, "0" per spegnimento): il segnale di speporta logica sia di 10 ns. (Il ritardo di propagazione

gnimento deve essere inviato quando n ≥ 192; la

è il tempo che una porta logica impiega a commutare

riaccensione deve avvenire quando n < 128.

l’uscita).

Per semplicità si supponga che l’uscita commuti "a gradino" ovvero passi da 0 a 5V in modo istantaneo, dopo Esercizio 157

Costruire la funzione logica

il ritardo di propagazione.

Esercizio 153

Esercizio 154

In un certo impianto industriale la temperatura è tenuta sotto controllo con 3 sonde, che forniscono 3 tensioni, V1 ,V2 ,V3 comprese fra 0 e 5 V . Si vuole realizzare

un sistema di allarme per segnalare situazioni anomale,

ovvero:

Se tutte le tensioni sono minori di 3 V si accende un

Led verde;

Se tutte le tensioni superano 3 V si accende un Led

rosso;

Se 2 delle 3 tensioni superano 3 V si accende un Led

giallo.

Progettate il circuito necessario per ottenere questo

risultato utilizzando i dispositivi che conoscete.

Esercizio 155

Il bit di parità è un codice di controllo utilizzato nei calcolatori per prevenire errori nella trasmissione o nella

memorizzazione dei dati. Tale sistema prevede l’aggiunta di un bit ridondante ai dati, calcolato in modo

tale che il numero di bit che valgono 1 sia sempre pari

o dispari. Progettare un dispositivo che riceve all’ingresso un numero a 3 bit e fornisce in uscita lo stesso

numero piu’ il bit di parita’, P (P e’ 1 se il dato in

ingresso contiene un numero pari di "1").

Y = A BC + ABC

utilizzando un multiplexer a 8 ingressi.

I0 I1 I2 I3 I4 I5 I6 I7

A

A0

B

A1

C

A2

Y

Esercizio 158

La temperatura di un impianto industriale deve essere mantenuta all’interno di un intervallo ottimale di

funzionamento. Se T > 100 ◦ C si deve accendere il

raffreddamento, mentre se T < 80 ◦ C si deve spegnere

il raffreddamento (le due soglie devono essere diverse

per evitare che il raffredddamento si accenda e spenga

in continuazione) La temperatura e’ misurata tramite

un trasduttore che fornisce in uscita una tensione, V :

V = .05 T + 1.0

39

(con T in ◦ C e V in Volt). Si progetti un circuito che

controlli la temperatura e comandi il raffreddamento

per ottenere il risultato anzidetto (accensione e spegnimento del raffreddamento sono ottenuti fornendo ad un

interruttore comandato un livello logico TTL, "1" per

accensione, "0" per spegnimento).

Esercizio 161

Progettare un circuito che fornisce in uscita l’AND oppure il NOR delle due variabili logiche A e B, in base

al valore di S:

S=0

→ Y = AB

S=1

→ Y =A+B

Esercizio 159

Un decoder e’ un circuito con n ingressi e 2n uscite: lo

stato logico degli ingressi determina quale delle uscite

viene attivata, cioe’ posta ad 1 logico.

Un decoder, usato insieme a opportune porte logiche, consente anche di costruire funzione logiche degli

ingressi.

Esercizio 162

Il circuito in figura è realizzato con porte TTL in logica

positiva. Inizialmente l’ingresso I si trova a 0 logico.

A

A0

All’istante t = t1 passa a 1 logico.

a) Determinare lo stato iniziale dell’uscita Y , ovvero

B

A1

per t < t1 ;

A2

C

b) Costruire in modo qualitativo l’andamento temporale dell’uscita Y per t ≥ t1 .

Si considerino trascurabili i tempi di commutazione

delle porte logiche rispetto al tempo τ = RC. Si

Utilizzando un decoder a 3 ingressi si realizzi un genetenga invece conto dei valori effettivi delle soglie di

ratore di parita’ ovvero un circuito che fornisca in uscicommutazione.

ta un "1" logico, quando nei 3 bit di ingresso è presente

un numero pari di "1" (cioe’ zero, oppure due).

Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7

Esercizio 160

Scrivere in forma canonica la funzione logica rappresentata dalla seguente tavola della verita’

A

B

C

Y

0

0

0

1

0

0

1

1

0

1

0

0

0

1

1

1

1

0

0

1

1

0

1

1

1

1

0

0

1

1

1

0

Ridurre poi la funzione alla sua forma minimale utilizzando le proprieta’ dell’algebra di Boole. Disegnare il

corrispondente circuito realizzato utilizzando solo delle

porte NAND.

Esercizio 163

In un tipico quiz televisivo i due concorrenti dispongono di un pulsante. Quando uno dei due vuole prenotarsi per rispondere alla domanda preme il suo pulsante:

si accende il led corrispondente (che resta acceso) e contemporaneamente si inibisce il pulsante dell’altro concorrente. Progettare il circuito necessario per ottenere

questo risultato. Prevedere anche un terzo pulsante

per riportare il sistema allo stato iniziale.

Esercizio 164

Progettare un circuito che fornisce in uscita l’OR oppure il NAND delle due variabili logiche A e B, in base

al valore di S:

S=0

S=1

→ Y =A+B

→ Y = AB

40

CAPITOLO 4. CIRCUITI LOGICI E CONVERTITORI

Esercizio 165

Il circuito in figura è realizzato con porte TTL in logica

positiva. Inizialmente l’ingresso I si trova a 1 logico.

All’istante t = t1 passa a 0 logico.

a) Determinare lo stato iniziale dell’uscita Y , ovvero

per t < t1 ;

b) Costruire in modo qualitativo l’andamento temporale dell’uscita Y per t ≥ t1 .

Si considerino trascurabili i tempi di commutazione

delle porte logiche rispetto al tempo τ = RC. Si

tenga invece conto dei valori effettivi delle soglie di

commutazione.

Esercizio 166

La temperatura di un sistema fisico è tenuta sotto controllo da tre sonde, T1 ,T2 e T3 . Ogni sonda fornisce

una tensione Vi = 10 × Ti (con V in mV e T in gradi centigradi). Progettare un circuito che genera un

allarme (accensione di un Led) quando la media delle

tre temperature supera 90 °C. L’allarme deve persistere (ovvero il Led deve rimanere acceso) anche se la

temperatura riscende sotto la soglia di allarme e deve

poter essere azzerato manualmente.

Il circuito in figura realizza la funzione logica Y =

AB + AC.

Inizialmente A = B = C = 1. All’istante t = 0 A transisce al livello 0. Determinare l’andamento temporale

dell’uscita nell’ipotesi che il ritardo di propagazione di

ogni porta logica sia di 10 ns.

Esercizio 169

Il livello, L, del liquido contenuto in un serbatoio deve essere mantenuto all’interno di un intervallo

Lmin ÷ Lmax e, se necessario, ripristinato aprendo una

elettrovalvola, V , che controlla il condotto di immissione. Il circuito di comando apre l’elettrovalvola se

riceve un livello logico 1 e la chiude se riceve uno 0. Il

livello e’ controllato da due sensori, Smin , che fornisce

in uscita un livello logico 1 se L > Lmin e Smax che

fornisce in uscita un livello logico 1 se L > Lmax .

Progettare il circuito che legge le uscite dei due sensori e fornisce all’elettrovalvola il dovuto livello logico di

comando.

Esercizio 170

Progettare il circuito logico a 3 ingressi che produce in

uscita la funzione

Y = ABC + ABC + ABC

utilizzando solo porte NOT, porte AND a due ingressi

e porte OR a due ingressi.

Esercizio 171

Esercizio 167

Progettare, utilizzando un multiplexer, un circuito logico con 3 ingressi che riceve un numero binario a 3 bit

e fornisce un’uscita logica 1 se e solo se il numero in

ingresso e ’ maggiore di 5.

Esercizio 168

Progettare, utilizzando un decoder e opportune porte

logiche, un sommatore completo (Full Adder) a 1 bit.

Esercizio 172

Un certo impianto industriale richiede un’alimentazione elettrica garantita. Quindi, in caso di cali di tensione, entra in funzione un’alimentazione di

emergenza.

41

Lo switch che seleziona l’alimentazione e’ comandato

da un livello logico I: se I = 0 e’ connessa l’alimentazione principale, se I = 1 e’ connessa l’alimentazione

di emergenza. La tensione V fornita dall’alimentatore

principale viene continuamente misurata : se V scende

sotto un valore V1 deve entrare in funzione l’alimentazione di emergenza, mentre deve essere ripristinata l’alimentazione principale se V risale almeno a V2

(maggiore di V1 ). Si hanno a disposizione due variabili

logiche (costruite con opportuni comparatori), L1 e L2 :

L1 = 1 se V > V1 ;

L2 = 1 se V > V2 .

Progettare il circuito logico necessario per gestire l’alimentazione dell’impianto, ovvero che fornisca il necessario comando logico allo switch in base ai valori di L1

e L2 .

42

CAPITOLO 4. CIRCUITI LOGICI E CONVERTITORI

Esercizio 4

Il risultato richiesto si ottiene completando in questo

modo il circuito:

50

Capitolo 5

25

+

_

10V

50

Soluzioni

Esercizio 5

Conviene anzitutto trasformare il generatore di corrente da 5mA (con i 10k in parallelo) in un generatore di

5.1 Reti

tensione da 50V (con i 10k in serie). A questo punto la

tensione equivalente si ricava scrivendo l’equazione del

Esercizio 1

La risposta può essere facilmente ricavata utilizzando nodo

Veq

Veq − 50 Veq + 5

il teorema di Thevenin. Dopo aver corto circuitato il

+

+

=0

10k

5k

10k

generatore si trova:

Da cui si ricava Veq = 10V .

R = 25k

Corto circuitando i generatori di tensione si trova poi

Req = 2.5k.

Esercizio 2

Esercizio 6

Per trovare il generatore equivalente di Thevenin è Corto circuitando i due generatori si trova facilmente

sufficiente scrivere l’equazione del nodo A:

che Req = 10k . Per calcolare la tensione equivalente

conviene anzitutto calcolare la tensione sul nodo in

VA + 5

VA

5 − VA

=

+

alto; essa è data da:

10k

5k

10k

10k

da cui si ricava VA = −1.25V , che e’ proprio il valore

= −2.5V

V1 = 5

10k

+ 10k

del generatore equivalente.

La resistenza equivalente si trova corto circuitando i

Quindi la tensione sul punto A è data da

generatori e si ottiene facilmente Req = 2.5k.

Esercizio 3

Per calcolare la resistenza equivalente si devono corto

circuitare i due generatori di tensione. Si ottiene facilmente Req = 11k.

Per calcolare la tensione equivalente conviene scrivere

l’equazione dell’unica maglia; scegliendo per la corrente

il verso antiorario si ha:

−2.5V − 10V = −12.5V

Esercizio 7

Dalle misure fatte si ricavano le due relazioni:

10k

Vx = 10

Rx + 10k

100k

Vx = 15

Rx + 100k

15 = 25k × I

Da cui si ricava:

I = .6 × 10−3

La tensione richiesta è quindi data da:

dove Vx ed Rx sono rispettivamente i valori del generatore equivalente e della resistenza d’uscita. Dividendo

membro a membro le due equazioni Vx si elimina e si

può facilmente ricavare

10 − 10k × .6 × 10−3 = 4 V

Rx ≃ 5.9k

43

44

CAPITOLO 5. SOLUZIONI

VEQ = 1 V , REQ = 2.5 kΩ

Esercizio 8

Si ha

Req = 1.4k

Veq = −0.85 V

Esercizio 9

E’ uno di quei casi in cui e’ assolutamente lecito approssimare. Possiamo trascurare la resistenza da 50Ω

rispetto a 100k e si trova facilmente Ri ≃ 9k.

Esercizio 10

L’impedenza di ingresso è ovviamente minima a frequenza infinita, quando l’impedenza del capacitore diviene nulla. Il suo valore minimo è quindi Zi = 10k

L’impedenza d’uscita è data dal parallelo tra il resistore

da 10k e la serie

1

(50 +

jω100nF )

Pertanto essa è massima alle basse frequenze, dove

tende al valore Z0 = 10k.

Esercizio 11

La resistenza equivalente e’ data da:

Req = R1 k R2 + R3 k R4 = 25k

La tensione equivalente puo’ essere calcolata valutando

anzitutto VA e VB rispetto al nodo tra R2 e R4 . Si ha:

VA =

VB =

R2

Vg = 5 V

R1 + R2

R4

Vg = 2.5 V

R3 + R4

Quindi

Veq = VA − VB = 2.5 V

Esercizio 12

La resistenza equivalente e’ data da:

Req = R1 k [R3 + (R2 k R4 )] = 1k

La tensione equivalente puo’ essere calcolata trasformando anzitutto il generatore di corrente Ig con la sua

resistenza R1 in parallelo in un generatore di tensione

Vg = Ig R1 con R1 in serie. Si trova poi facilmente:

Veq =

Esercizio 13

(R3 + R2 k R4 )

R1 Ig = 2V

R1 + R3 + R2 k R4 )

Esercizio 14

VEQ = 1 V , REQ = 2.5 kΩ

Esercizio 15

A destra del generatore J vi sono i resistori R3 ,R4 ,R5

in parallelo tra loro ed in serie al resistore R2 . La

resistenza equivalente e’ quindi

Re′ = R2 + (R3 k R4 k R5 ) = 100Ω

Questa resistenza e’ a sua volta in parallelo ad R1 ,

quindi la resistenza complessiva vista dal generatore e’

Re = R1 k Re′ = 50Ω

La tensione ai capi di J e’ infine

V = Re J = 500 mV

Esercizio 16

a) L’esercizio puó essere risolto applicando il principio

di sovrapposizione degli effetti. Cortocircuitando il generatore V2 , su R0 scorre una corrente verso massa di

valore I1 = 20 mA. Cortocircuitando il generatore V1 ,

su R0 scorre una corrente in verso opposto alla precedente di valore I2 = 10 mA. Sommando le due correnti

si ottiene una corrente totale che scorre verso massa di

valore Itot = 10 mA. La tensione del punto B vale

quindi: VB = R0 × Itot = 0.5 V .

b) Per il calcolo della resistenza equivalente si noti che,

dopo aver cortocircuitato i due generatori, le resistenze

R1 , R0 e la serie di R2 e R3 , sono in parallelo tra loro,

quindi la resistenza equivalente vale 25 Ω.

Esercizio 17

La funzione di trasferimento della rete in esame e’ data

da

sL1

=

T (s) =

R + s(L1 + L2 )

L1

L1 + L2

R

+s

L1 + L2

s

La trasformata della funzione d’ingresso e’ V (s) = k/s

quindi

L1

k

L1 + L2

Vo (s) =

R

+s

L1 + L2

45

5.2. CIRCUITI CON TRANSISTOR

Questa funzione ha un polo

p1 = −

con residuo

si può ricavare il valore della corrente di base

R

L1 + L2

L1

k1 = k

L1 + L2

Quindi la anti-trasformata di Vo (s) e’ data da

R

−

t

L1

e L1 + L2

vo (t) = k

L1 + L2

Esercizio 18

Applicando il teorema di Thevenin possiamo trasformare il circuito come in figura, dove

R′ = R1 k (R2 + R3 ) = 9.12k

e

R2 + R3

V1 − V2 = 12 V

R1 + R2 + R3

Scrivendo l’equazione della maglia e risolvendo si trova

infine

Vo = 2.88 V

V′ =

IB = 93µA

dove abbiamo supposto VBE ≃ 0.7 V . Utilizzando

il valore noto di βF possiamo quindi ricavare IC =

9.3 mA ; a questo punto, dalla equazione della maglia

di uscita

VCC = RC IC + VCE

ricaviamo

VCE = 0.7 V

Questo valore è maggiore della tensione di saturazione

VCEsat , quindi consistente con l’ipotesi che pertanto risulta verificata: il transistor è nella regione attiva.

b) Per rispondere a questa domanda ricordiamo la formula che lega la transconduttanza gm alla corrente di

collettore:

|Ic |

hf e

=

gm =

hie

T

Pertanto si può ricavare il valore di gm , e quindi di hie ,

assumendo che il transistor si trovi a temperatura ambiente e che hf e coincida con βF . Si trova hie = 280 Ω

, che rappresenta il valore della resistenza di ingresso

complessiva dell’amplificatore (RB , in parallelo ad hie

è in questo caso trascurabile).

Esercizio 20

Il punto di lavoro statico non è influenzato dalla presenza del capacitore sull’emettitore. Nell”ipotesi che

la corrente di base del transistor sia trascurabile rispetto alla corrente complessiva del partitore si trova

facilmente:

5.2

Circuiti con transistor

VB

=

VE

=

IC

≃

VC

=

=

VCE

3k

12 = 2 V

18k

VB − 0.7 = 1.3 V

VE

= 1.3 mA

IE =

1k

12V − IC · 4k = 6.8 V

VC − VE = 5.5 V

Esercizio 19

a) La giunzione base-emettitore è sicuramente polarizzata direttamente quindi il transistor può essere nella

regione attiva oppure in saturazione. Per accertarlo

faremo l’ipotesi che il transistor sia nella regione attiva e verificheremo se questa ipotesi porta a risultati

consistenti.

Dall’equazione della maglia di ingresso

L’ipotesi che abbiamo fatto all’inizio è ragionevole, perchè nel peggiore dei casi il transistor 2N2222A ha un

βF di 50; questo corrisponde ad una corrente di base

massima IB = 26 µA, sicuramente molto minore della

corrente del partitore.

VCC = RB IB + VBE

VCE = VCEsat ≃ 0.2V

Esercizio 21

Se il transistor è in saturazione possiamo assumere che

46

CAPITOLO 5. SOLUZIONI

Quindi è possibile ricavare

IC =

E’ evidente questa relazione non può essere soddisfatta

con alimentazioni simmetriche. Una possibile soluzione è VEE = −2V , VCC = 12V , RE = 1k, RC = 5k.

Si otterrà IC = 1.3mA e VCE ≃ 6V , superiore alla

richiesta minima.

10 − 0.2

≃ 10 mA

1k

Esercizio 22

I valori dei resistori del partitore di base determinano

la tensione di base. Si ha in questo caso VB = 1.5V e

VE = 0.8V .

Possiamo ottenere l’amplificazione richiesta scegliendo,

ad esempio, RE = 1k, RC = 5k. Avremo allora:

IC ≃ IE =

VE

≃ 0.8 mA

RE

e

VC = VCC − RC IC = 11 V

Esercizio 25

Si verifica facilmente che il progetto non è corretto. Infatti si ha VB = 2V , VE = 1.3V e IC = 1.3mA. Con

questo valore di corrente, se il transistor fosse nella regione attiva, VCE verrebbe negativa, il che è assurdo.

Quindi il transistor è in saturazione. E’ necessario modificare il partitore di base per avere una tensione di

base più piccola e quindi anche una tensione di emettitore più piccola. Dalla equazione della maglia di uscita

ricaviamo:

VCC = 11RE IC + VCE

valori ragionevoli per assicurare il corretto funzionamento dell’amplificatore.

VE = RE I C

da cui si ottiene

Esercizio 23

La tensione applicata effettivamente

dell’amplificatore è data da

1k

vs = 200 mV

vi =

1k + 500

La tensione d’uscita è quindi data da:

v0 = A · vi = 1.6V

all’ingresso

VCC = 11VE + VCE

In sostanza, per avere la VCE positiva dobbiamo

imporre che

VCC

VE ≤

11

Valori possibili sono ad esempio VB = 1.2V e VE =

0.5V , che si possono ottenere modificando il partitore

di base in modo opportuno.

Esercizio 26

Esercizio 24

Ovviamente VCC deve essere positiva, mentre VEE deve Sappiamo che l’amplificazione di tensione e’ data da:

essere negativa. Scrivendo l’equazione della maglia di

Av = −gm RC

uscita e tenendo conto che si deve porre RC = 5RE per

avere amplificazione pari a −5:

e che

|IC |

gm ≈

RC IC + VCE + RE IC = |VCC | + |VEE |

25 mV

Quindi, per ottenere Av = −200 dobbiamo avere

VCE = |VCC | + |VEE | − 6RE IC

RC IC = 5V . Possiamo ad esempio scegliere RC = 1k,

La tensione dell’emettitore è a -0.7 V, quindi si deve da cui segue che IC deve essere di 5 mA. Per ottenere

anche avere

questa corrente sul collettore devo avere una corrente

RE IC = |VEE | − 0.7

di base di circa 33 µA , che posso realizzare con una

resistenza

di base, RB ∼ 270k.

Sostituendo questa relazione nella precedente equazioIl

massimo

segnale d’ingresso amplificabile senza

ne si ottiene

distorsione è di circa 25 mV .

VCE = |VCC | − 5|VEE | + 4.2

Esercizio 27

Quindi, se si desidera avere VCE ≥ 5V è necessario Per trovare il punto di lavoro del transistore possiamo

scegliere le alimentazioni in modo che:

scrivere l’equazione della maglia di base:

|VCC | − 5|VEE | > 0.8

VCC = RC (IC + IB ) + RB IB + VCE

47

5.2. CIRCUITI CON TRANSISTOR

ovvero, ricordando che IC = βF IB :

Da cui vo = 50 V .

VCC = (1 + βF )RC IB + RB IB + 0.7

da cui si ricava IB ≃ 30 µA, IC ≃ 3 mA, VCE

Perciò il transistor è nella regione attiva.

Esercizio 30

Possiamo scrivere le equazioni della maglia d’ingresso

≃ 3.5 V . e della maglia di uscita, tenendo conto dell’errore di

montaggio

VCC = R1 IB + VBE + RE IC

RB

VCC = RC IC + VCE + RE IC

hie

hfe i b

RC

Dalla prima equazione si ricava

IB =

L’amplificazione di tensione può essere ricavata costruendo il modello h per piccoli segnali (vedi figura) e

scrivendo l’equazione del nodo di uscita:

vi − vo

vo

= h f e ib +

RB

RC

Ma ib = vi /hie quindi si ha

vi − vo

hf e v i

vo

=

+

RB

hie

RC

ovvero

vi (

1

hf e

1

1

−

) = vo (

+

)

RB

hie

RC

RB

I termini in RB possono essere trascurati in entrambi

i membri e si ricava

hf e R C

vo

=−

= −gm RC ≃ −310

vi

hie

dove abbiamo utilizzato la nota relazione tra il valore

di gm e quello di IC .

VCC − 0.7

R 1 + βF R E

e dalla seconda

VCE = VCC − (RC + RE )βF IB

E’ facile verificare che il transistor e’ in saturazione

(VCE viene negativa).

Esercizio 31

Determinazione del punto di lavoro:

la base del transistore è bloccata alla tensione VB ≃

0.7V ; pertanto il partitore di tensione blocca anche la

tensione del collettore

VC = 11 · VB = 7.7 V

La corrente IC può essere questo punto ricavata facilmente (si noti che IC non è la corrente che circola in

RC ):

IC =

VC − VB

VCC − VC

−

≃ 0.9 mA

RC

R1

L’amplificazione di tensione può essere ricavata costruendo il modello per piccoli segnali (vedi figura) e

Esercizio 28

I due transistor hanno la stessa VBE (pari a circa 0.7V). scrivendo l’equazione del nodo di uscita:

Le equazioni di Ebers-Moll ci dicono che la corrente di

vi − vo

v i hf e

vo

collettore di un transistor dipende solo da VBE , se si

=

+

R1

hie

RC

trascura il termine relativo alla corrente di polarizzazione inversa del diodo base collettore. Pertanto, se i ovvero

1

hf e

1

1

due transistor sono identici ed alla stessa temperatura

vi (

−

) = vo (

+

)

R1

hie

RC

R1

le due correnti di collettore devono essere identiche. La