1

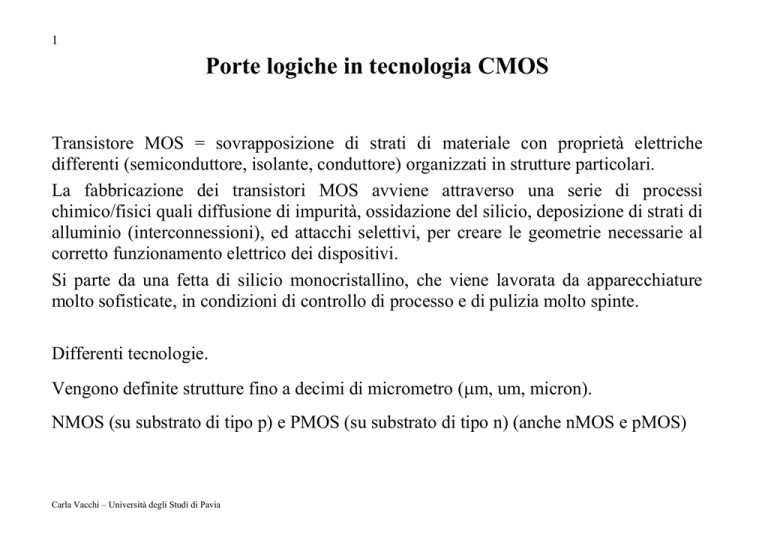

Porte logiche in tecnologia CMOS

Transistore MOS = sovrapposizione di strati di materiale con proprietà elettriche

differenti (semiconduttore, isolante, conduttore) organizzati in strutture particolari.

La fabbricazione dei transistori MOS avviene attraverso una serie di processi

chimico/fisici quali diffusione di impurità, ossidazione del silicio, deposizione di strati di

alluminio (interconnessioni), ed attacchi selettivi, per creare le geometrie necessarie al

corretto funzionamento elettrico dei dispositivi.

Si parte da una fetta di silicio monocristallino, che viene lavorata da apparecchiature

molto sofisticate, in condizioni di controllo di processo e di pulizia molto spinte.

Differenti tecnologie.

Vengono definite strutture fino a decimi di micrometro (m, um, micron).

NMOS (su substrato di tipo p) e PMOS (su substrato di tipo n) (anche nMOS e pMOS)

Carla Vacchi – Università degli Studi di Pavia

2

Spaccato di una tecnologia CMOS classica:

in

out

VDD

GND

in

polisilicio

(gate)

GND

VDD

out

p+

contatto

substrato

n+

n+

p+

p+

source

drain

drain

source

ossido di gate

transistore NMOS

ossido di gate

n well

n+

contatto

n-well

transistore PMOS

p substrate

In genere source e drain sono indifferenti (transistore simmetrico), anche se in alcune

tecnologie particolari ciò può non essere vero.

Carla Vacchi – Università degli Studi di Pavia

3

Caratteristiche elettriche di un transistore MOS

Polisilicio (gate)

W

L

source

substrato

drain

ossido di gate

Transistore NMOS

MOS a canale n (in figura, le dimensioni delle strutture relative all’ossido di gate e al

polisilicio di gate sono state aumentate per chiarezza)

aumento VG: si allontanano le lacune e si attirano elettroni

si crea un canale conduttivo nel semiconduttore al di sotto dell’ossido di gate

Si suppone che fino alla tensione di soglia Vth la corrente sia nulla (in realtà si ha anche

conduzione in condizioni di sottosoglia, e può essere un problema)

Per VG > Vth, quando il canale è formato, esistono due zone di funzionamento:

Carla Vacchi – Università degli Studi di Pavia

4

ID

VGS

VDS

VDS << (VGS – Vth): zona di triodo (segue la legge di Ohm e si comporta come un resistore)

VDS

W

I D Cox VDS VGS Vth

L

2

Vth < VGS < VDS + Vth): zona di pinch off o saturazione (ID non dipende da VDS)

In realtà aumentando VDS si modula il canale

ID

Cox W

2

L

VGS Vth 2 1 VDS

A noi interessa spento o in zona di triodo

Carla Vacchi – Università degli Studi di Pavia

5

Invertitore fully CMOS

VDD

VDD

in

0

1

P

PMOS

in

out

in

out

N

NMOS

out

1

0

out assume i valori GND e VDD perché uno dei due MOS

impone il valore logico mentre l’altro si interdice.

Invertitore CMOS Caratteristiche statiche

Caratteristica di trasferimento

Vout

VOL = 0 V

VDD

VOH = VDD

VIL VIH

VDD

Vin

0.5 VDD (?)

Famiglia fully CMOS

Sotto l’ipotesi: corrente statica sul carico nulla

livelli statici in uscita coincidenti con l’alimentazione

corrente che scorre nella porta nulla

Carla Vacchi – Università degli Studi di Pavia

6

Capacità delle interconnessioni

x2

x1

h

conduttore

drain

t

ossido

substrato

x2

x1

h

conduttore

t

ossido

conduttore

conduttore

CP = (/t) A = (/t) x1 x2

+ effetti di bordo

fringing fields

CP

condensatore a piatti

piani e paralleli

Carla Vacchi – Università degli Studi di Pavia

drain

x2

7

fringing fields

conduttore2

CP

conduttore1

condensatore a piatti

piani e paralleli

fringing fields

conduttore1

CP

conduttore2

ossido

condensatore a piatti

piani e paralleli

LIVELLO 3

LIVELLO 2

LIVELLO 1

Carla Vacchi – Università degli Studi di Pavia

8

Capacità in un Transistore MOS

gate

drain

source

Cs

Cg

Cd

Capacità di drain

W

source

b

drain

b

Capacità di gate

W

source

tox

drain

L

fringing fields

overlap

Carla Vacchi – Università degli Studi di Pavia

overlap

9

INVERTITORE SENZA CARICO ESTERNO

VDD

CgP

VDD

CdP

gateP

drainP

out

in

Cg =

CgN + CgP

drainN

Cd

gateN

CgN

CdN

Cd = CdN + CdP = Cintrinseca

INVERTITORI IN CASCATA

in

out1

INV1

INV2

VDD

INV1

in

Cg =

CgN1 + CgP1

Carla Vacchi – Università degli Studi di Pavia

out2

Cd = CdN1 + CdP1 = Cintrinseca

out1

CTOT = Cd + Cg2 + Cinterconnessione

10

INVERTITORE CON PIU’ PORTE COME

CARICO

in

out1

INV1

INV2

INV3

INV4

CTOT = Cd1 + Cg2 + Cg3 + Cg4 + Cinterconnessione

Nel caso ci siamo porte più complesse come carico, viene

aggiunta la capacità di ingresso di ciascuna porta

INVERTITORI con carico CL

in

out

CL

CTOT = Cd + Cinterconnessione + CL

Carla Vacchi – Università degli Studi di Pavia

11

Caratteristiche dinamiche

Tempo di ritardo (delay)

Vin

50% VDD

Vout

tdr

50% VDD

tdf

t

tdr,df = funzioni(parametri processo, dimensionamento

transistori, tensione di alimentazione, carico esterno)

CL

t dr, df k dr,df

n, p VDD

dove

kdr,df è funzione (complicata) di Vth/VDD,

(grafico nelle dispense)

CL rappresenta la capacità totale di carico:

CL = (Cintrinseca, Cgates(pilotate dalla porta), Cinterconnessioni)

Carla Vacchi – Università degli Studi di Pavia

12

Dissipazione di potenza statica

Vout

VDD

VDD

ID

in

out

VDD

substrato NMOS

collegato a GND

PS ,leak _ TOT VDD

substrato PMOS (n-well)

collegato a VDD

# porte

I

i 1

leakage,i

+

# porte

PS , subth _ TOT VDD

I

subth, i

i 1

Numero di porte, area, tecnologia

Carla Vacchi – Università degli Studi di Pavia

Vin

13

Dissipazione di potenza dinamica

Carica e scarica dei condensatori

VDD

VDD

out

in

out

in

CL

CL

VDD

1/f

out

in

CL

2

PD CL VDD f

2

PDTOT VDD

# porte

C

L ,i

fi

i 1

oppure

PDTOT V

2

DD

# porte

f sys

C

i 1

L ,i

Ai

dove Ai f i / f sys

+ veloce = + potenza

per consumare di meno:

scelte circuitali: W ed L minime

scelte di sistema (limitazione della tensione VDD)

scelte architetturali (far commutare i nodi solo quando

necessario)

Carla Vacchi – Università degli Studi di Pavia

14

Dissipazione di potenza di corto circuito

Vout

VDD

VDD

ID

in

out

VDD

VDD

VDD

trin

out

in

tfin

out

in

CL

PSC

Vin

12

VDD 2 Vth 3 1.25 t r , f

CL

in

f

In ogni caso:

L = Lmin permesso dalla tecnologia

(a parità di W/L meno area, meno capacità e meno potenza)

Si può anche aumentare la velocità:

più potenza, ma più elaborazione!

Carla Vacchi – Università degli Studi di Pavia

15

Invertitore fully CMOS

VDD

VDD

in

0

1

P

PMOS

in

out

in

out

N

NMOS

out

1

0

Il nodo di uscita assume i valori GND e VDD perché uno

dei due transistori impone un valore logico forte, mentre

l’altro si interdice.

Altre porte combinatorie

VDD

a

P

P

VDD

a

P

out

N

a

a

P

b

out

b

b

N

N

b

N

NAND CMOS

NOR CMOS

La parte PMOS e la parte NMOS risultano complementari:

cammini paralleli si trasformano in cammini serie.

Le porte invertenti sono molto compatte in CMOS.

E’ possibile costruire porte NAND e NOR a più ingressi.

Carla Vacchi – Università degli Studi di Pavia

16

LOGICA AD INTERRUTTORI

Porta di trasferimento (transfer gate)

s

x

s

s

y

x

s

s

x

y

y

x

s

s

s

per s = 0 i transistori sono entrambi spenti

s = 1 i transistori sono entrambi accesi

il valore x = 0 viene trasferito bene dal transistore NMOS

il valore x = 1 viene trasferito bene dal transistore PMOS

Multiplexer

out a s b s

se s 1, out a , se s 0, out b

Può essere realizzato direttamente tramite interruttori

s

s

a

a

out

s

b

a

b

b

Carla Vacchi – Università degli Studi di Pavia

out

out

s

s

a

1

0

b

s

s

17

Level sensitive latch

Latch D (DELAY): memorizza e ripropone in uscita un dato presente all’ingresso D in

funzione del valore del segnale presente all’ingresso di controllo ck (spesso è un clock,

ma non è necessario).

se ck è nello stato attivo: una variazione dell’ingresso ha un effetto immediato

se ck è nello stato non attivo l’uscita viene memorizzata e mantenuta stabile

Ingressi condizionati da un segnale di controllo: synchronous inputs.

ck

ck

D

Q

D

ck

D

1

Q

Latch

ck

Q

0

ck

ck

D

Q

ck = 1

Carla Vacchi – Università degli Studi di Pavia

D

Q

ck = 0

18

Edge triggered register (flip flop)

Combinando opportunamente un positive ed un negative level-sensitive latch si ha un

edge triggered register (primo stadio master, e secondo slave) o flip-flop.

Sensibile al fronte del segnale di controllo ck, non al livello.

ck

D

Q

D

0

QM

1

Q

ETDFF

1

0

ck

flip-flop DELAY “positive edge triggered” (transizione attiva: ck 01)

QM

D

Q

ck = 0

QM

D

Q

ck = 1

Carla Vacchi – Università degli Studi di Pavia

19

Caratteristiche

dinamiche

Tengono conto dei ritardi

introdotti dal dispositivo reale.

ck

D

Q

0

QM

1

1

Q

0

tck,q tempo di ritardo tra la variazione attiva dell’ingresso di controllo ck e

l’aggiornamento del valore dell’uscita Q (in modo analogo per l’eventuale uscita Q)

Per come è realizzato un edge triggered register, le variazioni dell’uscita in risposta a

variazioni dell’ingresso D vengono sempre condizionate dall’ingresso di controllo ck.

tck,q

tck,q

D

ck

Q

time

funzionamento di un positive edge triggered register

Carla Vacchi – Università degli Studi di Pavia

20

Per assicurare il corretto funzionamento del flip flop è necessario controllare la

temporizzazione relativa (timing) tra i segnali di ingresso e la loro durata.

Anche per queste strutture, se questi tempi non vengono rispettati, l’uscita è

indeterminata.

tsu tempo di setup: intervallo di tempo immediatamente precedente la transizione

attiva del segnale di controllo ck (01 nel caso di un positive edge triggered

register, 10 nel caso di un negative edge triggered register), intervallo durante il

quale il segnale di ingresso D deve essere mantenuto ad un valore logico stabile.

th

tempo di hold: intervallo di tempo che segue la transizione attiva del segnale di

controllo ck, durante il quale il segnale di ingresso D deve essere mantenuto ad un

valore logico stabile.

tw larghezza dell’impulso di controllo: intervallo di tempo minimo di permanenza del

segnale di controllo ck ad un livello logico stabile. Anche tck/2,min nel caso il segnale

di controllo ck sia una forma d’onda quadra con duty-cycle pari al 50%

(caratteristiche tipiche ad esempio di un segnale di clock).

Carla Vacchi – Università degli Studi di Pavia

21

ck

D

0

QM

1

tsu

1

Q

0

tw

tw

th

tsu

tw

D

th

ck

Q

time

(mal)funzionamento di un positive edge triggered register

Si prescinde da come è realizzato realmente internamente il circuito e se ne valutano le

prestazioni in termini comportamentali, associando alla cella comportamento logico (in

termini di relazioni tra ingressi ed uscite) e parametri temporali corretti.

Carla Vacchi – Università degli Studi di Pavia

22

Edge triggered register con set e reset asincroni

È necessario che set e reset agiscano almeno sullo slave, ma è meglio se agiscono sia sul

master, sia sullo slave.

R

S

D

S Q

ck

Q

ETDFF

ck

R Q

D

0

1

1

0

Esempio di simbolo circuitale e di schema elettrico di positive edge triggered

register con segnali di set e reset asincroni, attivi alti.

tr,s

tempo di ritardo tra l’ingresso S o R e la variazione dell’uscita Q.

Carla Vacchi – Università degli Studi di Pavia

Q

23

Edge triggered register con set e reset sincroni

Per imporre un valore prefissato in uscita, si antepone all’ingresso del flip flop una rete

combinatoria controllata dai segnali SS e SR (Synchronous Set e Synchronous Reset).

SS

IN

D

SR

SS = 0 ed SR = 1:

SS = 0 ed SR = 0:

SS = 1 ed SR = 1:

Q

ETDFF

ck

SS = 1 ed SR = 0:

Q

Q

Q

Esempio di circuito con set e reset sincroni, attivi alti.

in ingresso al flip flop viene imposto un ‘1’ logico, che verrà

riportato in uscita alla prima transizione attiva del segnale di clock;

in ingresso al flip flop viene imposto uno ‘0’ logico, che verrà

riportato in uscita alla prima transizione attiva del segnale di clock;

in ingresso al flip flop viene riportato in segnale IN, che verrà

riportato in uscita alla prima transizione attiva del segnale di clock;

questa combinazione non deve essere permessa (i segnale SR e SS

non devono essere attivi contemporaneamente).

Carla Vacchi – Università degli Studi di Pavia

24

Reti sequenziali

elementi di logica combinatoria + elementi di memoria

in

C

M

C

M

C

M

C

M

out1

out2

Esistono dei vincoli alla frequenza massima di clock di un sistema sequenziale

ina

C

M

C

M

C

M outb

C

M

Carla Vacchi – Università degli Studi di Pavia

ina

D

Q

FF1

ck

outa

C

inb

D

Q

FF2

outb

25

aggiornamento ina al tempo t = tck1 + tck,q

aggiornamento inb al tempo t = tck1 + tck,q + td

inb deve essere stabile da almeno un tempo tsu prima che si presenti il fronte ck2

Tck

outa

ina

D

Q

inb

C

FF1

D

Q outb

FF2

ck

tck1

tck2

tck3

set

ck

ina ina1

I due fronti attivi del segnale

ck devono distare almeno

Tck,min = tck,q + td + tsu

quindi la frequenza massima

operativa del sistema è

outa

ina2

ina1

inb

ina2

ina1

outb

ina3

ina2

ina1

tck,q

tck,q

td

fmax,ck = 1/ Tck,min

ina2

tck,q

td

tsu

ck1

Carla Vacchi – Università degli Studi di Pavia

ina3

tsu

ck2

t

td

tsu

ck3

26

Tck,min = tck,q + td + tsu

( fmax,ck = 1/ Tck,min )

(verifica su th, tw (o tck/2,min) )

Tck,min

ck

tck1

tck2

in

tck3

C

M

C

M

C

M

C

M

out1

set

ina ina1

outa

ina2

ina1

inb

ina3

ina2

ina1

outb

ina3

ina2

ina1

tck,q

tck,q

td

ck1

out2

ina2

tck,q

td

t

td

tsu

tsu

ck2

ck3

tsu

Se esiste un vincolo su fck, e la rete non lo soddisfa, si ricorre ad architetture più

complesse (es approccio pipeline)

Carla Vacchi – Università degli Studi di Pavia

27

Registri

in3

D

Q

out 3

flip flop

o latch

in2

D

Q

out 2

flip flop

o latch

IN

OUT

in1

D

Q

out 1

flip flop

o latch

in0

D

Q

flip flop

o latch

load

Carla Vacchi – Università degli Studi di Pavia

out0

Registro = sistema nel quale è possibile

memorizzare più bit di informazione.

Consiste in un insieme di elementi di memoria

ordinati secondo una determinata sequenza.

Si possono caricare e scaricare informazioni

Segnale load comune

L’informazione è memorizzata in modo parallelo

ed è disponibile in uscita in modo parallelo

(PIPO register: Parallel IN, Parallel OUT)

28

Shift register

+ versatile: gli elementi di memoria (in genere flip flop) sono connessi in catena

D

in

Q

D

FF0

Q

D

FF1

Q

D

FF2

Q

out

FF3

ck

Ad ogni fronte attivo del segnale ck il segnale in viene traslato verso l’uscita.

Lo shift register ha una lunghezza m il dato impiega m periodi di clock per raggiungere l’uscita

La struttura può utilizzare tipi di flip flop con differenti strutture interne, o anche latches

Il sistema può avere grado di parallelismo n, con n = n° di bit che vengono elaborati in parallelo

Per ogni elemento della catena ci sono n flip flop in grado di memorizzare n bit.

in7

in6

in5

in4

in3

in2

in1

in0

D

IN

out7

out6

out5

out4

out3

out2

out1

ou0

OUT

Q

FF0

ck

Carla Vacchi – Università degli Studi di Pavia

D

Q

FF1

D

Q

FF2

D

Q

FF3

29

Modi per inizializzare un registro

▪ inizializzazione asincrona con il segnale set (o reset)

set

in3

in2

in1

D S Q

flip flop

D S Q

D S Q

flip flop

out3

in0

flip flop

out2

D S Q

flip flop

out1

out0

load

▪ inizializzazione sincrona:

in3

in2

0

in1

0

D

Q

D

VDD 1

Q

flip flop

Q

D

VDD 1

flip flop

out3

0

D

VDD 1

set sincrono

in0

0

flip flop

out2

Q

VDD 1

flip flop

out1

out0

load

in3

in2

0

in1

0

D

Q

VDD 1

D

GND

flip flop

load

Carla Vacchi – Università degli Studi di Pavia

out3

Q

1

0

D

GND

flip flop

out2

preset sincrono

in0

0

Q

1

D

Q

VDD 1

flip flop

out1

flip flop

out0

30

Modi per inizializzare uno shift register

▪ inizializzazione asincrona con il segnale set (o reset)

set

D

in

S Q

D

FF0

S Q

D

FF1

S Q

D

FF2

S Q

out

FF3

ck

▪ inizializzazione sincrona:

parallelo: ogni elemento di memoria viene inizializzato contemporaneamente

seriale: i flip flop vengono inizializzati in sequenza (set o reset stabile per m colpi di clock )

set sincrono

VDD

serial in

VDD

1

VDD

1

D

Q

0

VDD

1

D

Q

0

1

D

Q

0

FF0

D

Q

out

Q

out

0

FF1

FF2

FF3

ck

set sincrono

VDD

serial in

1

D

Q

D

Q

D

Q

D

0

FF0

ck

Carla Vacchi – Università degli Studi di Pavia

FF1

FF2

FF3

31

Possibilità di lettura/scrittura

SISO register:

Series IN , Series OUT

Architettura FIFO: First In, First Out

fck,lettura = fck,scrittura

fck,lettura fck,scrittura (buffering).

D

in

Q

D

FF0

Q

D

FF1

D

FF2

Q

out

FF3

ck

q0

SIPO register:

series IN, Parallel OUT

Q

in

D

Q

q1

D

FF0

Q

q2

D

FF1

Q

q3

D

FF2

Q

FF3

ck

PISO register:

parallel IN , series OUT

memorizza m dati con caricamento

parallelo

parallel load

p0

p1

1

D

serial in

Q

0

p2

1

D

Q

0

FF0

p3

1

D

0

FF1

1

Q

D

Q

out

0

FF2

FF3

ck

Esistono anche “registri universali”, che permettono, a seconda del valore assunto da due

bit di selezione, di effettuare shift a destra, a sinistra, caricamento serie o parallelo, etc.

Carla Vacchi – Università degli Studi di Pavia

32

ASIC (Standard Cells)

Celle di input/output

righe di celle standard

canali di routing

VDD

WP

in

out

VDD

in

INV

WN

Carla Vacchi – Università degli Studi di Pavia

out

2WP

in

out

2WN

VDD

in

INV2

out

4WP

in

out

4WN

in

INV4

out