Dipartimento di elettronica

Istituto Tecnico Statale “Luigi Einaudi” - Montebelluna

Reti elettriche lineari

Capitolo I – Metodi per la soluzione delle reti elettriche

Alessandro Bertelli – Mariano Zanchi

Riedizione a cura di Massimo Ballon

Dipartimento di Elettronica

I.T.S. “L. Einaudi” - Montebelluna

1

Reti elettriche

Sommario

1

Metodi per la soluzione delle reti elettriche .................................................................................. 4

1.1 Premessa ........................................................................................................................................ 5

1.2 I resistori e la legge di Ohm.......................................................................................................... 5

Esempio 1...................................................................................................................................... 6

1.3 Bipoli .............................................................................................................................................. 7

Esempio 2...................................................................................................................................... 8

1.4 Le leggi di Kirchhoff ..................................................................................................................... 8

Esempio 3...................................................................................................................................... 8

Prima legge di Kirchhoff................................................................................................................... 9

Esempio 4...................................................................................................................................... 9

Seconda legge di Kirchhoff............................................................................................................. 10

Esempio 5.................................................................................................................................... 10

Esempio 6.................................................................................................................................... 11

1.5 Connessioni tra resistori............................................................................................................. 11

Resistori in serie.............................................................................................................................. 11

Esempio 7.................................................................................................................................... 12

Partitore di tensione ........................................................................................................................ 13

Resistori in parallelo ....................................................................................................................... 14

Esempio 8.................................................................................................................................... 14

Partitore (o derivatore) di corrente.................................................................................................. 15

Esempio 9.................................................................................................................................... 16

1.6 Generatori ideali e reali.............................................................................................................. 17

Generatori di tensione ..................................................................................................................... 17

Esempio 10.................................................................................................................................. 18

Generatori di corrente ..................................................................................................................... 19

Esempio 11.................................................................................................................................. 20

1.7 Metodi per la soluzione delle reti elettriche.............................................................................. 20

Metodo di Kirchhoff ....................................................................................................................... 20

Esempio 12.................................................................................................................................. 21

Esempio 13.................................................................................................................................. 22

Metodo di sovrapposizione degli effetti.......................................................................................... 23

Esempio 14.................................................................................................................................. 23

Esempio 15.................................................................................................................................. 24

Metodo di Thevenin ........................................................................................................................ 25

Esempio 16.................................................................................................................................. 26

Esempio 17.................................................................................................................................. 26

1.8 Potenza elettrica .......................................................................................................................... 27

Bilancio energetico ......................................................................................................................... 27

Esempio 18.................................................................................................................................. 27

1.9 Caratteristiche elettriche dei resistori e cenni costruttivi ....................................................... 28

Esempio 19.................................................................................................................................. 29

Esempio 20.................................................................................................................................. 30

Tipologie ......................................................................................................................................... 30

Reti di resistenze ............................................................................................................................. 30

Dipartimento di elettronica

I.T.S. “L.Einaudi” - Montebelluna

2

Reti elettriche

Potenziometri .................................................................................................................................. 30

1.10 I segnali ...................................................................................................................................... 32

Esempio 21.................................................................................................................................. 33

Segnali periodici significativi ......................................................................................................... 34

APPENDICE 1 .................................................................................................................................. 38

A.1

I quadripoli e i generatori dipendenti.................................................................................. 38

Esempio 1.................................................................................................................................... 39

APPENDICE 2 .................................................................................................................................. 41

A.2 Altri metodi per la soluzione delle reti elettriche..................................................................... 41

Metodo di Norton............................................................................................................................ 41

Esempio 2.................................................................................................................................... 41

Esempio 3.................................................................................................................................... 42

Metodo di Millman ......................................................................................................................... 44

Esempio 4.................................................................................................................................... 45

Metodo di Miller ............................................................................................................................. 45

Esempio 5.................................................................................................................................... 46

ESERCIZI GUIDATI ....................................................................................................................... 47

ESERCIZI PROPOSTI .................................................................................................................... 67

LABORATORIO .............................................................................................................................. 73

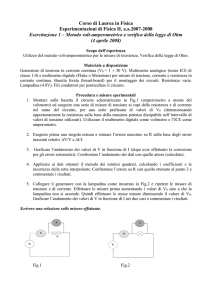

ESPERIENZA 1 Misura di resistenze ........................................................................................ 73

ESPERIENZA 2 Misura delle resistenze equivalenti di due reti ............................................... 74

ESPERIENZA 3 Misure di correnti e di tensioni ...................................................................... 74

ESPERIENZA 4 Misura di tensioni e correnti in una rete con due alimentatori........................ 75

ESPERIENZA 5 Verifica dei metodo di Thevenin .................................................................... 76

QUADRO RIASSUNTIVO .............................................................................................................. 79

Leggi e metodi per la soluzione delle reti elettriche....................................................................... 79

Potenza elettrica e bilancio energetico........................................................................................... 79

Connessioni di resistenze e partitori............................................................................................... 80

Dipartimento di elettronica

I.T.S. “L.Einaudi” - Montebelluna

3

Reti elettriche

1

Metodi per la soluzione

delle reti elettriche

In questa Unità di Apprendimento vogliamo offrire una panoramica sui principali metodi di

soluzione delle reti elettriche lineari, cioè sulle migliori strategie che consentano di

calcolare le grandezze elettriche incognite di una rete. Ci occuperemo quasi esclusivamente

di circuiti in regime continuo. Partiamo dalla legge di Ohm, seppur tale principio,

unitamente alla conoscenza dei resistori e del metodo di Kirchhoff, sia stato già proposto

nel corso di Fisica; questo per poter svolgere in modo più omogeneo e sicuro la trattazione

dei vari metodi. Vengono dati per assimilati però i concetti relativi al significato fisico delle

grandezze elettriche tensione e corrente.

OBIETTIVI

Conoscere e saper trasformare le unità di misura delle grandezze elettriche

Conoscere il componente resistore e saper effettuare l'equivalenza di gruppi di resistori

connessi in serie e/o in parallelo

Conoscere la differenza tra bipoli attivi e passivi

Conoscere, comprendere e saper applicare le leggi di Ohm e di Kirchhoff e i metodi di

sovrapposizione degli effetti e di Thevenin per la soluzione delle reti

Conoscere, comprendere e saper applicare i metodi di Norton, Millman e Miller

Conoscere i generatori di tensione e di corrente e comprendere la differenza tra elementi

ideali e reali

Saper effettuare il bilancio energetico in una rete elettrica con componenti passivi resistivi

Conoscere la tipologia dei segnali elettrici più importanti

Saper risolvere esercizi di soluzione di reti elettriche

Saper utilizzare gli strumenti di laboratorio per sperimentare le varie metodologie e per

effettuare le misure delle grandezze elettriche

Dipartimento di elettronica

I.T.S. “L.Einaudi” - Montebelluna

4

Reti elettriche

1.1 Premessa

Dando per acquisiti i concetti di tensione e corrente ricordiamo le unità di misura di queste due

grandezze elettriche.

La tensione si misura in volt [V], mentre la corrente in ampere [A].

In buona parte degli argomenti che verranno affrontati i valori delle correnti in gioco nei vari circuiti

sono al di sotto dell'ampere. Pertanto si ricorrerà ai suoi sottomultipli:

il milliampere [mA] fl 1 mA = 10-3 A

il microampere [µA] fl 1 mA = 10-6 A

Per la rappresentazione dei valori di tensione e di corrente si ricorrerà a caratteri maiuscoli nel caso

di regime continuo (tensioni e correnti costanti) o nelle occasioni in cui si vogliano indicare valori

istantanei particolari.

Per grandezze variabili nel tempo invece si utilizzeranno caratteri minuscoli.

Dal momento che questa Unità di Apprendimento è dedicata allo studio delle reti lineari in regime

continuo, per comodità di trattazione descriveremo le varie relazioni con lettere maiuscole; le leggi

rappresentate da tali relazioni sono comunque estendibili ai valori istantanei di tensioni e correnti

variabili nel tempo.

1.2 I resistori e la legge di Ohm

Il resistore è un elemento di circuito provvisto di due terminali (fig. 1) è pertanto un

bipolo ed è inoltre un componente passivo e lineare.

Per passivo intendiamo semplicemente dire che non ‘amplifica’ il segnale che lo attraversa; esso

inoltre dissipa potenza e la trasforma in calore per effetto Joule.

Con il termine lineare vogliamo invece evidenziare l'indipendenza del parametro R dal valore di

tensione applicata al resistore che identifica la relazione tra la corrente e la tensione.

Tale parametro è definito resistenza ed indica l'opposizione che il materiale conduttore offre al

passaggio di corrente.

La resistenza si misura in ohm [W], i cui multipli più usati sono

il chiloohm

il megaohm

[kW]

[MW]

fl 1 kW = 103 W

fl 1 MW = 106 W

I

I

I=

R

V

R

V

R

tgα =

1

R

a

0

Fig. 1 Simbolo elettrico

del resistore

Dipartimento di elettronica

I.T.S. “L.Einaudi” - Montebelluna

V

Fig. 3 Caratteristica voltamperometrica

del resistore

Fig. 2

5

Reti elettriche

La legge di Ohm

L'unità di misura della resistenza trova una diretta giustificazione nell'omonima legge e cioè la legge

di Ohm, la quale afferma che (fig. 2)

in un componente di resistenza R, al quale viene applicata una tensione (o differenza di

potenziale) V, circola una corrente di valore direttamente proporzionale a V ed

inversamente proporzionale ad R.

Tradotta in equazione, la legge di Ohm viene così descritta

I=

V

R

(1.1)

Dalla (1.1) appare evidente quindi che 1W corrisponde alla resistenza di un conduttore

sul quale circola la corrente di 1A quando ai suoi terminali viene applicata la tensione di

1V.

L'equazione (1.1) può essere inoltre rappresentata su un diagramma cartesiano da una retta passante

per l'origine e di coefficiente angolare 1/R (fig. 3). Tale retta individua la caratteristica

voltamperometrica del resistore di valore resistivo R.

Possiamo pertanto affermare che

quanto maggiore è il valore della resistenza, tanto minore risulta la pendenza della

retta che ne rappresenta la caratteristica voltamperometrica.

Esempio 1

In figura 4 sono disegnate le caratteristiche voltamperometriche di due resistori. Individuarne i valori di resistenza.

I(mA)

40

R1

30

R2

20

10

0

1

2

3

4

V(V)

Fig. 4

A tal proposito, per ciascuna caratteristica, basta individuare le coordinate (tensione e corrente) di un punto e poi

applicare la legge di Ohm.

Dipartimento di elettronica

6

I.T.S. “L.Einaudi” - Montebelluna

Reti elettriche

Per determinare la resistenza R1, associata alla retta con pendenza maggiore, possiamo ad esempio scrivere

1

R1 =

= 50Ω

20 ⋅10 − 3

Per R2 (identificata dalla retta con coefficiente angolare più basso) invece si ottiene

2

R2 =

= 200Ω

10 ⋅ 10 −3

1.3 Bipoli

Nel paragrafo precedente abbiamo definito il resistore un bipolo passivo, in quanto non in grado di

amplificare un segnale elettrico e quindi non in condizione di fornire ad esso energia.

Bipoli in grado di erogare potenza sono i generatori, che vengono considerati pertanto bipoli attivi.

In figura 5 sono schematizzati i simboli elettrici più comuni con i quali vengono rappresentati i

generatori ideali di tensione e di corrente.

Il primo a sinistra dei simboli di figura 5a rappresenta un elemento di batteria, cioè un generatore di

tensione continua, e sarà quello che con maggior frequenza troveremo in questa Unità Didattica.

L'elemento (elettrodo) più lungo rappresenta il terminale positivo. Negli schemi successivi faremo

quindi a meno di inserire il simbolo +.

Nei bipoli attivi (fig. 6) la corrente ‘esce’ dal terminale positivo, mentre nei bipoli passivi vi ‘entra’.

E’ possibile identificare la tensione anche con una freccia,

V

V

V

a)

V

i

i

i

b)

Fig. 5 Simboli elettrici di generatori: a) di tensione; b) di corrente.

in alternativa ai segni + e -; la sua punta indica il terminale positivo. In un resistore, e generalmente in

un bipolo passivo, le frecce di tensione e corrente sono in opposizione (fig. 7).

Può capitare anche che, in un particolare circuito nel quale siano presenti più generatori, uno di

questi si comporti da bipolo passivo e cioè assorba corrente (e potenza).

I

I

I

+

+

R

V

-

V

-

bipolo attivo

bipolo passivo

Fig. 6

Dipartimento di elettronica

I.T.S. “L.Einaudi” - Montebelluna

R

Fig. 7

7

Reti elettriche

Esempio 2

Nel circuito di figura 8 si individui il comportamento dei generatori di tensione presenti.

L'esempio fornisce già i valori e i versi delle correnti che entrano o escono dalle varie batterie.

Associando ad ogni generatore una freccia che indichi il verso della tensione e confrontando questa con la freccia relativa

alle correnti (fig. 9), possiamo affer mare che

2kW

1mA 5kW

3mA

4mA

4kW

15V

2V

5V

Fig. 8

— il generatore da 15V si comporta da bipolo attivo;

— il generatore da 5V si comporta da bipolo attivo;

— il generatore da 2V si comporta da bipolo passivo.

4mA

15V

Fig. 9

attivo

4mA

4mA

2V

5V

attivo

passivo

1.4 Le leggi di Kirchhoff

Risolvere una rete elettrica significa ricavare il valore delle grandezze incognite del relativo circuito

(spesso le correnti, ma anche resistenze o tensioni).

Per poter ora iniziare a fornire alcuni principi fondamentali che permettano di analizzare i circuiti

elettrici, dobbiamo indicare quali sono le parti essenziali che li compongono.

Si definisce nodo il punto di confluenza di tre o più elementi circuitali.

Si definisce ramo quella parte di circuito, costituita da uno o più elementi percorsi

dalla stessa corrente, che congiunge due nodi.

Si definisce maglia un percorso chiuso ottenuto passando attraverso più rami.

Esempio 3

Individuare i nodi, i rami e le maglie del circuito di figura 10.

Dipartimento di elettronica

I.T.S. “L.Einaudi” - Montebelluna

8

Reti elettriche

I nodi nel circuito sono due e li abbiamo indicati con le lettere A e B. I rami sono tre (fig. 11) e possiamo notare

come tutti confluiscano su entrambi i nodi; questo, e lo vedremo più avanti, ci consentirà di ricavare informazioni

utili per l'analisi del circuito solo da uno dei due nodi.

A

A

R1

A

A

R1

R2

R2

V1

V1

R3

R3

V2

V2

B

B

Fig. 10

Fig. 11

ramo 1

B

B

ramo 2

ramo 3

Le maglie sono ugualmente tre (fig. 12): la prima è costituita dai rami 1 e 2, la seconda dai rami 2 e 3 e la terza dai rami 1 e

3.

A

A

A

R1

R1

R2

R2

V1

R3

V2

B

Fig. 12

V1

R3

V2

B

maglia 1

B

maglia 2

maglia 3

Prima legge di Kirchhoff

A questo punto introduciamo la I legge (o principio) di Kirchhoff la quale afferma che

in un nodo la somma delle correnti entranti è uguale alla somma delle correnti

uscenti.

Esempio 4

Calcolare le correnti dei circuito di figura 13.

Dopo aver individuato i nodi nel circuito notiamo la presenza di tre rami e quindi di altrettante correnti da

calcolare, dal momento che su ogni ramo circola una corrente diversa.

Nel nodo A la corrente I entra, la I1e la I2 escono.

Applicando la legge di Ohm possiamo calcolare il valore di I1 e di I2; ai capi dei due resistori è applicata la stessa

tensione.

Quindi

I1 = 10/1000 = 0,01 A = 10 mA

I2 = 10/2000 = 0,005 A = 5 mA

La corrente 1, erogata dal generatore, applicando la I legge di Kirchhoff, vale

I = 11 + I2 = 10 + 5 = 15 mA

Dipartimento di elettronica

I.T.S. “L.Einaudi” - Montebelluna

9

Reti elettriche

L'equazione che porta al calcolo di I è la stessa che si ricaverebbe applicando la legge di Kirchhoff al nodo B, in

quanto in questo nodo confluiscono le stesse correnti del nodo A (per il nodo B la corrente I diventa uscente,

mentre I1 e I2 sono entranti).

I

A

I1

I2

1kW

10V

2kW

B

Fig. 13

Seconda legge di Kirchhoff

La II legge di Kirchhoff afferma che

in una qualsiasi maglia di una rete elettrica la somma algebrica delle tensioni è

nulla.

Questo principio può essere anche enunciato, qualora ogni ramo sia formato dalla serie di un

generatore ideale di tensione e di una resistenza, nel seguente modo:

in una maglia elettrica la somma algebrica delle forze elettromotrici associate ai

generatori è uguale alla somma delle cadute di tensione ai capi dei resistori.

Esempio 5

Applicare la II legge di Kirchhoff alle maglie individuate nel circuito di figura 8.

Per comodità abbiamo indicato in modo generico tensioni, correnti e resistenze del circuito di figura 8 e riportato in

figura 14 le tre maglie che costituiscono la rete.

Sono state inoltre segnate con delle frecce i versi delle tensioni in gioco.

Per poter tradurre in equazioni la legge di Kirchhoff alle tre maglie, si deve assegnare un verso di percorrenza a

ciascuna maglia in modo da individuare un riferimento per le tensioni da considerare positive; in figura 14 si

assume come positivo il verso orario.

R1

I1

V1

I3

I2

I2

R2

R2

R3

a

+

V3

Dipartimento di elettronica

I.T.S. “L.Einaudi” - Montebelluna

V1

b

V1 – R1I1 – R2I2 + V2 = 0

–V2 + R2 I2 – R3I3 – V3 = 0

V1 – R1I1 – R3I3 – V3 = 0

10

R3

1k

+

V2

Fig. 14

La seconda legge di Kirchhoff si trasforma nelle seguenti equazioni:

maglia a

maglia b

maglia c

I3

1k

+

V2

I1 R1

c

V3

Reti elettriche

Inserendo i valori numerici delle grandezze, riportate nello schema di figura 8, lo studente può effettivamente

verificare la validità delle tre equazioni.

Esempio 6

Ricorrendo alla seconda legge di Kirchhoff si determini la tensione VAB del circuito di figura 10 sapendo che

R2=500W, V2=9V e la corrente che circola nel ramo 2 (fig. 11) è diretta verso il nodo B e vale 4mA.

1

Ridisegniamo il ramo in questione come in figura 15.

Specifichiamo che per VAB si intende la differenza di potenziale esistente tra i punti A e B, cioè VA - VB e che si è

inserita, come riferimento di tensione positivo, una freccia che punta verso il primo dei due terminali del parametro

di tensione. Applicando ora il secondo principio di Kirchhoff alla maglia costituita dal bipolo A-B, formato da R2 e

V2 e chiusa mediante la VAB, possiamo scrivere

VAB – R2I + V2 = 0

A

I = 4 mA

R2 = 500 W

VAB

V2 = 9V

B

Fig. 15

da cui

VAB = R2I – V2 = 0,5 . 4 – 9 = –7 V

Il risultato negativo indica che il terminale A si trova ad un potenziale inferiore di 7 V rispetto al terminale B;

possiamo altresì dire che VBA = 7 V.

NOTA

Per snellire l'espressione, evitando di inserire la forma esponenziale, abbiamo espresso la resistenza in kW e la

corrente in mA. Lo faremo qualche volta anche in seguito. Si prega pertanto di fare sempre attenzione alle unità di

misura.

Si ricordi che 1 kW • 1 mA = 1 V.

1.5 Connessioni tra resistori

Per lo studio di una qualsiasi rete elettrica, prima di applicare i vari metodi di analisi, é molto spesso

conveniente, qualora ve ne sia la possibilità, semplificare il circuito andando a sostituire gruppi di

resistori con il loro valore equivalente. Ciò é possibile se tali elementi sono connessi in serie o in

parallelo.

Resistori in serie

Due o più resistori si dicono in serie se sono percorsi dalla stessa corrente (fig. 16).

Nel caso di N resistori in serie, la resistenza equivalente a tale gruppo, indicata con Req, risulterebbe

Dipartimento di elettronica

I.T.S. “L.Einaudi” - Montebelluna

11

Reti elettriche

Req = R1 + R2 + ... + R N

(1.2)

Questo vuol dire che, se al posto degli N resistori in serie ne viene inserito uno di valore ohmico

equivalente, determinato tramite l'equazione (1.2), i valori di tensione e di corrente del bipolo non

vengono modificati.

I

I

R1

R2

VAB

VAB

Req = R1 + R2 + ... + R N

RN

Fig. 16

Esempio 7

Verificare che i bipoli A-B negli schemi di figura 17 sono equivalenti.

Siano:

R1 = 250 W

R2 = 300 W

R3 = 400 W

La resistenza equivalente alla serie tra R1, R2 ed R3 risulta

Req = 250 + 300 + 400 = 950 Q.

Per verificare l'equivalenza dei bipoli A-B determiniamo la tensione VAB e la corrente I dei due circuiti di figura

17.

Mediante la II legge di Kirchhoff, applicata allo schema di figura 17a, possiamo scrivere

10 − 50 I − R1 I − R 2 I − R3 I = 0

da cui, inserendo i valori delle grandezze, otteniamo

I=

10

= 0,01A = 10mA

50 + 250 + 300 + 400

Stesso risultato ricaviamo per lo schema di figura b, inserendo nell'equazione alla maglia il termine R eq I al posto di

R1 I + R 2 I + R3 I . Infatti

R1 I + R 2 I + R3 I = (R1 + R 2 + R3 )I = Req I

Per questo motivo anche le tensioni VAB sono identiche, in quanto

V AB = R1 I + R 2 I + R3 I = Req I = 950 ⋅ 0,01 = 9,5V

Dipartimento di elettronica

I.T.S. “L.Einaudi” - Montebelluna

12

Reti elettriche

A

A

I

I

R1

50W

50W

VAB

VAB

R2

Req

10V

10V

R3

B

B

R eq = R1 + R 2 + R3

a)

b)

Fig. 17

Partitore di tensione

Allorquando si voglia calcolare la tensione ai capi di un resistore costituente l'elemento di una serie,

conoscendo la tensione complessiva e non avendo interesse a determinare la corrente circolante nel

ramo (fig. 18), é possibile ricorrere ad una semplice formula diretta. Questa deriva dal fatto che

in un gruppo di resistori posti in serie la tensione si ripartisce su di essi in modo

direttamente proporzionale a ciascuna singola resistenza

Tale utile espressione risulta

VR = V

R

Req

(1.3)

V

coincide con la corrente circolante nella serie ed Req , nel caso di figura 18, risulta

Req

Req = R1 + R + R2 .

dove il termine

R1

R

V

R2

Fig.18

Dipartimento di elettronica

I.T.S. “L.Einaudi” - Montebelluna

13

VR

Reti elettriche

Resistori in parallelo

Due o più resistori sono connessi in parallelo se si trovano sottoposti alla stessa

differenza di potenziale (fig. 19).

Per calcolare la resistenza equivalente di un gruppo di N resistori in parallelo si applica la seguente

formula

1

1

1

1

=

+

+ ... +

Req R1 R2

RN

(1.4)

che, per sole due componenti, si riduce all'espressione

Req =

R1 R2

R1 + R2

(1.5)

A

A

R1

R2

RN

VAB

Req

VAB

B

b)

a)

B

Fig. 19

Nel caso si debba calcolare la resistenza equivalente di tre o più elementi si applichi l'equazione

(1.4) oppure si esegua un primo parallelo tra due resistenze, ponendo il risultato nell'espressione di

parallelo con il terzo componente; si prosegua seguendo lo stesso criterio con il nuovo risultato posto

in parallelo con l'eventuale quarto elemento e così via.

Il secondo metodo è indicato nel caso in cui le varie operazioni di parallelo possano essere eseguite

con un veloce calcolo mentale.

E’ facilmente verificabile inoltre che la resistenza equivalente di un parallelo

composto da N resistenze di ugual valore R è pari a R/N.

Esempio 8

Calcolare la resistenza equivalente della rete di figura 20a.

Applicando l'equazione (1.4) ricaviamo

Dipartimento di elettronica

I.T.S. “L.Einaudi” - Montebelluna

14

Reti elettriche

1

1 1 1

1

= + + =

Req 15 10 6 3kΩ

Req = 3kΩ

da cui

Al risultato appena determinato potevamo giungere eseguendo i passaggi mostrati nelle figure 20: prima il parallelo

tra i resistori da 15 e 10 kW, con valore equivalente, ricavato dall'applicazione della (1.5), pari a 6 kW; poi il

parallelo tra 6 kW e 6 kW con risultato finale 6/2 = 3 kW.

15kW

10kW

6kW

15//10 = 6kW

6kW

a)

6//6 = 6/2 = 3kW

c)

b)

Fig. 20

Partitore (o derivatore) di corrente

Consideriamo ora la connessione in parallelo di due resistori (fig. 21). Si vogliano calcolare le

correnti in ciascun ramo conoscendo quella che confluisce nel nodo; possiamo scrivere

I1 =

V

R1

I2 =

(1.6)

dove

V = IReq = I

R1 R2

R1 + R2

V

R2

(1.7)

(1.8)

I

I1

I2

R1

V

R2

Fig. 21

Sostituendo al termine V l'espressione a destra dell'equazione (1.8), prima nella (1.6) e poi nella

(1.7), otteniamo

Dipartimento di elettronica

I.T.S. “L.Einaudi” - Montebelluna

15

Reti elettriche

I1 = I

R2

R1 + R2

(1.9)

I2 = I

R1

R1 + R2

(1.10)

Operando una divisione membro a membro tra la (1.9) e la (1.10) o tra la (1.6) e la (1.7) osserviamo

che

I 1 R2

=

I 2 R1

(1.11)

Possiamo dunque affermare che

le correnti circolanti su ciascun resistore di un parallelo stanno tra loro come le

resistenze dei rami opposti.

A conclusione del paragrafo risolviamo il problema proposto nel seguente esempio.

Esempio 9

Del circuito di figura 22 determinare il valore di tutte le correnti e delle tensioni incognite.

• Resistenza equivalente vista dal generatore: Req

Req = [2,6 + (6 // 4)] // 5 = 2,5 kW

(con il simbolo // indichiamo il parallelo tra due resistori)

• Corrente erogata dal generatore: I

I=

5

VG

=

= 2mA

Req 2,5 ⋅ 10 3

• Resistenza complessiva ramo sinistro: Rs

Rs = 2,6 + (6 // 4) = 5 kW

• Correnti su 2,6 kW (ramo sinistro) e sui 5 k W (ramo destro): Is e Id

A

2,6kW

B

6kW

VG

VG = 5V

4kW

C

C’

Fig. 22

Dipartimento di elettronica

I.T.S. “L.Einaudi” - Montebelluna

16

5kW

Reti elettriche

Le due correnti sono uguali e pari a 1 mA, cioè la metà di quella totale, in quanto le resistenze dei rami sinistro

e destro hanno lo stesso valore.

• Tensione sui 2,6 kW: VAB

Applichiamo la formula (1.3) del partitore di tensione

V AB = 5 ⋅

2,6

2 ,6

= 5⋅

= 2,6V

2,6 + (6 // 4 )

2,6 + 2,4

• Tensione sul parallelo: VBC

I nodi C e C' sono equipotenziali e sul tratto di conduttore che li congiunge, considerato di resistenza nulla,

circola la corrente IS.

V BC = VG − V AB = 5 − 2,6 = 2,4V

• Correnti nei due rami del parallelo:I6k e I4k

Applicando il partitore di corrente

I 6k = I s ⋅

4

= 0,4mA

4+6

I 4k = I s ⋅

6

= 0,6mA

4+6

1.6 Generatori ideali e reali

I generatori trattati in questa Unità di Apprendimento vengono definiti indipendenti in quanto la

grandezza da loro prodotta non è legata a tensioni o correnti presenti in altri punti dei vari circuiti.

Si differenziano tra loro sia per la grandezza generata sia per il modello ideale o reale al quale fare

riferimento.

I generatori definiti dipendenti verranno brevemente analizzati nell'Appendice 1.

Generatori di tensione

IDEALI

Un generatore di tensione si dice ideale se fornisce una tensione indipendente dalla

corrente erogata e non condizionata quindi dal valore ohmico del carico che viene

alimentato

La caratteristica V-I di tale dispositivo (dove la tensione costituisce la variabile dipendente) é

pertanto quella di figura 23 ed è rappresentata da una semiretta parallela all'asse delle correnti (ascisse).

a)

VG

b)

IO

VO

VG

VO

RL

IO

Fig. 23 Generatore ideale di tensione

Dipartimento di elettronica

I.T.S. “L.Einaudi” - Montebelluna

17

Reti elettriche

REALI

La tensione prodotta da un generatore in realtà diminuisce all'aumentare della corrente erogata.

Questo fenomeno può essere notato soprattutto per bassi valori ohmici del carico RL.

Un generatore reale di tensione può essere pertanto schematizzato con la serie tra un dispositivo

ideale e la sua resistenza interna RO, coincidente con quella di uscita se si guarda dal carico verso il

generatore (fig. 24a).

a)

b)

IO

VO

pendenza = -RO

VG

RO

VO

RL

VG

VG /RO

IO

Fig. 24 Generatore reale di tensione

La tensione VO, corrisponde a quella del generatore ideale (VG) solo nel caso in cui il carico risulti

scollegato (connessione a vuoto).

Generalmente invece si ha che

VO = VG - ROIO

(1.12)

L'espressione (1.12) si trasforma graficamente nella retta di figura 24b, che rappresenta la

caratteristica voltamperometrica del generatore.

Il valore della corrente in corrispondenza di VO = 0 si ottiene cortocircuitando l'uscita, è pari a VG/RO

ed è generalmente indicato con ICC (corrente di cortocircuito).

Esempio 10

Determinare il valore della tensione prodotta da un generatore reale su un carico di 250W sapendo che la tensione a

vuoto è 12V e la corrente con l'uscita in cortocircuito è 240mA.

Conoscendo il valore della corrente di cortocircuito possiamo determinare la resistenza interna del generatore.

RO =

VG

12

=

= 50Ω

I CC 0,24

Per calcolare la tensione di uscita con un carico di 250 W si può ricorrere alla formula del partitore di tensione

(eq.l.3) e quindi

VO = VG

RL

250

= 12 ⋅

= 10V

RO + RL

300

valore inferiore a quello a vuoto.

Da quanto esposto si deduce che.

affinché la tensione prodotta da un generatore possa essere considerata

indipendente dalla corrente erogata, la resistenza interna deve essere trascurabile

rispetto al valore ohmico minimo assunto dal carico (RO ideale = 0).

Dipartimento di elettronica

I.T.S. “L.Einaudi” - Montebelluna

18

Reti elettriche

Generatori di corrente

IDEALI

Vengono definiti così quei dispositivi in grado di erogare una corrente di valore

indipendente dalla tensione ai loro morsetti e quindi non condizionata dal valore

ohmico di un eventuale carico.

La caratteristica voltamperometrica di questo tipo di generatore di corrente (fig. 25) è rappresentata

pertanto da una semiretta parallela all'asse delle tensioni (ascisse).

a)

b)

IO

IG

IO

IG

VO

RL

VO

Fig. 25 Generatore ideale di corrente.

REALI

La corrente erogata da questi generatori è in realtà dipendente dalla tensione presente tra i loro

terminali. Collegando un carico, quanto più questo assume valore ohmico elevato, tanto minore rispetto

al valore ideale risulta la corrente erogata. Questo effetto può essere pertanto schematizzato attraverso

un resistore posto in parallelo al generatore ideale e che identifica la resistenza interna del

dispositivo(fig. 26a).

Questa resistenza interna sottrae al carico una parte della corrente; il dispositivo eroga una corrente

pari a quella ideale solo in situazione di carico in cortocircuito. Vale la relazione

V

IO = IG − O

(1.13)

RO

che si trasforma graficamente nella caratteristica voltamperometrica mostrata in figura 26b dove, per

I O = 0 (connessione a vuoto), VO = RO I G .

a)

b)

IO

IO

pendenza = −

1

RO

IG

IG

RO

VO

RL

ROIG

Fig. 26 Generatore reale di corrente.

Dipartimento di elettronica

19

I.T.S. “L.Einaudi” - Montebelluna

VO

Reti elettriche

Esempio 11

Un generatore eroga una corrente di cortocircuito di 100mA mentre su un carico di 100W fornisce 90mA. Quanto

vale la sua resistenza interna?

La corrente IG del generatore ideale corrisponde a quella di cortocircuito e vale quindi 100mA.

Con il carico di 100W. sulla resistenza interna circola una corrente I pari a

I = 100 - 90 = l0mA

Dal momento che la tensione di uscita è

VO = RLIO = 100 . 0,9 = 9V

la resistenza interna vale

RO =

VO

9

=

= 900 Ω

I

0,01

Da quanto è stato detto si deduce che, affinché la corrente erogata da un generatore

sia pressoché indipendente dal carico, la resistenza interna (in parallelo) deve

assumere un valore elevato e tale da rendere trascurabile quella del carico stesso.

1.7 Metodi per la soluzione delle reti elettriche

Analizziamo ora alcuni tra i metodi più diffusi e pratici che permettono di determinare le grandezze

incognite di un circuito elettrico (o rete elettrica).

Metodo di Kirchhoff

Nel paragrafo 1.4 sono state proposte le due leggi di Kirchhoff, che si traducono la prima in

equazioni ai nodi (tante quante sono i nodi della rete meno uno), la seconda in equazioni alle maglie

(tante quante sono le maglie).

Per risolvere una rete elettrica, e cioè per determinare le grandezze incognite di un

circuito sotto analisi, è pertanto necessario individuare e scrivere un numero di

equazioni pari a quello delle grandezze da calcolare.

• Le equazioni possono essere scelte tra tutte quelle possibili, ai nodi e/o alle maglie, e devono

contenere tutte le incognite.

• Le equazioni formeranno un sistema che, risolto, fornirà il valore delle grandezze incognite.

• Prima di scrivere le equazioni ai nodi assegnare un verso arbitrario alle correnti incognite di tutti i

rami. Nel caso in cui, durante lo sviluppo del sistema, venissero determinate alcune correnti con

segno negativo, continuare lo svolgimento del sistema mantenendo lo stesso segno; ciò significherà

solo che il vero verso della corrente calcolata é opposto a quello fissato.

• Prima di scrivere le equazioni alle maglie fissare arbitrariamente un verso di percorrenza in modo da

individuare il riferimento positivo per le tensioni (come fatto nelle figure 14 dell'esempio 5).

Dipartimento di elettronica

I.T.S. “L.Einaudi” - Montebelluna

20

Reti elettriche

Esempio 12

Risolvere la rete di figura 27 calcolando le correnti circolanti in ogni ramo.

1kW

3kW

18V

2kW

19V

1,5kW

3V

Fig. 27

Le correnti da calcolare sono tre, quanti i rami del circuito. Devono essere tre pertanto anche le equazioni da

individuare ed inserire nel sistema da risolvere. Riferendoci allo schema di figura 28, possiamo scegliere

l'equazione al nodo A e le equazioni alle due maglie interne a e b.

Come si può notare abbiamo provveduto ad evidenziare le tre correnti incognite, assegnando loro un verso

arbitrario, e fissato un riferimento di tensione positivo per le due maglie.

Si faccia attenzione inoltre che in questo esempio le resistenze vengono espresse in kW e le correnti in mA.

1kW

A

I1

I3

3kW

I2

18V

2kW

+

+

19V

1,5kW

a

b

3V

Fig. 28

Il sistema risulta perciò il seguente:

⎧ I1 = I 2 + I 3

⎪

⎨18 − 1I 1 − 2 I 2 − 3 − 1,5 I 1 = 0

⎪2 I − 3I − 19 = 0

3

⎩ 2

equazione nodo A

equazione maglia a

equazione maglia b

Svolgiamo ora il sistema

⎧

⎪ I1 = I 2 + I 3

⎪

⎨ 15 − 2,5 I1 − 2 I 2 = 0

2 I 2 − 19

⎪

⎪⎩ I 3 =

3

Dipartimento di elettronica

I.T.S. “L.Einaudi” - Montebelluna

21

Reti elettriche

2 I 2 − 19 5 I 2 − 19

⎧

=

⎪ I1 = I 2 +

3

3

⎪⎪

2,5

(

)

15

−

5

−

19

−

2

I

I

2

2 =0

⎨

3

⎪

⎪ I 3 = 2 I 2 − 19

⎪⎩

3

Ricavando I2 dalla seconda equazione possiamo poi determinare il valore delle altre due correnti; otteniamo

dunque:

I1 = 2mA

I2 = 5mA

I3 = -3mA

La corrente I3 risulta pertanto entrante nel nodo A e non uscente come fissato in partenza.

Esempio 13

Calcolare le correnti e la resistenza R nel circuito di figura 29.

In questo caso le correnti incognite sono due in quanto la terza è quella imposta dal generatore da 2,5 mA.

1kW

I2

A

4kW

VAB = 5V

I = 2,5mA

I1

I

VAB

R

3V

B

Fig. 29

Servono comunque tre equazioni; si faccia però attenzione a non utilizzare quella della maglia che contiene il

generatore di corrente, in quanto la tensione ai suoi capi, di cui non viene richiesto il calcolo, diventerebbe una

quarta incognita.

Si potrebbero quindi in forma rigorosa scrivere le tre equazioni e risolvere il sistema. Se osserviamo bene lo

schema ci accorgiamo però che possiamo di volta in volta individuare una equazione contenente una sola incognita,

la quale può essere pertanto immediatamente calcolata.

L'equazione alla maglia destra (fissato ad esempio come verso di percorrenza quello orario) infatti ci permette

direttamente di calcolare I2, in quanto

V AB − 4 ⋅10 3 I 2 − 3 = 0

da cui

I2 =

5−3

= 0,5mA

4 ⋅ 103

Ora che conosciamo I2, applicando l'equazione al nodo A, possiamo calcolare I1; infatti

I = I1 + I 2

da cui

I1 = I − I 2 = 2,5 − 0,5 = 2mA

Infine, applicando semplicemente la legge di Ohm, determiniamo R.

R=

V Ab

5

=

= 2,5kΩ

I1

2 ⋅ 10 −3

Fino a quando l'allievo non ha acquisito una buona dimestichezza nell'analisi delle reti, anche in problemi come

questo è consigliabile scrivere inizialmente l'intero sistema.

Dipartimento di elettronica

I.T.S. “L.Einaudi” - Montebelluna

22

Reti elettriche

Metodo di sovrapposizione degli effetti

E’ possibile calcolare una o più grandezze di una rete lineare considerando

separatamente l’effetto prodotto da ciascun generatore presente nel circuito,

annullando ogni volta l'azione degli altri generatori.

Annullare l'azione dei generatori significa:

-

cortocircuitare i generatori di tensione;

-

aprire i rami in cui sono inseriti i generatori di corrente.

I vari effetti dovranno successivamente essere sommati algebricamente; si terrà cioè conto, per

ciascuno di essi, del verso assunto dal parametro incognito rispetto a quello di riferimento.

Esempio 14

Calcolare con il metodo di sovrapposizione degli effetti la corrente I indicata nello schema di figura 30.

1,5kW

3kW

I

V18

3kW

15V

12V

Fig. 30

Effetto del generatore da 15 V (fig.31a)

I.

(generatore da 12 V cortocircuitato)

Si calcola IG:

IG =

15

= 5mA

[(3 // 3) + 1,5]⋅ 103

Si calcola I’ applicando il partitore di corrente:

I'=

IG

= 2,5mA

2

3kW

1,5kW

IG

I’

3kW

15V

I’’

1,5kW

3kW

3kW

12V

IG

Fig. 31

a)

b)

II. Effetto del generatore da 12 V (fig. 31b)

(generatore da 15 V cortocircuitato)

Si calcola IG:

Dipartimento di elettronica

I.T.S. “L.Einaudi” - Montebelluna

23

Reti elettriche

IG =

12

[(1,5 // 3) + 3]⋅ 103

= 3mA

Si calcola I’’ applicando il partitore di corrente:

I '' = 3 ⋅

1,5

= 1mA

1,5 + 3

I due effetti presentano verso opposto; il primo è concorde con quello assegnato in figura 30 e può quindi essere

considerato positivo, pertanto

I = I '− I ' ' = 2,5 − 1 = 1,5mA

Esempio 15

Calcolare con il metodo di sovrapposizione degli effetti la tensione VR ai capi del resistore da 6 kW nel circuito di

figura 32.

4kW

6kW

2mA

VR

12V

Fig.32

I. Effetto del generatore di corrente (fig. 33a)

(generatore di tensione cortocircuitato)

VR ' = 2 ⋅ 10 −3 ⋅ (6 // 4) ⋅ 103 = 4,8V

4kW

4kW

2mA

VR’’

6kW

6kW

VR’

12V

Fig. 33

b)

a)

II. Effetto del generatore di tensione (fig. 33b)

(ramo con il generatore di corrente aperto)

Dipartimento di elettronica

I.T.S. “L.Einaudi” - Montebelluna

24

Reti elettriche

VR ' ' = 12 ⋅

6

= 7,2V

6+4

I due effetti presentano versi opposti; il secondo è concorde con quello di figura 32 e può essere considerato

positivo, pertanto

VR = VR ' '−VR ' = 7,2 − 4,8 = 2,4V

Metodo di Thevenin

Questo metodo deriva dall' applicazione del teorema di Thevenin, il quale afferma che

una qualsiasi rete elettrica lineare vista da due terminali può essere rappresentata in

modo equivalente da un bipolo costituito da un generatore di tensione ideale (Veq) in

serie ad una resistenza (Req).

Req

A

rete

elettrica

lineare

RL

B

A

RL

Veq

B

a)

b)

Fig. 34

In figura 34 abbiamo supposto la rete elettrica chiusa su un semplice resistore (RL), ma a destra del

bipolo A-B poteva essere presente un'altra rete più o meno complessa.

• La Veq si determina calcolando la tensione a vuoto presente tra i due terminali di uscita della rete da

semplificare (fig. 35a). ‘A vuoto’ significa aver staccato la restante parte del circuito collegata al

bipolo in questione.

A

rete

elettrica

lineare

Veq = VAB (a vuoto)

a)

B

annullati

i generatori

indipendenti

Req

b)

Fig. 35

• La Req é la resistenza vista dal bipolo, guardando verso la rete da semplificare (fig. 35b), dopo aver

annullato i generatori indipendenti (nel caso di generatori dipendenti vedere Appendice 1).

Dipartimento di elettronica

I.T.S. “L.Einaudi” - Montebelluna

25

Reti elettriche

Esempio 16

Semplificare con il metodo di Thevenin la rete a sinistra dei terminali A-B nel circuito di figura 36.

6kW

1kW

6kW

12kW

9V

Req

A

A

6kW

Veq

RL

RL

B

B

b)

a)

Fig. 36

Per determinare Veq scollegare il resistore RL e calcolare la VAB a vuoto. Questa tensione coincide con quella ai

capi del resistore da 12 kW in quanto su quello da l kW, avendo aperto il suo ramo, non scorre corrente.

Veq = V AB ( a vuoto ) = 9 ⋅

12

= 6V

12 + 6

La Req è quella compresa tra A e B dopo aver cortocircuitato il generatore di tensione (fig. 37) e vale

Req = (6 // 12) + 1 = 5kΩ

1kW

A

12kW

6kW

Req

B

Fig. 37

A questo punto, se occorresse determinare la tensione o la corrente relative al resistore R, basterà ricostituire la

maglia come in figura 36b.

Esempio 17

Determinare il circuito equivalente di Thevenin perla rete vista dai morsetti A e B di figura 38a.

Nel circuito proposto potremmo applicare direttamente il metodo, di sovrapposizione degli effetti per determinare

la Veq da inserire nello schema di figura 38c. Preferiamo però usare questo esempio per proporre una doppia

applicazione del teorema di Thevenin.

Trasformiamo prima la rete costituita dal generatore di corrente e dalla resistenza da 10 kW, aprendo il circuito nel

modo mostrato in figura 38a, per giungere così allo schema di figura 38b. Cosi facendo passiamo dalla tipica

configurazione di un generatore reale di corrente a quella altrettanto caratteristica di un generatore reale di tensione

(Veq’ in serie a Req’).

Veq’ = V10kW = 10V

(con il generatore di corrente aperto)

Req’ = 10kW

Si arriva infine allo schema di figura 38c, calcolando la Veq ricorrendo al metodo di sovrapposizione degli effetti e

la Req cortocircuitando i due generatori di tensione.

Otteniamo quindi

Dipartimento di elettronica

I.T.S. “L.Einaudi” - Montebelluna

26

Reti elettriche

Veq = V AB = 10 ⋅

15

10

+ 4⋅

= 7,6V

10 + 15

10 + 15

(abbiamo inserito nell'espressione direttamente entrambi gli effetti, calcolati applicando il partitore di tensione)

Req = 10 // 15 = 6 kW

Req’

A

4V

1mA

Req

A

A

4V

10kW

Veq’

Veq

15kW

15kW

B

B

B

a)

b)

c)

Fig. 38

1.8 Potenza elettrica

La potenza associata ad un bipolo elettrico è data dal prodotto tra la tensione e la corrente ad

esso relative e si misura in watt [W].

L' espressione

p = vi

(1.14)

descritta con lettere minuscole, indica la potenza calcolata in ogni istante su un elemento interessato da

grandezze elettriche genericamente variabili nel tempo.

In regime continuo invece scriveremo

P = VI

(1.15)

Le equazioni (1.14) e (1.15) sono adatte soprattutto nel caso di potenza erogata da un generatore.

Volendo invece determinare la potenza dissipata in regime continuo da un resistore di resistenza R,

per il quale V e I rappresentano rispettivamente la tensione ai suoi capi e la corrente in esso circolante,

oltre alla (1.15) possiamo utilizzare le seguenti espressioni

P = VI = (RI )I = RI 2

V V2

P =V ⋅ =

R

R

(1.16)

(1.17)

Bilancio energetico

In una rete elettrica la somma algebrica delle potenze associate ai generatori è

uguale alla somma aritmetica delle potenze dissipate dai resistori.

Nella definizione abbiamo indicato la somma algebrica per le potenze dei generatori perché, come

già accennato, in alcuni casi questi possono comportarsi come elementi passivi.

Esempio 18

Eseguire il bilancio energetico della rete di figura 39.

Dipartimento di elettronica

27

I.T.S. “L.Einaudi” - Montebelluna

Reti elettriche

R1

IG

VG

R2

R3

VG = 8 V

R1 = 800 W

R2 = 2 k W

R3 = 3 k W

Fig. 39

• Calcoliamo la potenza erogata dal generatore: PG

(è uno solo, pertanto sicuramente eroga potenza)

Per fare questo determiniamo la corrente IG uscente dal suo polo positivo e che circola anche su R1.

IG =

VG

VG

8

=

=

= 4mA

R eq R1 + R 2 // R3 2 ⋅10 3

Pertanto

PR1 = VG I G = 8 ⋅ 4 ⋅10 −3 = 32mW

• CalcoIiamo le potenze relative ai tre resistori.

Prima però determiniamo la tensione sul parallelo tra R2 ed R3, sapendo che R2 // R3 = 1,2kW.

Per cui

V // = 8 ⋅

1,2

= 4,8V

1,2 + 0,8

PR1 = R1 I G2 = 12,8mW

PR2 =

V//2

= 11,52mW

R2

PR3 =

V//2

= 7,68mW

R3

Quindi è verificato l'equilibrio tra potenza erogata e potenza dissipata, infatti

12,8 + 11,52 + 7,68 = 32

1.9 Caratteristiche elettriche dei resistori e cenni costruttivi

Proponiamo ora alcune caratteristiche elettriche relative ai resistori in commercio e fornite dalle case

costruttrici.

Resistenza nominale: assume valori standard in base a determinate serie, ciascuna composta secondo

le norme IEC da particolari tagli.

Nella tabella 1 sono riportati i valori delle serie E-12 ed E-24, anche se in commercio sono

inoltre disponibili le E-6, E-48, E-96 ed E-192

Tolleranza: la resistenza nominale rappresenta un valore indicativo, ma non reale dei componente.

In effetti il valore effettivamente misurato di un elemento può discostarsi da quello nominale.

Il massimo errore relativo, espresso in percentuale, è indicato con il termine tolleranza.

In molti tipi di resistori la lettura dei valori di resistenza nominale e di tolleranza è deducibile

dall'interpretazione di una serie di anelli di diversa colorazione (fig. 40) che costituiscono un

vero e proprio codice colori (che riportiamo nella tabella 2).

Dipartimento di elettronica

I.T.S. “L.Einaudi” - Montebelluna

28

Reti elettriche

Tabella 1

Serie E-12

10

-12

-15

-18

-22

-27

-33

-39

-47

-56

-68

-82

--

Tabella 2

Serie E-24

10

11

12

13

15

16

18

20

22

24

27

30

33

36

39

43

47

51

56

62

68

75

82

91

Colori

Assente

Argento

Oro

Nero

Marrone

Rosso

Arancio

Giallo

Verde

Blu

Viola

Grigio

Bianco

Prime due

cifre

---0

1

2

3

4

5

6

7

8

9

Fattore

esponenziale

-10-2

10-1

100

101

102

103

104

105

106

----

Tolleranza %

20

10

5

-1

2

--------

Tolleranza

1a cifra

a

2 cifra

Fattore esponenziale

Fig. 40

Ad esempio nelle serie E-12 ed E-24 gli anelli che identificano la resistenza sono tre, i primi due

codificano il coefficiente moltiplicativo, il terzo indica il fattore esponenziale, mentre un quarto

é relativo alla tolleranza. A tal proposito svolgere l’esempio 19 proposto più avanti.

Potenza dissipabile: è la massima potenza che il componente può dissipare ad una determinata

temperatura ambiente (70° C).

Coefficiente di temperatura: rappresenta la variazione relativa di resistenza nominale in

corrispondenza di uno scarto termico di 1° C. Viene indicato con TC, e spesso è espresso in

ppm/°C (ppm = parti per milione del valore nominale, cioè 1 . 10-6 . Rnom)

Campo di temperature di esercizio: rappresenta l’intervallo di temperature di lavoro ammesso per il

componente (ad esempio da -55 a + 125 °C)

Tensione massima: massima tensione di lavoro applicabile al componente

Esempio 19

Determinare i valori di resistenza e di tolleranza dei resistori di figura 41a e b.

argento

giallo

viola

oro

a)

verde

Fig. 41

Dipartimento di elettronica

I.T.S. “L.Einaudi” - Montebelluna

oro

marrone

29

arancio

b)

Reti elettriche

a) Giallo – viola - oro/argento = 47 ◊ 10-1 ± 10%

per cui 4,7W e ± 10% di tolleranza

Il vero valore può essere compreso quindi tra 4,23 e 5,17 W.

b) Marrone – verde - arancio/oro = 15 ◊ 103 ± 5%

per cui 15 kW e ± 5% di tolleranza

Il vero valore può essere compreso quindi tra 14,25 e 15,75 kW.

Esempio 20

Calcolare la massima variazione di resistenza di un componente di valore nominale 1 kW, con coefficiente di

temperatura Tc, pari a 200 ppm/°C, in corrispondenza di uno scarto termico di 20 °C.

La formula, dedotta dalla definizione di coefficiente di temperatura, da applicare per calcolare DR è

DR = Tc ◊ Rnom ◊ DT = 200 ◊ 10-6 ◊ 1000 ◊ 20 = 4 W

Tipologie

Le attuali tecniche costruttive vedono prevalere soprattutto i resistori a film (o a strato) e i resistori

a filo.

I primi (fig. 42) sono costituiti da un sottile strato di materiale conduttivo (metallo, ossido di

metallo, carbone, cermet = ceramica + metallo) avvolto su un cilindretto di materiale isolante

(porcellana).

Fig. 42 Resistori a film.

Il valore ohmico di resistenza viene realizzato attraverso una particolare operazione di tornitura.

Per potenze superiori al watt si ricorre ai resistori a filo (fig. 43), costituiti da un elemento

conduttivo avvolto e immerso in un corpo di ceramica. Per potenze dalla decina di watt in su è

possibile trovare resistori in cui il filo viene avvolto su un nucleo in ceramica e poi alloggiato in una

protezione di alluminio anodizzato.

Fig. 43 Resistori a filo.

Reti di resistenze

Sono costituite da un certo numero di elementi resistivi (fig. 44) inseriti in alloggiamenti di

ceramica a 14 o 16 piedini (DIL), o in rivestimenti ancor più sagomati ad 8 o 9 terminali (SIL).

Possono presentarsi in soluzioni singole o ad allacciamento in comune.

Potenziometri

Sotto questo nome troviamo una vasta gamma di resistori il cui valore può essere regolato attraverso il

Dipartimento di elettronica

30

I.T.S. “L.Einaudi” - Montebelluna

Reti elettriche

movimento di un cursore che può essere circolare o lineare (fig. 45).

Fig. 44 Reti di resistenze: (a) e (b) singole; (c) e (d) con allacciamento in comune.

Fig. 45 Potenziometri.

Sono forniti di tre terminali e possono essere utilizzati nel modo rappresentato in figura 46b, e cioè da

vere resistenze variabili (trimmer), oppure come in figura 47 dove, nell'uso classico da potenziometri

e opportunamente alimentati, producono una tensione dipendente dalla posizione del cursore.

Sfruttando questa seconda modalità i potenziometri costituiscono il tipo più noto e semplice di

trasduttori di posizione.

a)

b)

R

aR

VG

R

aR

VO = aVG

Fig. 46 Trimmer.

Dipartimento di elettronica

I.T.S. “L.Einaudi” - Montebelluna

Fig. 47 Potenziometro.

31

Reti elettriche

1.10 I segnali

Una qualsiasi grandezza fisica a cui viene associata una informazione attraverso la

variazione nel tempo di una sua caratteristica viene definita segnate.

Per la natura di questa materia noi prendiamo in esame solo i segnali di tipo elettrico.

Una prima distinzione può essere effettuata dividendo i segnali in analogici e digitali.

Un segnale analogico può assumere tutti i valori compresi entro un certo intervallo di esistenza,

mentre uno digitale è rappresentabile attraverso un numero finito di livelli.

I segnali digitali legati all'elettronica sono generalmente di tipo binario, assumono cioè due soli

possibili valori, uno ‘basso’, il cosiddetto zero logico, l'altro ‘alto’ e cioè l'uno logico.

Se un segnale s(t) è presente in ogni istante viene definito continuo (fig. 48), se invece è definito

solo in determinati significativi momenti è considerato discreto (fig. 49).

s

s

t

t

Fig. 48 Segnale continuo.

Fig. 49 Segnale discreto.

I segnali da noi considerati saranno per lo più continui (in tutto il tempo o per alcuni intervalli).

Questi possono essere distinti in periodici e aperiodici.

In figura 50 è disegnato un segnale periodico, definibile come quel fenomeno che si ripete con

uguali modalità ad intervalli regolari di tempo.

Ogni intervallo durante il quale si sviluppa un ciclo del segnale si chiama periodo (unità di misura

il secondo) e viene di solito indicato con il simbolo T.

Si definisce poi frequenza f l'inverso del periodo, cioè

1

f =

T

Essa rappresenta il numero di cicli che il segnale ripete in un secondo.

La frequenza si misura in hertz [Hz] i cui multipli più significativi sono

il chilohertz [kHz]

il megahertz [MHz]

il gigahertz [GHz]

fl

fl

fl

1 kHz = 103 Hz

1 MHz = 106 Hz

1 GHz = 109 Hz

Si dicono invece segnali aperiodici tutti quelli in cui non è possibile riconoscere dei cicli ripetitivi e

per i quali non sono significativi i concetti di periodo e frequenza (fig. 51).

Dipartimento di elettronica

I.T.S. “L.Einaudi” - Montebelluna

32

Reti elettriche

s

T

t

Fig. 50 Segnale periodico.

s

s

S+

S+

T

2T

t

S-

S-

t

Fig. 51 Segnale aperiodico.

Fig. 52 Segnale alternato.

I segnali periodici, a loro volta, possono differenziarsi in unipolari e bipolari: i primi presentano

sempre lo stesso verso rispetto a quello di riferimento, mentre i secondi lo invertono.

Tra i bipolari particolare importanza rivestono i segnali alternati (fig. 52). In essi sono uguali le

aree, positiva e negativa, racchiuse in un periodo tra la funzione e l'asse delle ascisse.

Parametri fondamentali per definire le caratteristiche di un segnale periodico, oltre la frequenza e il

periodo, sono:

valor medio

altezza di un ipotetico rettangolo la cui area è uguale alla somma algebrica delle

aree racchiuse in un periodo tra la funzione segnale e l'asse delle ascisse;

valore efficace

valore di un segnale continuo (tensione o corrente) che, applicato ad una

resistenza, produce in un ciclo gli stessi effetti termici della grandezza periodica;

ampiezza

valore massimo assunto dal segnale rispetto al suo valor medio;

valore picco-picco distanza tra i valori massimo e minimo del segnale.

Esempio 21

Calcolare i valori medio ed efficace del segnale (tensione) raffigurato in figura 53.

Dipartimento di elettronica

I.T.S. “L.Einaudi” - Montebelluna

33

Reti elettriche

L'area Al vale

5◊1=5V◊s

e quindi il valor medio è

Vm =

A1 5

= = 1,25V

4

T

Il segnale di figura 53, applicato ad un resistore supposto di valore 1 kW, dissipa una potenza istantanea pari a

52/1000 = 0,025 W = 25 mW solo per 1 secondo ogni periodo; quindi l'energia trasformata in calore è

W = Pt = 25 ◊ 1 = 25 mJ

Il valore efficace del segnale, inteso come quel valore costante che, applicato in un periodo (4 s), dissipa la stessa

energia, si ricava dall'espressione

V eff2

R

⋅ T = W = 25mJ

da cui

V eff2 =

25 ⋅10 −3 ⋅10 3

= 2,5V

4

v(V)

v(V)

5

+3,75

componente alternata

valor medio

+1,25

A1

0

1

4

5

t(s)

-1,25

0

1

4

Fig. 53 Segnale rettangolare.

5

t(s)

Fig. 54

Il segnale di figura 53, così come generalmente tutte le grandezze periodiche con valor medio non

nullo, può essere pensato come la somma tra un segnale continuo, coincidente con il valor medio del

segnale in questione, e uno alternato di forma identica a quello dato.

In figura 54 abbiamo rappresentato le due componenti, continua ed alternata, del segnale di figura

53: la prima ha valore 1,25 V, la seconda ha valore medio nullo, massimo 3,75 V e minimo -1,25 V.

Segnali periodici significativi

Onda quadra

Un'onda quadra è un segnale che in un periodo assume solo due livelli che si alternano con uguale

durata (fig. 55). I1 valore ‘basso’ è generalmente nullo, ma può essere considerata quadra anche

un'onda che presenta livelli di segno opposto e di pari valore assoluto.

Il cosiddetto ciclo utile del segnale (duty-cycle), definito come rapporto tra la durata del livello alto

Dipartimento di elettronica

34

I.T.S. “L.Einaudi” - Montebelluna

Reti elettriche

TH e il periodo T, ed indicato con la lettera d, è pari a 0,5. Cioè

δ=

TH

= 0,5

T

(1.19)

Il duty-cycle viene usualmente espresso in percentuale.

v

v

T

VM

ϕ

ω

t

TH

t

-VM

T

Fig. 55 Onda quadra.

Fig. 56 Tensione alternata sinusoidale.

Onda rettangolare

Il segnale di figura 53 è rettangolare e si differenzia da quello quadro per avere un duty-cycle

diverso dal 50%.

Nel caso di duty-cycle molto minore del 50% si usa indicare tale segnale con il termine impulsivo.

Onda sinusoidale

Un segnale alternato sinusoidale assume la forma mostrata in figura 56 ed è rappresentato trigonometricamente dalla seguente legge

v(t ) = VM sen(ωt + ϕ )

(1.20)

dove

v(t) = valore istantaneo del segnale

VM = valore massimo o ampiezza

w = 2pf = pulsazione angolare

j = fase iniziale

Si può dimostrare che il valore efficace di un segnale sinusoidale è legato al suo valore massimo

dalla relazione

V

(1.21)

Veff = M

2

Dipartimento di elettronica

I.T.S. “L.Einaudi” - Montebelluna

35

Reti elettriche

Segnali aperiodici significativi

Gradino

Un esempio di tensione a gradino è mostrata in figura 57. È definita dall'espressione

v(t ) = E ⋅ u (t − t 0 )

dove

⎧⎪0

u (t − t 0 ) = ⎨

⎪⎩1

(1.22)

per t < t 0

per t > t 0

rappresenta la funzione gradino unitario.

Il gradino è uno dei segnali più importanti nello studio dei sistemi di controllo, la cui risposta a

questo tipo di eccitazioni offre molte informazioni sulla velocità e sulla stabilità dei sistemi in esame.

v

v

E

t0

t

t0

T

t

E0

Fig. 57 Gradino.

Fig. 58 Rampa.

Rampa

È un segnale che cresce o decresce linearmente nel tempo. Un esempio di tale grandezza è mostrato

in figura 58 ed ha la seguente espressione analitica

E

v(t ) =

t + E0

(1.23)

T − t0

Importante per la classificazione dei sistemi di controllo, la rampa é inoltre uno dei segnali che si

incontrano pia frequentemente nelle applicazioni e nella strumentazione.

Esponenziale

Una tensione con possibile andamento esponenziale è mostrata in figura 59 ed ha espressione

analitica

−t

⎛

v(t ) = V0 ⎜⎜1 − e τ

⎝

con

Dipartimento di elettronica

I.T.S. “L.Einaudi” - Montebelluna

36

⎞

⎟

⎟

⎠

(1.24)

Reti elettriche

V0 = valore asintotico a cui tende la funzione per t = costante di tempo del circuito.

Tale funzione sarà frequentemente utilizzata nella prossima Unità. Didattica, nello studio della

risposta al gradino in sistemi contenenti elementi reattivi.

v

t

V0

t

Fig. 59 Esponenziale.

Dipartimento di elettronica

I.T.S. “L.Einaudi” - Montebelluna

37

Reti elettriche - Appendici

APPENDICE 1

A.1

I quadripoli e i generatori dipendenti

Un quadripolo (fig. A.1) è un circuito che presenta una coppia di terminali in ingresso ed una in

uscita e realizza una trasformazione di vario tipo del segnale che lo attraversa (amplificazione di

tensione, di corrente, di potenza, adattamento di resistenze o di impedenze, filtraggio, ecc.).

Ad esso sono associate tensioni, correnti e resistenze sia di ingresso che di uscita.

La resistenza di ingresso di un quadripolo è la resistenza equivalente vista dai terminali di ingresso,

con i terminali di uscita chiusi sull'eventuale carico e vale

Ri =

vi

ii

(1)

La resistenza di uscita di un quadripolo è la resistenza equivalente vista dal carico dopo aver

annullato l'effetto dei generatori indipendenti; si ottiene dalla relazione

Ro =

vo

io

(2)

Altri parametri fondamentali di un quadripolo sono:

guadagno di tensione = rapporto tra tensione di uscita e tensione di ingresso

Av =

vo

vi

(3)

guadagno di corrente = rapporto tra corrente di uscita e corrente di ingresso

Ai =

io

ii

(4)

guadagno di potenza = rapporto tra la potenza fornita dalla coppia di terminali di uscita e quella

associata ai morsetti di ingresso

Ap =

po

pi

Ri

Ro

ii

vi

(5)

io

rete

elettrica

vo

Fig.A.1 Quadripolo

Naturalmente, nel caso in cui i valori che esprimono i vari guadagni dovessero risultare inferiori

38

Reti elettriche - Appendici

all'unità, sarà più opportuno parlare di attenuazione.

Viene definito generatore dipendente un generatore che fornisce una tensione o una

corrente imposta dalla tensione o dalla corrente presente in un altro punto del

circuito.

Svolgiamo il seguente esempio.

Esempio 1

o

Ro

Ri

ii

vi

R1

io

h1vo

h2ii

R2

vo

RL

Fig. A.2

Il quadripolo di figura A.2 richiama il circuito equivalente per lo studio del funzionamento di un transistor (BJT)

in presenza di tensioni di ingresso variabili nel tempo. Questo argomento esula dagli obiettivi del volume, lo

proponiamo sia per evidenziare la presenza di un generatore di tensione e di uno di corrente, entrambi dipendenti,

sia per esercitarci al calcolo delle resistenze di ingresso e di uscita.

Nello schema da analizzare il primo generatore fornisce una tensione legata a quella di uscita attraverso il

parametro h1, il secondo genera una corrente legata a quella di ingresso attraverso il parametro h2.

In questo esempio la coppia dei terminali di uscita è collegata al carico resistivo RL.

• Resistenza di ingresso

Ri =

vi

ii

dove

v i = R1ii + h1 v o

ma

v o = −h2 i i (R 2 // R L )

(la corrente h2ii circola sul parallelo tra R2 e RL)

per cui

v i = R1ii − h1 h2 ii (R 2 // R L )

Dividendo membro a membro l'ultima espressione per ii ricaviamo

Ri = R1 − h1 h2 (R 2 // R L )

• Resistenza di uscita

Per calcolare la resistenza di uscita si tolga il carico, si consideri la corrente io erogata da un fittizio generatore di

tensione vo e si annulli la sorgente della tensione vi (fig. A.3).

Questo metodo è utilizzabile anche per determinare la resistenza equivalente nei circuiti in cui si riduce la rete con

39

Reti elettriche - Appendici

il metodo di Thevenin, nel caso in cui siano presenti generatori dipendenti.

Ro

ii

R1

io

h1vo

h2ii

R2

vo

Fig. A.3

Scriviamo dunque

Ro =

vo

io

dove

io =

vo

+ h2 i i

R2

e

ii = −

hi v o

R1

da cui

⎛ 1 h1 h2

+

i o = v o ⎜⎜

R1

⎝ R2

Sostituendo quest'ultima espressione nella relazione R o =

Ro =

⎞

⎟⎟

⎠

vo

otteniamo

io

R1 R 2

1

=

1 h1 h2

R1 − h1 h2 R 2

−

R2

R1

Si noti infine come il circuito di figura A.2 presenti un terminale, comune sia al bipolo di uscita che a quello di

ingresso, che potrebbe essere ridotto ad un unico morsetto. Questo particolare e molto diffuso quadripolo, come é

appunto il BJT di cui abbiamo anticipato il modello equivalente, é praticamente riconducibile ad un elemento con

tre terminali, definito tripolo.

40

Reti elettriche - Appendici

APPENDICE 2

A.2 Altri metodi per la soluzione delle reti elettriche

Metodo di Norton

Può essere considerato il duale del metodo di Thevenin.

Con il metodo di Norton è possibile ridurre una rete lineare che fa capo ad una

coppia di terminali ad un generatore reale di corrente e cioè alla combinazione di un

generatore ideale Ieq e di una resistenza equivalente Req connessa in parallelo

(fig.A.4).

A

A

rete

elettrica

lineare

Ieq

B

Req

B

Fig. A.4

• La Ieq si determina calcolando la corrente che circola tra i due terminali della rete da semplificare

dopo averli cortocircuitati.

• La resistenza equivalente, allo stesso modo di quanto visto col metodo di Thevenin, è invece la

resistenza vista dai due terminali guardando la rete e si calcola dopo aver annullato i generatori

indipendenti (generatori di tensione cortocircuitati, generatori di corrente aperti).

Esempio 2

Trasformare un modello equivalente realizzato secondo il teorema di Thevenin in uno secondo Norton.

Si tratta in pratica di rendere il modello di un generatore reale di corrente equivalente a quello di un generatore

reale di tensione dato (fig. A.5).

• Determiniamo Ieq (fig. A.6a]

(cortocircuitiamo il bipolo A-B)

I eq =

V eq'

'

R eq

• • Determiniamo Req (fig. A.6b)

(cortocircuitiamo il generatore e scolleghiamo iI carico)

'

R eq = Req

41

Reti elettriche - Appendici

'

Req

A

A

Veq'

Ieq

RL

Req

RL

B

B

Fig.A.5

a)

'

Req

A

b)

'

Req

Ieq

A

Veq'

Req

B

Fig.A.6

B

a)

b)

Esempio 3

Calcolare la tensione VAB presente ai capi del resistore da 12kW (fig. A.7), riducendo il circuito a sinistra del

bipolo A-B applicando il metodo di Norton.

Per calcolare la Ieq si cortocircuiti il bipolo A-B e si determini la corrente che vi circola. Si possono separare gli

effetti dei due generatori, come mostrano gli schemi di figura A.8.

A

2mA

2kW

VAB

4mA

6kW

B

Fig.A.7

I.

Effetto dei generatore da 2 mA

(fig. A.8a)

'

La corrente I eq è quella che scorre sul resistore da 6 kW.

42

12kW

Reti elettriche - Appendici

I eq' = 2 ⋅

II.

Effetto del generatore da 4 mA

2

= 0,5mA

2+6

(fig. A.8b)

La corrente I eq'' è quella che scorre sul resistore da 2 kW.

''

I eq

= 4⋅

6

= 3mA

2+6

Pertanto I eq = 0,5 + 3 = 3,5mA .

A

A

'

I eq

2mA

''

I eq

2kW

2kW

4mA

6kW

6kW

B

Fig.A.8

B

a)

b)

Per determinare la Req si aprano i rami dove sono presenti i due generatori di corrente e si calcoli la resistenza

equivalente vista dal resistore da 12 kW guardando la rete:

Req = 2 + 6 = 8kΩ

(i due resistori sono in serie)

Il circuito di figura A.7 diventa quindi equivalente a quello di figura A.9.

La tensione ai capi dei 12 kW risulta infine

V AB = 3,5 ⋅10 −3 ⋅ (8 // 12 ) ⋅10 3 = 16,8V

A

3,5mA

8kW

VAB

B

Fig. A.9

43

12kW

Reti elettriche - Appendici

Metodo di Millman