ANNO SCOLASTICO 2002/2003

CLASSE 5^BZ

FIENI DANILO

ADERENTI FRANCESCO

TESI DI MATURITA’ DI SISTEMI

PROGRAMMATORE DI EPROM

DOCENTE:

Ing. AZZANI CLETO

SOMMARIO

INTRODUZIONE ......................................................................................................................... 3

CHE COSA E’ UNA EPROM................................................................................................... 3

READ-ONLY MEMORY .......................................................................................................... 4

SCHEMA ELETTRICO .............................................................................................................. 5

MANUALE PROGRAMMATORE........................................................................................ 9

82C55A.............................................................................................................................................. 15

Buffer per il Bus Dati........................................................................................................................ 15

Circuiti logici di controllo e di lettura/scrittura.................................................................................... 15

Operazioni fondamentali dell’82C55A:.............................................................................................. 16

Controllo degli interrupt:................................................................................................................... 16

Modi operativi:................................................................................................................................. 17

FUNZIONAMENTO DEL CIRCUITO ............................................................................... 18

2

INTRODUZIONE

Questa tesi ha lo scopo di interfacciare un programmatore di eprom ad un PC.

Il programmatore di eprom ci è stato fornito dalla scuola che ne era già in possesso ma inutilizzato.

Nella specie è il modello “PGM512” costruito dalla “MICROLAB”.

Nello specifico questo programmatore è in grado di utilizzare eprom che ai giorni nostri non sono più

utilizzate ma bisogna considerare che è un progetto del 1987.

CHE COSA E’ UNA EPROM

La sigla eprom deriva dall’inglese “Erasable Programmable Read Only Memory” (memoria di sola lettura

programmabile cancellabile).

Le eprom sono memorie programmabili dall’utente per un numero limitato di volte , e rispetto alle prom

(rom programmabili) presentano il vantaggio di non dover essere sostituite quando occorre modificare

qualche dato memorizzato.

Non è possibile, in una eprom, effettuare una cancellazione parziale o una modifica ai dati contenuti. Per

scrivere anche un solo bit è necessario cancellare totalmente le informazioni contenute.

Questa operazione si effettua esponendo l’integrato per alcuni minuti ad una radiazione ultravioletta; esiste

inoltre una categoria alla quale è stata aggiunta l’opzione di cancellazione tramite impulso elettrico: le

eeprom (Elettrical Erasable Programmable Read Only Memory).

Il meccanismo di cancellazione di una eprom è molto semplice: la radiazione ultravioletta trasporta

abbastanza energia per penetrare all’interno dello strato isolante dell’integrato, raggiungere gli elettroni

immagazzinati nel floating gate e trasferire loro energia per uscire da questa zona.

Il contenitore DIP presenta una finestrella che consente di esporre l’integrato alla radiazione.

Questa finestrella normalmente è coperta da materiale opaco per evitare che le radiazioni ultraviolette

presenti nella luce naturale cancelli le informazioni contenute nella stessa.

Per cancellare il contenuto di una eprom si usano appositi dispositivi (cancellatori di eprom).

Le eprom pulite hanno tutte le celle a 1 cioè $FF.

Infatti i raggi ultravioletti inseriscono tutti 1 mentre i segnali elettrici portano a 0 il contenuto delle celle.

Le eprom commerciali sono identificate da una sigla che inizia per 27 (talvolta per 25) e termina con un

numero che rappresenta la capacità in Kbyte della memoria.

Fanno eccezione i dispositivi prodotti dalla Texas Instrument e dalla Motorola, le cui sigle iniziano con il

numero 68.

Ricordiamo infine che, pur essendo realizzate in tecnologia unipolare, le eprom risultano perfettamente

compatibili con gli integrati TTL.

3

READ-ONLY MEMORY

A read-only memory (ROM) is a memory device in which a fixed set of binary information is stored. The

binary information must first be specified by the user and is then embedded in the unit to for in the required

interconnection pattern.

Since read-only memories have special internal links, that can be fused or broken, the desired

interconnection for a particular application requires the fusion of certain links to form the required circuit

paths.

Once a pattern is established for a read-only memory it remains fixed even when power is turned off and

then on again.

A read-only memory consists of n input lines and m output lines. Each bit combination of the input variables

is called an address. Each combination that comes out of the output lines is ca1led a word. The number of

bits per word is equal to the number ofoutput lines m.

An address is essentially a binary number that denotes one of the minterms of n variables.

The number of distinct addresses possible with n input varia blesis 2n . An output word can be selected by a

unique address, and since there are 2n distinct addresses in a read-only memory,

there are 2n distinct words which are stored in the unit.

For example a 32 x 8 ROM consists of 32 words of 8 bits each.

This means that there are eight output lines and that there are 32 distinct words stored in the unit, each of

which may be applied to the output lines.

The required paths in a read-only memory may be programmed in two different ways.

The first is called mask programming and is done by the manufacturer during the last fabrication process.

In this case the manufacturer makes the corresponding mask for the paths to produce the l's and 0's

according: to the customer’s truth table.

For this reason, mask programming is economical only if large quantities of the same read-only memory

configuration are to be manufactured.

For small quantities, it is more economical to use a programmable read-only memory or PROM that contains

all 0’s (or all l’s) in every bit of the stored words.

A third type of unit available is called erasable PROM or EPROM.

EPROMs can be reconstructed to the initial value even though they have been changed previously.

Erasure occurs when an EPROM is placed under a special Ultraviolet light or by electrical signals.

The function of a read-only memory can be interpreted in two different ways.

The first interpretation is of a unit that implements any combinational circuit. The second interpretation

considers the read-only memory to be a storage unit having a fixed pattern of bit strings called words.

From this point of view, the inputs specify an address to a specifìc stored word which is then applied to the

outputs.

This is the reason why the unit is given the name read only memory. Memory is commonly used to designate

a storage unit. Read is commonly used to signify that the content of a word specifìed by an address in a

storage unit is placed at the output terminals.

Thus, a read-only memory is a memory unit with a fixed word pattern that can be read out upon application

of a given address.

The bit pattern in the read-only memory is permanent and cannot be changed during normal operation.

Read-only memories are widely used to implement complex combinational circuits directly from their truth

tables.

They are useful for converting from one binary code to another (such as ASCII to EBCDIC) and vice versa,

for arithmetic functions such as multipliers, for display of characters in a cathode-ray tube and in many other

applications requiring a large number of inputs and outputs.

They are also employed in the design of micro programmed control units of digital systems.

4

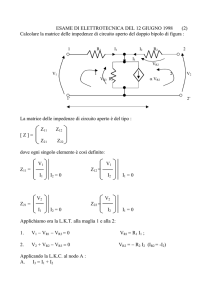

SCHEMA ELETTRICO

5

6

7

8

MANUALE PROGRAMMATORE

M I C R O L A B sas

Hardware Software Microprocessori

25070 CAINO (Brescia) -Via Nazionale 124- Tel. 030/630018

25100 BRESCIA -Via P. da Cemmo 3/A- Tel. 030/41847

PROGRAMMATORE DI EPROM EPG512

Il programmatore di EPROM mod.

operare sui seguenti dispositivi :

EPG512

consente

di

-EPROM : TMS2516 TMS2532 TMS2564 2716 2732 @ 25V.

-EPROM : 2732A 2764 27128 27256 @ 21V.

-EPROM : 2764 27128 27256 27512 @ 12.5V.

-EEPROM : HM-58064 (scrittura e lettura).

-RAM : 48Z02 (scrittura e lettura).

-PROM : MCM7681 (solo lettura).

La scelta del tipo di dispositivo viene effettuata attraverso

il software di gestione che si presenta nel modo seguente :

M6809-XDOS-EPROM-PROGRAMMER

4.xx-EPG512 by MICROLAB 1987

Port $yyyy - FCPU = zzz MHz

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

-

INT2716

TMS2532

INT2732

INT2764

INT2764

INT27128

INT27128

INT27256

INT27256

TMS2564

INT27512

INT27512

MK48Z02

MCM7681

HM58064

02048

04096

04096

08192

08192

16384

16384

32764

32764

08192

65536

65536

02048

01024

08192

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

EPROM

EPROM

EPROM

EPROM

EPROM

EPROM

EPROM

EPROM

EPROM

EPROM

EPROM

EPROM

RAM

PROM

EEPROM

Algoritmo Intel

Algoritmo Intel

Algoritmo Intel

Algoritmo Intel

.xx sta ad indicare la revisione del software;

$yyyy sta ad indicare l'indirizzo del Port di I/O attivo, zzz

sta ad indicare la frequenza di CPU misurata all'atto

dell'accensione.

Il

programmatore

di EPROM mod. EPG512 viene connesso

direttamente all'Host Computer

attraverso

l'interfaccia

predisposta per la Line-printer (Standard Centronics); il

Port-A, solitamente bufferato e percio' unidirezionale, viene

usato come port per i segnali di controllo mentre il Port-B,

solitamente non bufferato, viene usato come port per il

trasferimento

dei dati da e verso il dispositivo montato

nell'apposito zoccolo.

Il programmatore di EPROM mod. EPG512 e'

software per i seguenti sistemi di sviluppo :

corredato

di

-EXORciser M6809 sotto MDOS09 3.06

-EXORset 30-33-100 sotto XDOS 4.12 - 4.13

-M6809DS operante sotto XDOS 4.14

9

Il software fornito

seguenti operazioni :

R

L

S

P

E

V

D

M

X

H

Q

K

di

serie

consente

di

effettuare le

EPROM read

LOAD disk-file

SAVE disk-file

EPROM programming

EPROM-RAM verify

EPROM test

MEMORY dump

DATA move

MONITOR entry

EPROM select

DOS return

SELF-TEST

Le temporizzazioni sono sempre effettuate via

Software

partendo dal clock della CPU che si suppone di 1 MHz in caso

di EXORset ma che puo' essere 1.0 - 1.5 - 2.0 MHz in caso di

EXORciser ; il programma segnala con apposito messaggio la

frequenza di lavoro e verifica che sia fra quelle consentite.

La procedura di Test

del

programmatore

consente

di

controllare

l'

efficienza

dell' hardware in caso si

verifichino malfunzionamenti. Per attivare tale procedura e'

necessario portare a

1 il flag TSTFLG contenuto nel PSN

$0000 (offset 4) attraverso la seguente procedura di DUMP.

=DUMP EP512.CM

: R 0

: S

: 4/1/

: S

: W 0

: Q

=

Caricando il programma EPG512 in memoria il menu delle

procedure verra' aggiornato con l' inclusione della procedura

di test.

All'interno della procedura

di

test

potranno

essere

effettuate le scelte seguenti :

Non inserire EPROM !

1

Test Read-Status

2

3

4

5

6

7

8

9

A

Q

Test PGM-Status

Test PGM-Pulse

Set Vpp = 0

Set Vpp = 5

Set Vpp = 12.5

Set Vpp = 21

Set Vpp = 25

Scala tensioni

Generazione indirizzi

End SELF-TEST

Exit via BREAK

10

LA PROCEDURA DI TEST VA

INSERITO NELLO ZOCCOLO .

ESEGUITA SENZA ALCUN DISPOSITIVO

Scegliendo lo status Read o PGM si puo' verificare la

correttezza dei livelli logici presenti ed il valore della

tensione di programmazione Vpp (a tale scopo sono stati

riportati nelle pagine seguenti le condizioni Read e PGM

delle EPROM piu' diffuse).

Scegliendo Test PGM Pulse e' possibile verificare con un

oscilloscopio

la

forma

d'onda

dell'

impulso

di

programmazione.

Le caratteristiche di tale impulso sono le seguenti :

Ampiezza : livelli compatibili TTL (LLB max. 0.4 V. - LLA

min. 2.4 V.)

Durata

:

(dipende

dal

tipo di algoritmo impiegato)

normalmente 2 ms.

L'indirizzo base del port-parallelo PIA MC6821 e' :

- $EC10 per le versioni MDOS M6800 e M6809

- $EF60 per la versione XDOS M6809 per EXORset

- $EFC0 per la versione XDOS M6809 per M6809DS

il software fornito riconosce l'indirizzo del port-parallelo

della stampante fra una serie di 5 indirizzi collocati nel

PSN $0000 del programma di gestione (partendo da offset $16).

Non e' quindi piu' necessario inizializzare la zona PORT

(offset 2-3) del PSN $0000 del software di gestione.

TABELLA

PRINTER PORT

PSN $0000

Offset

$16

$18

$1A

Contenuto

EF CO

EF 60

EC 10

$1C

$1E

00 00

00 00

Printer Port M6809SBC

Printer Port EXORset

Printer Port EXORciser

Printer Port libero

Printer Port libero

La tabella PRINTER PORT viene scandita dall'alto verso il

basso pertanto la prima posizione e' quella a piu' elevata

priorita'.

Per assegnare un port specifico al programmatore di EPROM

(distinto da quello della Line-Printer)

e'

necessario

modificare il contenuto della tabella PRINTER PORT attraverso

l'uso dei comandi DUMP o PATCH.

Ad esempio si voglia assegnare al Programmatore di EPROM un

port con indirizzo-base $ED00; si dovra' procedere come segue

:

=DUMP EPG512.CM

: R 0

: S

: 16/ED,00/

: S

: W 0

: Q

=

11

PSN $0000

Parametri Software

- TSTFLG

1 byte

- PRINTER-PORT TABLE 11 bytes

- FDC-CODE TABLE

16 bytes

Off. $04

Off. $16

Off. $06

(0=NO - 1=SI)

MESSAGGI DI ERRORE :

** E401 ** Illegal EPROM code

** E402 ** FDC firmware error

** E403 ** FCPU Error

** E404 ** Port Error

*****************************************************

*

PINOUT

VARIE

EPROM

*

*****************************************************

Pinout Comune 24 pin

------------------| Pin

Sig. |

------------------01

A7

02

A6

03

A5

04

A4

05

A3

06

A2

07

A1

08

A0

09

D0

10

D1

11

D2

12

GND

------------------| Pin

Sig. |

------------------24

Vcc

23

A8

22

A9

21

***

20

***

19

***

18

***

17

D7

16

D6

15

D5

14

D4

13

D3

----------------------------------------------------|

Pin

2708

2716

2732

2532

|

----------------------------------------------------18

Vpp

-CE/PG

-CE/-PG

A11

19

Vdd

A10

A10

A10

20

-CS/WE

-OE

-OE/Vpp

-CE/-PG

21

Vbb

Vpp

A11

Vpp

2708

PGM

RD

24 pin - 1K x 8 EPROM +5 +12 -5 Vdd=+12V, Vbb=-5V

Vpp 26 V pulsed NxTpw=100ms, WE to Vdd.

-CS, Vpp LOW.

2716

PGM

RD

24 pin - 2K x 8 EPROM +5V Vpg: 25V

PG TTL pulse act. HIGH, -OE HIGH, Vpp=Vpg

-CE, -OE LOW; Vpp=HIGH

2732

PGM

RD

24 pin - 4K x 8 EPROM +5V Vpg: 21V, 25V

-PG TTL pulse act. LOW, Vpp=Vpg

-CE, -OE/Vpp LOW

2532

PGM

RD

24 pin - 4K x 8 EPROM +5V Vpg: 25V

-PG TTL pulse act. LOW, Vpp=Vpg

-CE LOW, Vpp HIGH.

12

Pinout Comune 28 pin

------------------| Pin

Sig. |

------------------01

***

02

***

03

A7

04

A6

05

A5

06

A4

07

A3

08

A2

09

A1

10

A0

11

D0

12

D1

13

D2

14

GND

------------------| Pin

Sig. |

------------------28

Vcc

27

***

26

***

25

A8

24

A9

23

***

22

***

21

A10

20

***

19

D7

18

D6

17

D5

16

D4

15

D3

----------------------------------------------------| Pin

2564

2764

27128

27256

27512 |

----------------------------------------------------01

Vpp

Vpp

Vpp

Vpp

A15

02

-CS1

A12

A12

A12

A12

20

A11

-CE

-CE

-CE

-CE

22

-PGM/PD

-OE

-OE

-OE

-OE/Vpp

23

A12

A11

A11

A11

A11

26

Vcc

N.C.

A13

A13

A13

27

-CS2

-PGM

-PGM

A14

A14

2564

PGM

RD

28 pin - 8K x 8 EPROM +5V Vpg: 25V

-PGM TTL pulse act. LOW, -CS1, -CS2 LOW, Vpp=Vpg

-CS1, -CS2, -PGM Low, Vpp HIGH.

2764

PGM

RD

28 pin - 8K x 8 EPROM +5V Vpg: 12.5V, 21V

-PGM TTL pulse act. LOW, -CE LOW, -OE HIGH, Vpp=Vpg

-CE, -OE LOW, -PGM, Vpp HIGH.

27128

PGM

RD

28 pin - 16K x 8 EPROM +5V Vpg: 12.5V, 21V

-PGM TTL pulse act. LOW, -CE LOW, -OE HIGH, Vpp=Vpg

-CE, -OE LOW, -PGM, Vpp HIGH.

27256

PGM

PGV

RD

28 pin - 32K x 8 EPROM +5V Vpg: 12.5V, 21V

-CE TTL pulse act. LOW, -OE HIGH, Vcc=6V

-CE HIGH, -OE LOW, Vpp=Vpg, Vcc=6V

-CE, -OE LOW, Vpp HIGH, Vcc=5V

27512

PGM

PGV

RD

28 pin -CE TTL

-CE LOW,

-CE, -OE

64K x 8 EPROM +5V Vpg: 12.5V

pulse act. LOW, -OE/Vpp=Vpg, Vcc=6V

-OE/Vpp LOW, Vcc=6V

LOW, Vcc=5V

13

--------------------------------------------------CONNESSIONI CONN. CANNON 25-POLI HDW EPG512

--------------------------------------------------CONN.25 POLI

HDW-EPG512-26 poli

1 -----------------------------2 <----------------------------- 1

3 -----------------------------> 12

4 -----------------------------> 9

5 -----------------------------> 10

6 -----------------------------> 7

7 -----------------------------> 8

8 -----------------------------> 5

9 -----------------------------> 6

10 -----------------------------> 3

11 -----------------------------> 4

12 -----------------------------13 -----------------------------> 25

14 <----------------------------> 23

15 <----------------------------> 22

16 <----------------------------> 21

17 <----------------------------> 20

18 <----------------------------> 19

19 <----------------------------> 18

20 <----------------------------> 17

21 <----------------------------> 16

22

23 ------------------------------ 11

24 ------------------------------ 24

25 -----------------------------N.C.

2-13-14-15-26

--------------------------------------------------CONNESSIONI TRA HOST-COMPUTER E CONNETTORE

CANNON 25-POLI FEMMINA PER PROGRAMMATORE

--------------------------------------------------CONN.25 POLI

SEGNALI-HOST

1 ------------------------------ GND

2 -----------------------------> CA1

3 <----------------------------- CA2

4 <----------------------------- PA0

5 <----------------------------- PA1

6 <----------------------------- PA2

7 <----------------------------- PA3

8 <----------------------------- PA4

9 <----------------------------- PA5

10 <----------------------------- PA6

11 <----------------------------- PA7

12 -----------------------------> CB1

13 <----------------------------- CB2

14 <----------------------------> PB0

15 <----------------------------> PB1

16 <----------------------------> PB2

17 <----------------------------> PB3

18 <----------------------------> PB4

19 <----------------------------> PB5

20 <----------------------------> PB6

21 <----------------------------> PB7

22 -----------------------------23 ------------------------------ GND

24 ------------------------------ GND

25 ------------------------------ GND

14

82C55A

Il circuito integrato INTEL 82C55A è un’interfaccia per I/O programmabile (PPI= Programmable Peripheral

Interface) atta a collegare una generica periferica al Bus della CPU. La configurazione operativa del 82C55A

è controllabile da software,in modo da rendere inutile l’uso di circuiti logici esterni per il normale

interfacciamento.

È dotato di 24 linee divise in 3 PORT:

- 8 linee appartenenti al PortA;

- 8 linee appartenenti al PortB;

- 8 linee appartenenti al PortC.

Le 8 linee del portA e del PortB possono essere programmate per funzionare o da ingressi o da uscite; mentre

le linee del PortC possono essere suddivise in 2 gruppi da 4 bit ciascuno.

Buffer per il Bus Dati

Viene utilizzato un buffer three-state bidirezionale a 8 bit per interfacciare l’82C55A al Bus Dati del sistema.

I dati sono trasmessi o ricevuti dal buffer sotto il controllo delle istruzioni di ingresso o di uscita inviate dalla

Cpu. Anche le parole di controllo e le informazioni di stato vengono trasferite attraverso questo buffer.

Circuiti logici di controllo e di lettura/scrittura.

La funzione di questo è di gestire tutti i trasferimenti interni ed esterni sia dei dati che delle parole di

controllo di stato. Riceve comandi del Bus Indirizzi e da quello di controllo della Cpu e controlla entrambe i

gruppi di linee.

___

(CS)

Chip Select. La presenza di un livello basso a questo piedino d'ingresso abilita le comunicazioni tra

l’interfaccia e la Cpu.

___

(RD)

Read. La presenza di un livello basso a questo piedino d'ingresso abilita l’82C55A ad inviare dati o

informazioni di stato alla Cpu tramite il Bus Dati. In altre parole la Cpu è abilitata a leggere l’82C55A.

___

(WR)

Write. La presenza di un livello basso a questo piedino di ingresso abilita la Cpu a scrivere dati o parole di

controllo nell’83C55A.

(A0 e A1 )

__ ___

Port Select 0 e Port Select 1. Questi segnali da ingresso, assieme alle precedenti linee RD e WR, permettono

di selezionare una delle tre Port d'accesso ai rispettivi registri di controllo. Normalmente queste due linee

sono connesse ai due bit meno significativi del Bus degli indirizzi (appunto A0 e A1 ).

(RESET)

Reset. La presenza di un livello alto a questo piedino azzera il registro di controllo e tutti i port (A, B e C)

vengono settati come ingresso.

15

Operazioni fondamentali dell’82C55A:

Possono essere selezionati da software tre diversi modi operatevi:

Modo 0 – ingresso/uscita normale

Modo 1 – ingresso/uscita controllato da strobe

Modo 2 - bus bidirezionale

Quando il segnale d’ingresso di reset assume un valore alto tutti i Port vengono selezionati come ingressi

(cioè tutte le 24 linee si portano in uno stato di alta impedenza). Quando il comando di reset termina

l’82C55A resta in tale condizione senza che siano richiesti altri comandi. Durante l’esecuzione del

programma possono essere utilizzati tutti i modi operativi disponibili mediante l’invio dalla Cpu di una sola

istruzione contenente la parola di controllo appropriata. Ciò permette di utilizzare un solo 82C55A per

gestire contemporaneamente diversi tipi di periferiche.

I modi operativi due Port A e B possono essere definiti in maniera indipendente l’uno dall’altro, mentre il

Port C viene diviso in due parti in funzione di quanto specificato per gli altri due Port.

Tutti i registri d’uscita, inclusi i flip-flop di stato, vengo resettati ogni volta che viene cambiato modo

operativo.

Le definizioni di modo dei due port possono essere combinare tra di loro in modo da adattare l’interfaccia

alle varie periferiche. Ad esempio il gruppo B può essere programmato in modo OUT per controllare la

chiusura di una serie di tasti o visualizzare sul display dei risultati, mentre il gruppo A può essere

programmato in modo IN per gestire una tastiera o un lettore di schede o qualsiasi altro dispositivo gestibile

mediante interrupt.

Le definizioni di modo e le loro combinazioni possibili possono all’inizio un inutile complicazione e risultare

difficili da comprendere, ma dopo il primo impatto se ne comprenderà la versatilità d’uso offerta da queste

scelte e risulteranno alla fine di facile apprendimento.

La progettazione dell’82C55A ha tenuto conto di vari fattori, quali l’efficienza della disposizione dei

componenti sulla scheda di trasporto e la facile connessione dei segnali di controllo tra CPU e interfaccia, ed

ha cercato di offrire la massima versatilità di funzioni svolte sfruttando tutti ipiedini disponibili

dell’integrato.

Controllo degli interrupt:

quando l’82C55A è programmato per funzionare in modo1 o modo 2, i segnali di controllo possono essere

utilizzati direttamente per generare richieste di interrupt alla CPU. Quando ciò avviene, i segnali di richiesta

di interrupt generati dal Port C possono essere abilitati o disabilitati ponendo a livello alto o basso il flip-flop

INTE associato, utilizzando l’istruzione set/reset di un singolo bit del Port C.

Con tali istruzioni il programmatore può permettere o negare ad un dispositivo di I/O la possibilità di

lanciare interrupt. Se viene posto ad 1 il contenuto di un dato bit del flip-flop INTE, l’interrupt del

dispositivo relativo viene abilitato, mentre se viene posto a 0 l’interrupt risulta disabilitato.

16

Modi operativi:

Modo 0 (ingresso uscita normale). Questa configurazione operativa permette di instaurare su tutti i 3 Port le

normali funzioni di lettura o scrittura di un dato. Non è richiesto alcun segnale di controllo tipo handshake in

quanto i dati vengono semplicemente letti o scritti nel Port relativo.

Caratteristiche del Modo 0:

- due Port a 8 bit e due Port a 4 bit;

- qualsiasi Port può essere definito come ingresso o come uscita;

- le uscite sono memorizzate;

- gli ingressi non sono memorizzati;

- sono possibili 16 diverse combinazioni di I/O.

Modo 1 (ingresso/uscita mediante strobe). Questo tipo di configurazione permette di trasferire i dati da un

Port mediante il controllo di segnali di handshake. Nel modo 1 il Port A e il Port B usano le linee del Port C

per generare o acquisire questi controlli.

Caratteristiche del Modo 1:

- due gruppi di trasferimento (gruppo A e gruppo B);

- ciascun gruppo contiene un Port di dati da 8 bit e un Port di controllo dei dati da 4 bit;

- i due port di dati ad 8 bit possono essere sia d’ingresso che d’uscita. Sia le uscite che gli ingressi sono

memorizzate;

- i due Port a 4 bit vengono usati per emettere i segnali di controllo e fornire lo stato del dispositivo alle

periferiche collegate ai due Port ad 8 bit.

Modo 2 (ingresso- uscita di dati attraverso bus bidirezionale e segnali di controllo).

Questa configurazione operativa permette all’82C55A di interfacciarsi direttamente ad un dispositivo avente

un bus bidirezionale ad 8 bit. I segnali di controllo (con modalità di handshake) permettono di regolare il

flusso dei dati in maniera analoga a quella vista per il Modo 1.

È possibile inoltre sia generare un segnale di interrupt che di abilitarne e disabilitarne il funzionamento.

Caratteristiche del Modo 2:

- si può usare solo il gruppo A;

- un bus bidirezionale ad 8 bit disponibile sul Port A e 5 linee di controllo accessibili sul Port C;

- sia gli ingressi che le uscite sono memorizzate;

-

il Port di controllo a 5 bit (Port C) viene usato per controllare e leggere lo stato del bus

bidirezionale ad 8 bit (Port A)

DATA-SHEET 82C55A

17

FUNZIONAMENTO DEL CIRCUITO

L’interfacciamento del PC al programmatore avviene tramite l’8255 che serve per compensare la differenza

di architettura dei due dispositivi.

Il programmatore ha un’architettura simile a quella Motorola, ha due Port: il PortA e il PortB.

Il primo è unidirezionale perché utilizzato esclusivamente per i segnali di controllo che dal Computer vanno

verso il programmatore.

Il secondo invece, è bidirezionale perché è usato per il trasferimento dei dati da e verso la EPROM montata

sullo zoccolo.

In più sull’8255 è presente un altro Port ; il PortC che viene utilizzato solo in parte per il controllo dei segnali

secondari, come: CB1, CB2, CA2 (guarda schema elettrico, blocco “Port”).

Dal PortA i segnali PA7 e PA6 partono verso due contatori CD4040 collegati tra di loro in cascata; PA7

fornisce l’impulso di clock al contatore Ic8, mentre PA6 fornisce l’impulso di reset ad ambo due i contatori.

I bit rimanenti del PortA (da PA0 a PA5) vanno verso gli integrati 74LS259 e 74LS174 (blocco “tensioni

variabili”).

Il 74LS259 è una memoria indirizzabile: le possibili combinazioni derivate dai bit PA0, PA1, PA2, PA3

fanno eccitare il corrispondente relè il quale cambia il funzionamento del piedino sullo zoccolo; perché i

piedini delle eprom non sono uguali per tutte.

Il 74LS174 invece, è un registro PIPO ( Parallel Input Parallel Output) che ha la funzione di controllare i

transistor open collector (SN7407) presenti sulle uscIte dell’integrato per l’utilizzo della esatta tensione di

programmazione che varia da EPROM a EPROM.

L’alimentazione di tutto il circuito è controllata dal blocco “Generatore” che è costituito da un trasformatore

a due linee, una 0-24V e l’altra 0-8V.

La prima linea (quella da 0-24V) si occupa della generazione di tutte le tensioni di programmazione

necessarie per i diversi tipi di EPROM; mentre la seconda linea (quella da 0-8V) viene utilizzata per

alimentare tutti gli integrati presenti nel circuito.

18

19