caricato da

paniced768

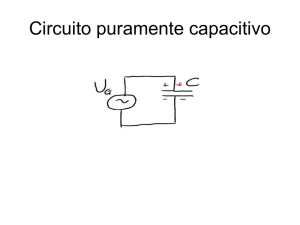

Elettrotecnica ed Elettronica: Corso per Istituti Tecnici