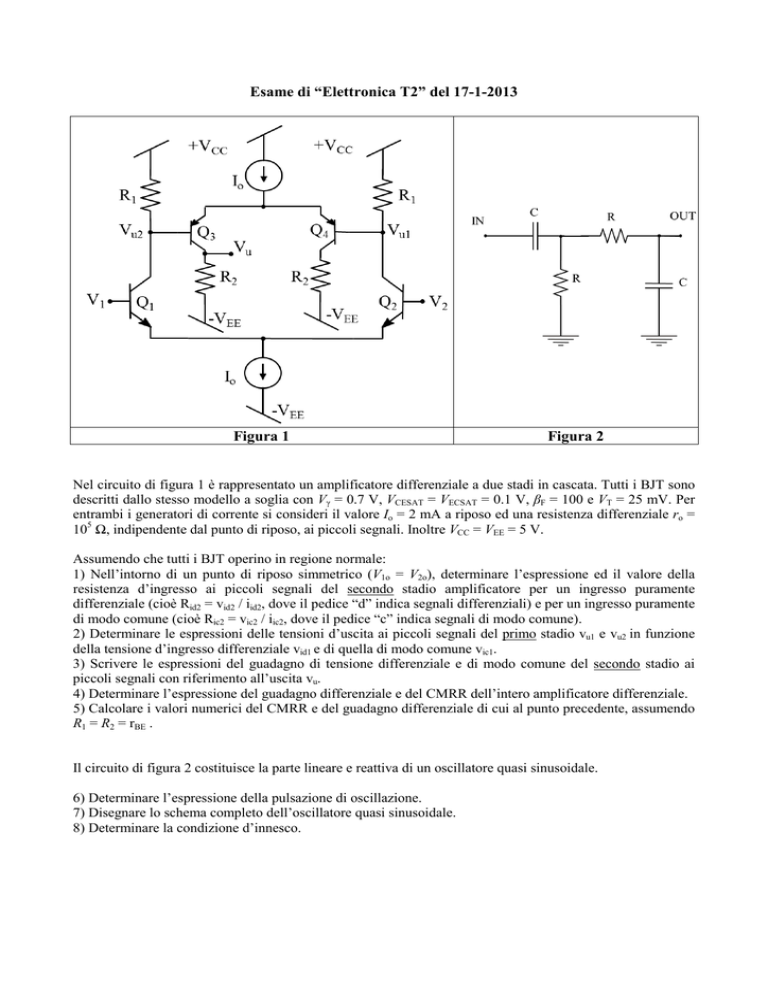

Esame di “Elettronica T2” del 17-1-2013

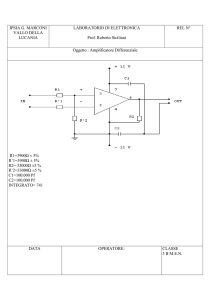

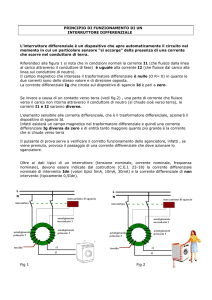

Figura 1

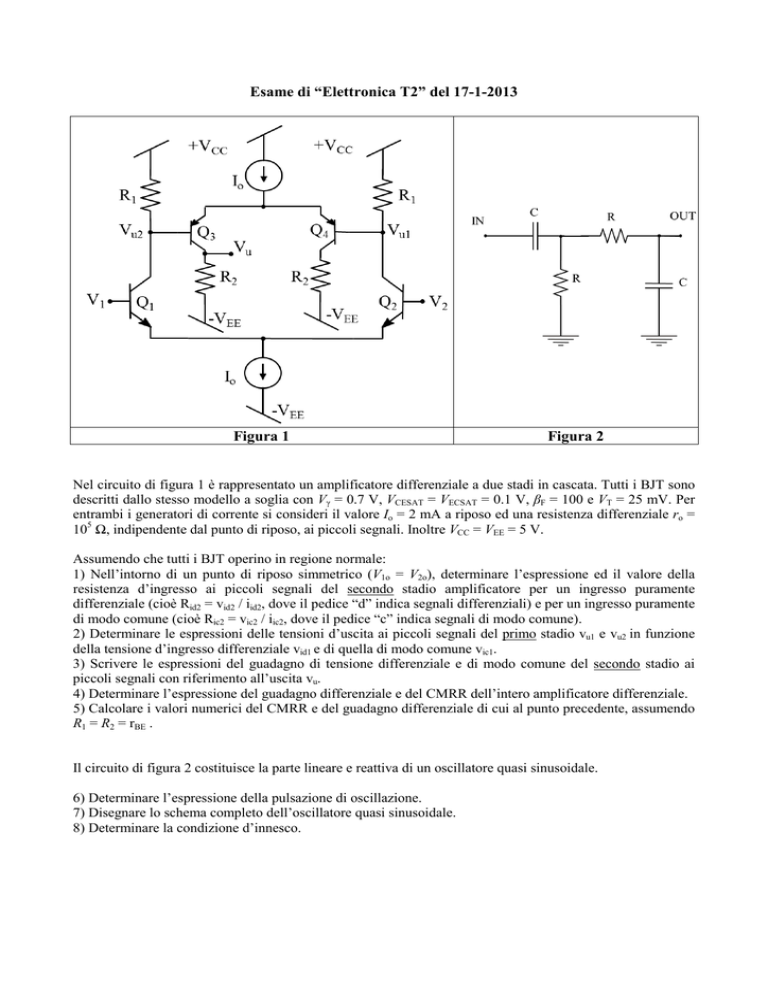

Figura 2

Nel circuito di figura 1 è rappresentato un amplificatore differenziale a due stadi in cascata. Tutti i BJT sono

descritti dallo stesso modello a soglia con Vγ = 0.7 V, VCESAT = VECSAT = 0.1 V, βF = 100 e VT = 25 mV. Per

entrambi i generatori di corrente si consideri il valore Io = 2 mA a riposo ed una resistenza differenziale ro =

105 Ω, indipendente dal punto di riposo, ai piccoli segnali. Inoltre VCC = VEE = 5 V.

Assumendo che tutti i BJT operino in regione normale:

1) Nell’intorno di un punto di riposo simmetrico (V1o = V2o), determinare l’espressione ed il valore della

resistenza d’ingresso ai piccoli segnali del secondo stadio amplificatore per un ingresso puramente

differenziale (cioè Rid2 = vid2 / iid2, dove il pedice “d” indica segnali differenziali) e per un ingresso puramente

di modo comune (cioè Ric2 = vic2 / iic2, dove il pedice “c” indica segnali di modo comune).

2) Determinare le espressioni delle tensioni d’uscita ai piccoli segnali del primo stadio vu1 e vu2 in funzione

della tensione d’ingresso differenziale vid1 e di quella di modo comune vic1.

3) Scrivere le espressioni del guadagno di tensione differenziale e di modo comune del secondo stadio ai

piccoli segnali con riferimento all’uscita vu.

4) Determinare l’espressione del guadagno differenziale e del CMRR dell’intero amplificatore differenziale.

5) Calcolare i valori numerici del CMRR e del guadagno differenziale di cui al punto precedente, assumendo

R1 = R2 = rBE .

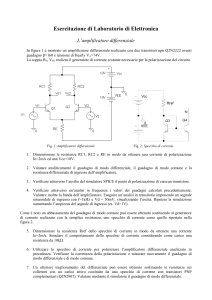

Il circuito di figura 2 costituisce la parte lineare e reattiva di un oscillatore quasi sinusoidale.

6) Determinare l’espressione della pulsazione di oscillazione.

7) Disegnare lo schema completo dell’oscillatore quasi sinusoidale.

8) Determinare la condizione d’innesco.