Elettronica 2

© Alessandro Bogliolo

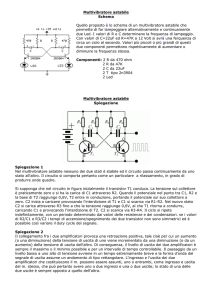

Esercitazione 5: Astabile (oscillatore a rilassamento)

1. Schema di base

Es5a: astabile

Mp1 1 2 3 1 mosp W=1u L=0.5u

Mn1 3 2 0 0 mosn W=0.5u L=0.5u

Mp2 1 3 4 1 mosp W=1u L=0.5u

Mn2 4 3 0 0 mosn W=0.5u L=0.5u

C 4 2 100f

R 3 2 500k

.model mosp pmos level=1 vto=-1v kp=50u

+ tox=9e-9 cgdo=3.5e-10 cgso=3.5e-10 cgbo=4.5e-10

.model mosn nmos level=1 vto=1v kp=100u

+ tox=9e-9 cgdo=3.5e-10 cgso=3.5e-10 cgbo=4.5e-10

Vdd 1 0 5

.tran 100p 500n 0 100p

.probe

.end

Simulando si nota che il circuito non oscilla, ma resta nella condizione di equilibrio instabile in cui le tensioni ai

nodi 2, 3 e 4 sono pari alla soglia logica degli inverter (2.5V). Infatti la condizione di equilibrio è quella iniziale

(individuata da Spice come punto di lavoro) dalla quale si esce solo per effetto di perturbazioni che nel nostro

caso non sono state imposte.

Nota: variando i parametri si potrebbero trovare casi in cui la simulazione esce dalla condizione di equilibrio,

innescando le oscillazioni, pur senza specificare perturbazioni esplicite. Questo può avvenire per effetto delle

approssimazioni con cui viene risolto per via numerica il sistema di equazioni differenziali. Le approssimazioni

sono a tutti gli effetti delle perturbazioni della condizione di equilibrio.

Ponendo il W di Mn1 pari a 1u, si ottengono soglie logiche diverse per i due inverter. In questo caso la

condizione di equilibrio non è più V(2)=V(3)=V(4), ma quella in cui il primo inverter lavora sulla soglia logica

(con V(2)=V(3)) mentre il secondo risulta pilotato dal primo e fissa il valore di V(4) in base alla sua caratteristica

statica valutata per tensione d’ingresso pari a V(3). Infatti, tra i nodi 2 e 3 c’è solo una resistenza, che in

condizioni stazionarie non può essere attraversata da corrente, da cui V(2)=V(3). Al contrario, tra i nodi 3 e 4

c’è una capacità, che in condizioni stazionarie può sostenere differenze di potenziale tra i due nodi.

Per studiare le oscillazioni occorre assicurarsi che le oscillazioni si instaurino (non solo confidando nell’effetto

di approssimazioni). A tal fine si possono adottare diverse soluzioni tra cui:

1. La prima soluzione consiste nell’inserire un generatore di tensione Vp disaccoppiato dal resto del circuito

mediante una piccola capacità Cp. Se il generatore produce un gradino di tensione al tempo 10ns, in quel

momento la perturbazione determina l’inizio delle oscillazioni. Le righe da aggiungere al file d’ingresso di

Spice sono le seguenti:

Es5b: astabile con perturbazione in tensione

...

Vp 0 5 PWL(0 0 9.95n 0 10.05n 5)

Cp 5 2 10f

...

Si noti che, cessata la perturbazione, la capacità Cp si comporta come una capacità parassita verso un

nodo a tensione costante, e quindi influenza le costanti di tempo del sistema e in particolare l’andamento

della tensione al nodo . Aumentando Cp (rendendola ad esempio pari a C=100f) si noterà una riduzione

dei picchi di V(2), dovuta all’attenuazione dell’effetto bootstrap causata dalla ripartizione di carica tra C e

Cp.

Facoltà di Ingegneria – Università di Ferrara – A.A. 2001/2002

1

Elettronica 2

© Alessandro Bogliolo

2. Perturbazione in corrente: generatore di corrente che imponga un impulso di corrente al nodo 2 al tempo

10ns:

Es5c: astabile con perturbazione in corrente

...

Ip 0 2 PWL(0 0 9.95n 0 10n 0.1m 10.05n 0)

...

3. Specifica di condizioni iniziali diverse da quelle di equilibrio, mediante il comando .ic:

Es5d: astabile con condizioni iniziali esplicite

...

.ic v(2)=2.0

...

Le soluzioni migliori sono la 2 e la 3, poichè non alterano l’andamento delle oscillazioni, ma si limitano a

garantire l’instaurazione del regime oscillatorio. Poichè nella realtà le perturbazioni sono comunque presenti,

non occorrono accorgimenti specifici per uscire dalla condizione di equilibrio instabile, nella quale di fatto un

circuito reale non si troverebbe mai. Pertanto, le soluzioni proposte per uscire dall’equilibrio rappresentano solo

metodi per pilotare la simulazione, ma non rappresentano componenti addizionali di un circuito reale.

2. Duty-cycle diverso dal 50%

Per rendere il duty-cycle dell’onda quadra diverso dal 50% occorre rendere le costanti RC che regolano i

trasitori di salita e discesa al nodo 2 diverse tra loro. Per far questo si possono adottare diverse soluzioni:

1. Modificare i beta di Mn1 e Mp1, poichè la loro resistenza è in serie a R. Tuttavia, per il buon funzionamento

dell’oscillatore la resistenza R deve essere molto maggiore della resistenza d’uscita del primo inverter, le

cui variazioni incidono quindi marginalmente sulle costanti di tempo.

2. Inserire un diodo tra i nodi 2 e 3 che offra un percorso di corrente parallelo a R in una sola direzione. In

serie al diodo può essere posta una resistenza R1 per controllare la durata del transitorio. In questo caso

una costante di tempo sarebbe RC, l’altra (R//R1)C. La funzione del diodo per il controllo del trasitorio di

carica di V(2) può essere svolta da un transistore pMOS pilotato dal nodo 4 o dal nodo 2. Le forme d’onda

dei segnali sono lievemente diverse nei due casi.

Es5e: astabile con duty cycle diverso dal 50%

...

Mrise 2 4 5 1 mosp W=1u L=0.5u

R1 5 3 100K

...

3. Inserire due percorsi indipendenti di carica e scarica tra i nodi 2 e 3, con resisteze R1 ed R2

rispettivamente, controllati da due diodi orientati in versi opposti. I diodi possono essere realizzati da un

transistore pMOS e da un trasistore nMOS entrambi controllati dal nodo 4. In questo caso la permanenza

del valore alto e del valore basso d’uscita possono essere controllate indipendentemente.

Es5f: astabile con duty cycle diverso dal 50%

...

Mrise 2 4 5 1 mosp W=1u L=0.5u

R1 5 3 100K

Mfall 2 4 6 0 mosn W=0.5u L=0.5u

R2 6 3 200K

...

Se R1 ed R2 sono molo maggiori delle impedenze dei MOS, le due costanti di tempo risultano circa uguali

a R1C e R2C.

Si noti che qualunque sia il duty cycle il circuito ha comunque un punto di equilibrio instabile nel quale tende a

restare in assenza di perturbazioni. Pertanto, le modifiche proposte in questa sezione sono da combinare a

quelle proposte nella sezione precedente per garantire l’instaurazione delle oscillazioni.

Facoltà di Ingegneria – Università di Ferrara – A.A. 2001/2002

2