Elettronica Digitale

© Alessandro Bogliolo

Esercitazione 3: Linea LC (e uso di sottocircuiti)

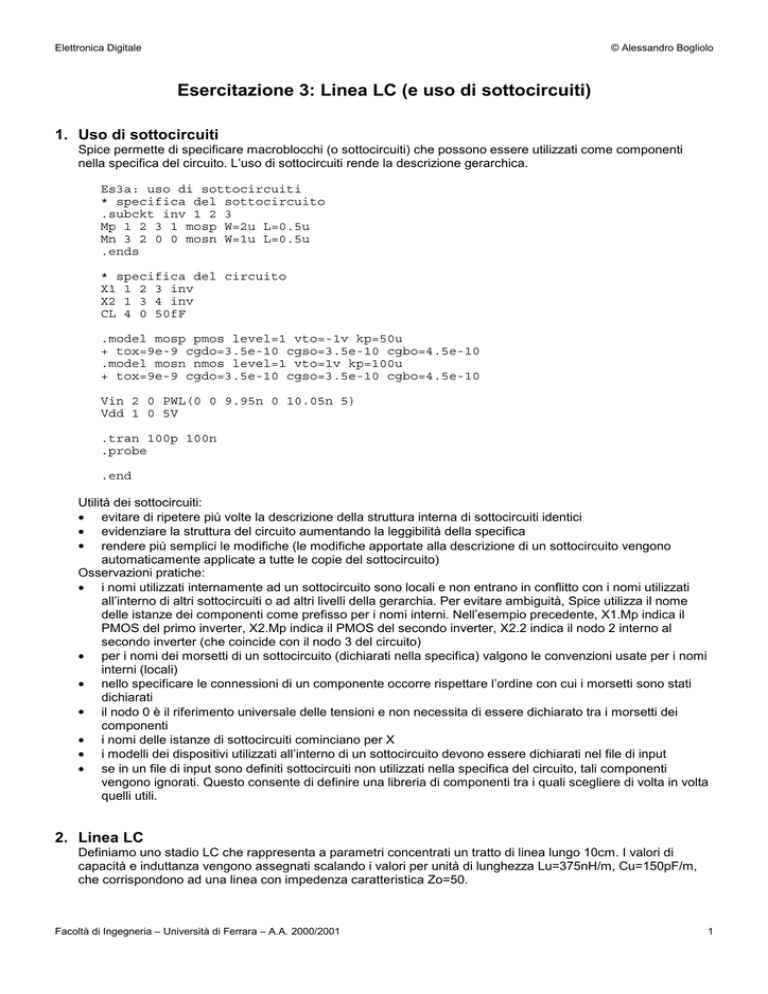

1. Uso di sottocircuiti

Spice permette di specificare macroblocchi (o sottocircuiti) che possono essere utilizzati come componenti

nella specifica del circuito. L’uso di sottocircuiti rende la descrizione gerarchica.

Es3a: uso di sottocircuiti

* specifica del sottocircuito

.subckt inv 1 2 3

Mp 1 2 3 1 mosp W=2u L=0.5u

Mn 3 2 0 0 mosn W=1u L=0.5u

.ends

* specifica del circuito

X1 1 2 3 inv

X2 1 3 4 inv

CL 4 0 50fF

.model mosp pmos level=1 vto=-1v kp=50u

+ tox=9e-9 cgdo=3.5e-10 cgso=3.5e-10 cgbo=4.5e-10

.model mosn nmos level=1 vto=1v kp=100u

+ tox=9e-9 cgdo=3.5e-10 cgso=3.5e-10 cgbo=4.5e-10

Vin 2 0 PWL(0 0 9.95n 0 10.05n 5)

Vdd 1 0 5V

.tran 100p 100n

.probe

.end

Utilità dei sottocircuiti:

• evitare di ripetere più volte la descrizione della struttura interna di sottocircuiti identici

• evidenziare la struttura del circuito aumentando la leggibilità della specifica

• rendere più semplici le modifiche (le modifiche apportate alla descrizione di un sottocircuito vengono

automaticamente applicate a tutte le copie del sottocircuito)

Osservazioni pratiche:

• i nomi utilizzati internamente ad un sottocircuito sono locali e non entrano in conflitto con i nomi utilizzati

all’interno di altri sottocircuiti o ad altri livelli della gerarchia. Per evitare ambiguità, Spice utilizza il nome

delle istanze dei componenti come prefisso per i nomi interni. Nell’esempio precedente, X1.Mp indica il

PMOS del primo inverter, X2.Mp indica il PMOS del secondo inverter, X2.2 indica il nodo 2 interno al

secondo inverter (che coincide con il nodo 3 del circuito)

• per i nomi dei morsetti di un sottocircuito (dichiarati nella specifica) valgono le convenzioni usate per i nomi

interni (locali)

• nello specificare le connessioni di un componente occorre rispettare l’ordine con cui i morsetti sono stati

dichiarati

• il nodo 0 è il riferimento universale delle tensioni e non necessita di essere dichiarato tra i morsetti dei

componenti

• i nomi delle istanze di sottocircuiti cominciano per X

• i modelli dei dispositivi utilizzati all’interno di un sottocircuito devono essere dichiarati nel file di input

• se in un file di input sono definiti sottocircuiti non utilizzati nella specifica del circuito, tali componenti

vengono ignorati. Questo consente di definire una libreria di componenti tra i quali scegliere di volta in volta

quelli utili.

2. Linea LC

Definiamo uno stadio LC che rappresenta a parametri concentrati un tratto di linea lungo 10cm. I valori di

capacità e induttanza vengono assegnati scalando i valori per unità di lunghezza Lu=375nH/m, Cu=150pF/m,

che corrispondono ad una linea con impedenza caratteristica Zo=50.

Facoltà di Ingegneria – Università di Ferrara – A.A. 2000/2001

1

Elettronica Digitale

© Alessandro Bogliolo

Definiamo lo stadio LC come sottocircuito per poterlo replicare agevolmente per rappresentare linee più

lunghe. Nel nostro caso connettiamo in cascata 4 stadi LC pilotati da un generatore di tensione, con resistenza

d’uscita Rs, che impone un gradino da 0 a 5V (con rampa di 0.1ns) al tempo 10ns.

Es3b: linea LC

.subckt LCline 1 2

L 1 2 37.5nH

C 2 0 15pF

.ends

X1

X2

X3

X4

3

4

5

6

4

5

6

7

LCline

LCline

LCline

LCline

Vin 2 0 PWL(0 0 9.95n 0 10.05n 5)

Rs 2 3 50

.tran 100p 100n

.probe

.end

Simulare il circuito per diversi valori di Rs (ad esempio 100, 20, 50) e osservare le forme d’onda ai nodi 3, 4, 5,

6 e 7.

• Inizialmente si osserva la propagazione di un’onda di ampiezza 5V*Zo/(Rs+Zo), tanto maggiore quanto

minore è Rs. Quando l’onda raggiunge il nodo 7 (fine della linea) viene interamente riflessa (poichè il

coefficiente di riflessione di una linea non terminata è 1) e si propaga all’indietro. Gli effetti delle onde

incidente e riflessa si sommano subito al nodo 7, che quindi subisce un gradino di ampiezza doppia

rispetto ai nodi precedenti. Da qui l’onda riflessa si propaga all’indietro contribuendo all’innalzamento

successivo del valore delle tensioni ai nodi 6, 5, 4 e 3. Al nodo 3 l’onda si riflette ulteriormente, con

coefficiente di riflessione pari a (Rs-Zo)/(Rs+Zo), e subisce la sorte dell’onda originale.

• Il tempo impiegato per raggiungere il nodo 7 è il tempo di volo.

• V(3) presenta un picco iniziale. Il nodo 3 collega la resistenza Rs del generatore d’ingresso all’induttanza

del primo stadio LC. Quando Vin passa da 0 a 5V, il nodo 3 tende a seguirlo poichè l’induttanza si oppone

a brusche variazioni di corrente e la caduta di tensione ai capi di Rs è nulla in assenza di corrente.

L’ampiezza del picco iniziale di V(3) è tanto maggiore quanto minore è Rs e ripido il fronte di Vin.

• Si osservano oscillazioni a frequenza più alta che si sovrappongono agli effetti di riflessione descritti in

precedenza. Tali oscillazioni sono dovute alle discontinuità tra gli stadi del nostro modello approssimato a

parametri concentrati.

• Per Rs=100, servono ripetute riflessioni (i cui effetti si sommano) per portare la linea a 5V. La forma d’onda

osservata ad ogni nodo della linea è una rampa a gradini di ampiezza decrescente che complessivamente

descrivono un transitorio con costante di tempo Rs*Ctot.

• Per Rs=20 la prima onda è già prossima a 5V, così che la sovrapposizione dell’onda riflessa determina il

superamento di 5V. L’onda riflessa alla sorgente si sottrae a quella incidente riportando la tensione sulla

linea al di sotto di 5V.

• Per Rs=50=Zo, la linea è adattata alla sorgente: l’onda che si propaga inizialmente ha ampiezza 5V/2 e la

prima onda riflessa porta la linea a 5V.

3. Linea LC che pilota invertitori CMOS

Colleghiamo invertitori CMOS con carico di 50fF ciascuno ai nodi 3, 5 e 7 della linea. La capacità di carico

degli inverter è specificata all’interno del sottocircuito inv. Chiamiamo 3a, 5a e 7a i nodi di uscita degli inverter.

Le linee da aggiungere all’esempio precedente sono le seguenti:

...

.subckt inv 1 2 3

Mp 1 2 3 1 mosp W=2u L=0.5u

Mn 3 2 0 0 mosn W=1u L=0.5u

CL 3 0 50fF

.ends

Xinv1 1 3 3a inv

Xinv2 1 5 5a inv

Xinv3 1 7 7a inv

.model mosp pmos level=1 vto=-1v kp=50u

Facoltà di Ingegneria – Università di Ferrara – A.A. 2000/2001

2

Elettronica Digitale

© Alessandro Bogliolo

+ tox=9e-9 cgdo=3.5e-10 cgso=3.5e-10 cgbo=4.5e-10

.model mosn nmos level=1 vto=1v kp=100u

+ tox=9e-9 cgdo=3.5e-10 cgso=3.5e-10 cgbo=4.5e-10

Vdd 1 0 5

...

Simulando ed osservando i segnali all’ingresso e all’uscita degli inverter si osserva che:

• L’impedenza caratteristica della linea cambia lievemente per effetto delle capacità d’ingresso degli inverter,

che si presentano in parallelo (e quindi si sommano) alle capacità degli stadi LC usati per modellare la

linea.

• per Rs=10, l’inverter più vicino alla sorgente commuta per primo, ma le oscillazioni sulla linea sono

percepite dagli inverter come transizioni d’ingresso che determinano oscillazioni spurie in uscita

• per Rs=75, l’inverter che commuta per primo è quello più lontano dalla sorgente, poichè è l’onda riflessa

che determina il superamento della tensione di soglia logica. L’uscita degli inverter non subisce oscillazioni

• per Rs=50, ogni inverter lavora in prossimità della soglia logica tra l’istante in cui è raggiunto dall’onda

incidente e l’istante in cui è raggiunto dall’onda riflessa che completa il transitorio di salita. Il primo inverter

a stabilizzarsi è il più lontano dalla sorgente.

• quando la linea è a potenziale prossimo alla soglia logica il consumo di potenza è alto. In particolare, gli

inverter pilotati dalla linea sono attraversati da una forte corrente di corto circuito.

Facoltà di Ingegneria – Università di Ferrara – A.A. 2000/2001

3