CAPITOLO 7

PORTE LOGICHE ECL

7.1 La porta elementare ECL

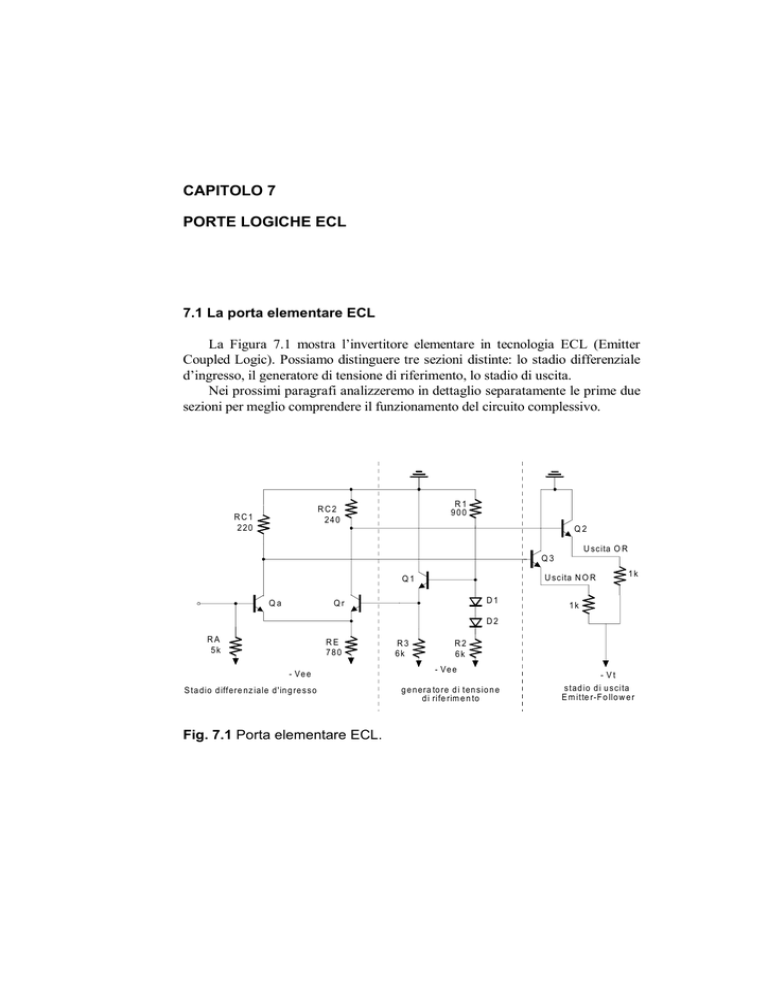

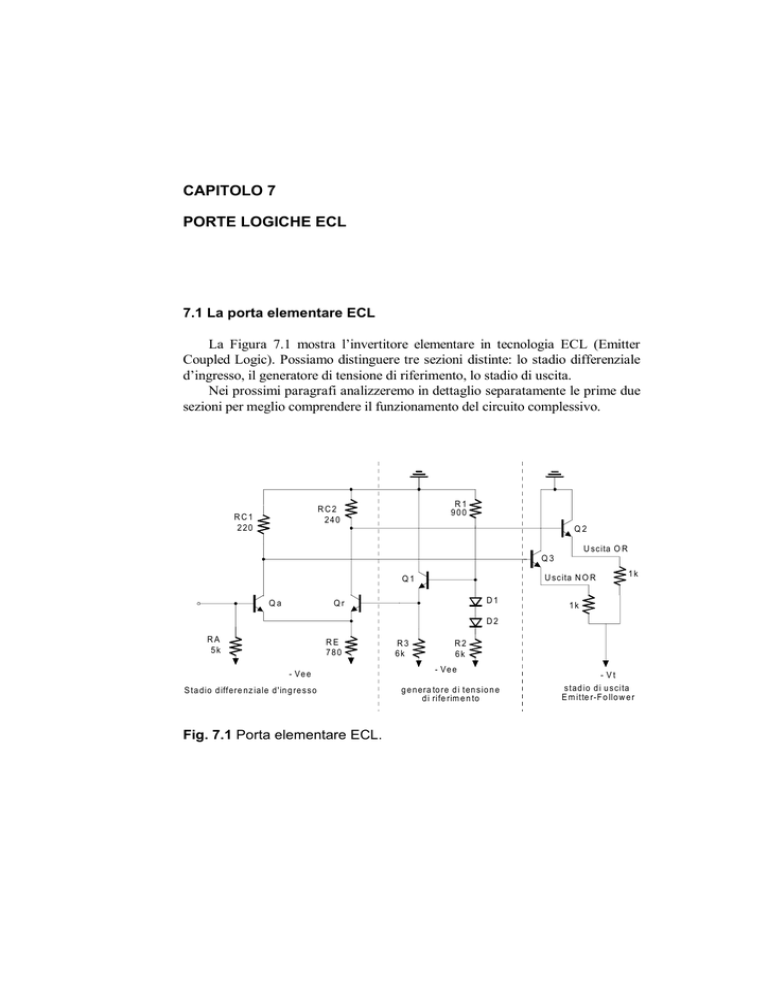

La Figura 7.1 mostra l’invertitore elementare in tecnologia ECL (Emitter

Coupled Logic). Possiamo distinguere tre sezioni distinte: lo stadio differenziale

d’ingresso, il generatore di tensione di riferimento, lo stadio di uscita.

Nei prossimi paragrafi analizzeremo in dettaglio separatamente le prime due

sezioni per meglio comprendere il funzionamento del circuito complessivo.

R1

900

RC2

240

RC1

220

Q2

U scita O R

Q3

U scita N O R

Q1

Qa

D1

Qr

1k

1k

D2

RA

5k

RE

780

- Ve e

S ta dio d iffere nz iale d'in g re sso

Fig. 7.1 Porta elementare ECL.

R3

6k

R2

6k

- Ve e

g e n era to re d i ten sio n e

d i rife rim e n to

- Vt

stad io d i u scita

E m itte r-F o llo w e r

2

Capitolo 7

_________________________________________________________________

Vcc = 5 V

RC1 = 1 k

RC2 = 1 k

V in

Q1

Q2

Ie = 2 m A

Ve e = -5 .2 V

Fig. 7.2 Stadio differenziale.

7.2 Lo stadio d’ingresso (l’amplificatore differenziale).

Cominciamo lo studio delle porte logiche non saturate partendo dal circuito

differenziale mostrato in figura 7.2

Per i transistori Q1 e Q2 utilizziamo la scheda .MODEL “standard”,

introdotta nel Capitolo 5, mentre per le resistenze, le alimentazioni ed il

generatore di corrente usiamo i valori riportati in figura 7.2.

Mediante SPICE effettuiamo una analisi in DC facendo variare il valore di

Vin tra -0.5V e 0.5V con passo di 0.01 V, ricordando che i terminali di substrato

dei transistori BJT vanno sempre connessi al nodo che presenta il valore di

potenziale più basso.

La Figura 7.3 mostra le correnti di emettitore dei due transistori. Si noti che

la corrente del generatore Ie si ripartisce fra Q1 e Q2, a seconda del valore di

tensione di ingresso. E’ sufficiente un valore di Vin pari a ±100mV per

commutare tutta la corrente Ie in uno solo dei due dispositivi.

Si noti che, con i valori utilizzati per le resistenze di collettore e per il

generatore Ie, i due transistori non lavorano mai in regione di saturazione. Infatti,

quando la corrente è commutata, ad esempio, nel solo transistore Q2 risulta:

VC2=VCC-RCIE = 5 - 1×2 = 3V. Poichè la tensione fra collettore e base è positiva,

la giunzione corrispondente è polarizzata inversamente ed il BJT opera in regione

attiva.

Porte logiche ECL

3

_________________________________________________________________

Fig. 7.3 Correnti di emettitore dei transistori Q1 e Q2.

La Figura 7.4 mostra lo schema effettivo dello stadio di ingresso della porta

ECL. Rispetto al circuito idealizzato di Figura 7.2, il generatore di corrente è

realizzato con una semplice resistenza RE collegata verso l’alimentazione

negativa Vee. Il valore di tale resistenza, rispetto alle resistenze di collettore,

risulta tale da consentire ai due transistori Q1 e Q2 di non raggiungere la

saturazione (per i segnali d’interesse). Il nodo di base del transistore Q2 è

collegata alla tensione di riferimento VR, negativa rispetto a massa, così come

negativa deve essere la tensione di ingresso Vin.

RC 1=230

V in

RC 2=230

Q1

Q2

RE=780

Ve e = -5 .2 V

Fig. 7.4 Stadio d’ingresso della porta ECL.

V R = -1 .2 V

4

Capitolo 7

_________________________________________________________________

Fig. 7.5 Andamento della corrente che fluisce nella resistenza RE.

La Figura 7.5 mostra l’andamento della corrente nella resistenza RE. Si noti

che tale corrente, a differenza di quanto avviene nel circuito ideale di Figura 7.2,

non è costante ma cresce quando la Vin supera il valore di VREF. In questo campo

di valori, infatti, la giunzione base-emettitore di Q1 è direttamente polarizzata e

dal circuito di Figura 7.4 otteniamo: IE = (Vin - 0.7 + VEE) / RE. La Figura 7.5,

peraltro, evidenzia che la corrente IE varia debolmente per variazioni della

tensione d’ingresso pari a VR±0.1V. Il valore nominale di IE (per Vin=VREF) è

pari a circa 4.2mA.

Le tensioni di uscita del circuito, prelevate fra i morsetti di collettore dei due

transistori e massa, sono mostrate in Figura 7.6

Fig. 7.6 Tensioni ai morsetti di collettore di Q1 e di Q2.

Porte logiche ECL

5

_________________________________________________________________

Consideriamo dapprima l’uscita al collettore di Q2. Per ingresso basso

(Vin<VR-0.1) il transistore Q1 è interdetto e tutta la corrente che fluisce in RE

attraversa anche la resistenza RC2. L'uscita al collettore di Q2 assume pertanto il

valore logico basso, corrispondente a: -RC2 × IE = -0.23×4.2 = -1.0V. Per

ingresso alto (Vin>VR+0.1) il transistore Q2 è interdetto e la tensione al collettore

di Q2 assume il valore di 0V.

Per l'uscita al collettore di Q1 si ha un comportamento duale, con la

differenza che per ingresso alto la corrente IE non è costante ma cresce

linearmente con Vin, come mostrato in Figura 7.5. Pertanto, per Vin>VR+0.1,

l'uscita VC1 decresce linearmente con Vin, con una pendenza pari a -RC1/RE.

Aumentando sempre più la Vin il transistore Q2 entra infine in regione di

saturazione (per Vin=-0.45V). Dopo questo punto la tensione di uscita al

collettore di Q1 si "aggancia" alla tensione di inmgresso, in quanto risulta:

Vc1=Vin-VBC1=Vin-0.7V. Si noti che il circuito è progettato in modo tale che nel

range nominale di variazione di Vin (comprso fra -1.7V e -0.7V) il transistore Q1

non opera mai in regione di saturazione.

7.3 Il generatore di tensione di riferimento.

Lo schema circuitale del generatore di tensione di riferimento è mostrato in figura

7.7 La scelta del valore delle tre resistenze inserite nel circuito determina il valore

della tensione di uscita ed il suo coefficiente di temperatura

R1

900

Q1

Vre f

D1

D2

R3

6k

R2

6k

-Ve e = -5 .2 V

Fig. 7.7 Generatore di tensione di riferimento.

6

Capitolo 7

_________________________________________________________________

Fig. 7.8 Tensione di riferimento VR al variare della tensione di

alimentazione e della temperatura.

La Figura 7.8 mostra la caratteristica di uscita del generatore di riferimento,

ottenuta al variare della tensione di alimentazione e per diversi valori di

temperatura. Per la simulazione SPICE a diverse temperature (nel nostro caso:

0°C, 50°C e 100°C) è necessario introdurre nel listato la scheda:

.temp 0 50 100

Si osservi dalla Figura 7.8 che la tensione di uscita diminuisce al crescere di

Vee e mostra inoltre un coefficiente di temperatura positivo. Queste dipendenze

sono introdotte volutamente al fine di compensare la caratteristica di

trasferimento della porta ECL rispetto alle variazioni termiche e della tensione di

alimentazione. Verifichiamo con semplici calcoli analitici i risultati mostrati in

Figura 7.8. Dal circuito di Figura 7.7 si ottiene facilmente:

VR = −

R1

(Vee − 2V D ) − V BE

R1 + R2

(7.1)

in cui si è indicato con VD la caduta sul diodo. Sostituendo i valori numerici

abbiamo: VR= - (0.9/6.9)×(5.2 - 2×0.7) - 0.7 = -1.2V. Dalla (7.1) si ricava:

dV R

R1

.

=−

= −013

dVee

R1 + R2

(7.2)

Porte logiche ECL

7

_________________________________________________________________

Per quanto concerne la dipendenza dalla temperatura, si deve ricordare che

la caduta su di una giunzione polarizzata direttamente decresce al crescere di T,

con un coefficiente di temperatura pari a:

dV BE dV D

=

= −δ = −2mV / ° C

dT

dT

(7.3)

Dalle (7.1) e (7.3) si ottiene immediatamente:

dV R

R − R1

2 R1

=−

δ +δ = 2

δ

dT

R1 + R2

R1 + R2

sostituendo i valori numerici si ha:

(7.4)

dVR

= 0.74δ = 148

. mV / ° C

dT

7.4 Analisi statica della porta ECL

Dopo aver analizzato lo stadio differenziale di ingresso e lo stadio regolatore

di tensione, passiamo allo studio del funzionamento della porta ECL completa di

Figura 7.1.

L’ultima sezione della porta ECL è composta dai due transistori montati a

collettore comune usati come buffer e necessari inoltre per traslare il segnale di

uscita di una VBE. I due emitter-follower, come i dispositivi dello stadio totem

della TTL, presentano un’area cinque volte maggiore rispetto a quelli utilizzati

nel resto del circuito.

Le caratteristiche di trasferimento della porta ECL, relative alle uscite OR e

NOR, sono mostrate in Figura 7.9. Si noti che il circuito è perfettamente

“bilanciato”, in quanto risulta VR=(VOH+VOL)/2.

Dalla simulazione SPICE è possibile ricavare i valori di VOH, VOL, VIH, VIL e

quindi calcolare i margini di rumore.

Ricordiamo che dalla teoria risulta:

VIL= VR - 0.1

VIH= VR + 0.1

VOH=-VBE

VOL=-VBE - VSW

(7.5)

(7.6)

(7.7)

(7.8)

dove lo swing logico VSW=RC×IE ed IE è la corrente di emettitore dello

stadio differenziale.

8

Capitolo 7

_________________________________________________________________

Fig. 7.9 Caratteristiche di trasferimento della porta ECL.

Simulazioni SPICE

Valori teorici

VOH

VOL

VIH

VIL

NMH

NML

-0.7 V

-1.7 V

-1.1 V

-1.3 V

0.4 V

0.4 V

Tab. 7.1 Margini di rumore della porta ECL.

Nel nostro caso IE=4.2mA e lo swing logico è pari a: VSW=0.24×4.2=1.0V,

mentre VR=-1.2V. Si ottengono pertanto i valori teorici riportati in Tabella 7.1.

Si lascia al lettore il compito di competare la tabella con i risultati delle

simulazioni SPICE relativi alle due uscite or e nor.

Data l’esiguità dei margini di rumore, le porte ECL vengono progettate in

modo da compensare le variazioni di VOH, VOL, VIH e VIL dovute sia a variazioni

di temperatura che della tensione di alimentazione. Poichè dalle (7.5)-(7.6)

risulta: (VIH + VIL)/2=VR, la condizione che si impone è la seguente:

(VOH + VOL)/2=VR, per ogni valore di T e di Vee

(7.9)

In questo modo i margini di rumore sono uguali fra loro (NMH=NML) ed

hanno il massimo valore possibile.

Utilizzando le (7.7)-(7.8) l’equazione (7.9) fornisce:

VR=(VOH + VOL)/2=(-VBE - VBE -VSW)/2 = -VBE - RC IE /2

(7.10)

Consideriamo ora la porzione del circuito della porta ECL riportata in

Figura 7.10.

Porte logiche ECL

9

_________________________________________________________________

R1

900

RC

240

Q1

D1

VR

Qr

VE + Ve e

RE

VB = VR + VB E

VR

D2

VE

IE =

Vx

RE

780

- Ve e

R3

6k

- Ve e

R2

6k

VE

I*=

VE + Ve e

R2

- Ve e

Fig. 7.10 Generatore di riferimento della porta ECL.

La tensione VB sul morsetto di base del transistore Q1 è pari a:

VB=VR+VBE. Imponendo la condizione (7.10) si ottiene:

VB= - RC IE /2

(7.11)

La tensione VB, trascurando la corrente di base di Q1, è data da:

VB= - R1 I*

(7.12)

in cui si è indicata con I* la corrente che fluisce in R1 ed R2. Dalla Figura

7.10, poichè le cadute su i due diodi D1 e D2 sono uguali alle tensioni baseemettitore di Q1 e Q2, si ottiene:

I* =

V E + Vee

R

= IE E

R2

R2

(7.13)

Dalle (7.12)-(7.13) risulta:

VB = −

R1

I E RE

R2

(7.14)

10

Capitolo 7

_________________________________________________________________

Poichè vogliamo che sia verificata la condizione (7.11) deve risultare:

-(R1/R2)IE RE = - RC IE /2 , ovvero:

R1/R2 = ½ RC/RE

(7.15)

In definitiva, la condizione (7.9) è verificata se il rapporto fra le resistenze

R1 ed R2 è pari alla metà del rapporto fra RC ed RE. Nel caso del circuito di

Figura 7.1, sostituendo i valori numerici, abbiamo: R1/R2 = 0.9/6=0.15, ed

inoltre: ½ RC/RE = 0.5 × 0.24/0.78 = 0.15.

Per verificare tramite SPICE che la porta ECL sia effettivamente

indipendente dalle variazioni della temperatura e della tensione di alimentazione,

è interessante effettuare delle simulazioni della caratteristica di trasferimento, al

variare di Vee e di T.

La Figura 7.11 mostra la caratteristica di trasferimento per tre valori di

tensione di alimentazione, pari a: -Vee=-4.8V, -5.2V e -5.6V. I valori di VOH,

VOL e VR per -Vee=-4.8V sono riportati in Tabella 7.2. Si lascia al lettore il

compito di completare la tabella per gli altri valori di Vee.

Fig. 7.11 Caratteristica di trasferimento al variare di Vee.

Vee=-4.8V

Vee=-5.2V

Vee=-5.6V

VOH

-0.75

VOL

-1.60

½(VOH+VOL)

-1.18

VR

-1.17

NMH

0.33

Tab. 7.2 Margini di rumore della porta ECL al variare della Vee.

NML

0.33

Porte logiche ECL

11

_________________________________________________________________

Fig. 7.12 Caratteristica di trasferimento al variare della temperatura.

T=0°C

T=50°C

T=100°C

VOH

-0.79

VOL

-1.72

½(VOH+VOL)

-1.26

VR

-1.25

NMH

0.36

NML

0.36

Tab. 7.3 Margini di rumore della porta ECL al variare della temperatura

La Figura 7.12 mostra la caratteristica di trasferimento della porta ECL per

-Vee=-5.2V e per tre valori di temperatura: T=0°C, 50°C 100°C. I valori di VOH,

VOL e VR per T=0°C sono riportati in Tabella 7.3. Anche in questo caso si lascia

al lettore il compito di completare la tabella per gli altri valori di temperatura.

Per completare l’analisi statica dlla porta ECL, la figura 7.13 riporta la

potenza dissipata dal circuito al variare di Vin. Si noti che la potenza dissipata è

è all’incirca la stessa nei due stati logici; la potenza media è di circa 37mW.

La figura 7.14 riporta infine le correnti assorbite dai vari stadi della porta

ECL. Si noti che le correnti che scorrono nei resistori di pull-down delle due

uscite OR e NOR sono basse, grazie all’elevato valore delle resistenze (5kΩ). I

valori di corrente sarebbero molto maggiori qualora il valore delle resistenze

dovesse essere scelto in modo da adattare l’uscita della porta ad una linea di

trasmissione.

12

Capitolo 7

_________________________________________________________________

Fig. 7.13 Potenza statica dissipata dalla porta ECL.

Fig. 7.14 Correnti assorbite dai vari stadi della porta ECL.

7.5 Analisi Dinamica

Per effettuare l'analisi dinamica della risposta della ECL consideriamo come

carico di uscita una capacità di 5 pF. La Figura 7.15 mostra i risultati di una

simulazione SPICE ottenuta per tre valori di resistenze collegate alle uscite OR e

NOR: 500Ω, 2kΩ e 5kΩ.

Porte logiche ECL

13

_________________________________________________________________

Fig. 7.15 Transitorio della porta ECL.

Fig. 7.16 Tensioni ai nodi di collettore dello stadio differenziale.

La Figura mostra che il tPLH=0.54ns non dipende dal valore delle resistenze,

che viceversa influenza in maniera determinante il valore di tPHL, che vale 0.45ns,

1.0ns e 3.7ns a seconda del valore di R.

La Figura 7.16 mostra l’andamento delle tensioni ai nodi di collettore dello

stadio differenziale ed evidenzia il ridotto valore del tempo di propagazione del

primo stadio della porta ECL.

14

Capitolo 7

_________________________________________________________________

ECL1

ECL2

20

-Vee

30

R = 2k

-Vee

Fig. 7.17 Due porte ECL collegate da una linea di trasmissione.

Adattamento alle linee di trasmissione.

Vista la velocità di commutazione delle porte ECL è spesso necessario

considerare i collegamenti fra più porte logiche come linee di trasmissione,

caratterizzate da un valore di impedenza caratteristica Z0 e di ritardo TD. Valori

tipici di Z0, per interconnessioni su di un circuito stampato, sono compresi fra 50

e 200Ω, mentre il ritardo TD è pari al rapporto fra la lunghezza L della linea e la

velocità di propagazione.

La Figura 7.17 mostra due porte ECL connesse mediante una linea di

trasmissione caratterizzata da una impedenza caratteristica pari a 100Ω e da un

ritardo pari a 2ns. Per il circuito di figura 7.20 è necessario introdurre nel listato

SPICE la seguente scheda, relativa alla linea di trasmissione:

TL1 20 0 30 0 Z0=100 TD=2n

Per le due porte ECL è opportuno utilizzare uno schema semplificato, in cui

il circuito che genera la tensione di riferimento è sostituito da un semplice

generatore costante di tensione.

I risultati di una simulazione SPICE in transistorio sono riportati in Figura

7.18, nel caso in cui la resistenza R (vedi figura 7.17) è pari a 2kΩ. Il mancato

adattamento della linea di trasmissione comporta la presenza di riflessioni. In

corrispondenza del transitorio basso-alto dell’uscita della prima porta ECL si

evidenziano dei fenomeni di “ringing”, mentre in corrispondenza dell’altra

commutazione la presenza della linea di trasmissione aumenta in maniera

sensibile il tempo di propagazione.

Soffermiamo la nostra attenzione sul primo transitorio. La Figura 7.19

mostra l’andamento della tensione all’uscita della prima porta ECL e quello

all’ingresso della seconda porta ECL. Nel grafico ad entrambi i segnali è stata

sommato un valore costante, pari a VOL=-1.7V, in modo che le forme d’onda

partono dal valore iniziale di 0V.

Porte logiche ECL

15

_________________________________________________________________

Fig. 7.18 Simulazione in transitorio di due porte ECL collegate con una

linea di trasmissione.

Fig. 7.19 Particolare della Figura 7.18. Alle forme d’onda è sommata

una costante pari a VOL.

Per spiegare l’andamento delle forme d’onda di Figura 7.19 consideriamo il

modello semplificato mostrato in Figura 7.20, in cui la prima porta ECL è

rappresentata mediante un generatore di tensione a gradino di ampiezza pari a

VSW=VOH-VOL=1V ed una resistenza serie RS, mentre si assume che la resistenza

di ingresso della seconda porta ECL sia molto maggiore di R.

Il valore di RS si può ottenere osservando che l’ampiezza del primo gradino

di tensione all’uscita della ECL1 è pari a: V1=VSWZ0/(RS+Z0)=0.93V. Si ricava

pertanto: RS=Z0×(VSW/V1-1)=100×(1/0.93 -1)=7.5Ω, un valore prossimo a

quello teorico: RC/βF=240/50=4.8Ω.

16

Capitolo 7

_________________________________________________________________

ECL1

RS=7 .5

TD =2 ns

Z 0 =1 00

VS W =1 V

R = 2k

Fig. 7.20 Modello semplificato del circuito di Figura 7.17.

Fig. 7.21 Forme d’onda per il circuito di Figura 7.20.

Il risultato di una simulazione SPICE del circuito di Figura 7.20 è riportato

in Figura 7.21. Nella simulazione SPICE è opportuno ridurre il passo di

integrazione ad un decimo del tempo di ritardo della linea di trasmissione

utilizzando la scheda:

.tran 0 30n 0 200ps

I risultati di Figura 7.21 possono essere ottenuti analiticamente, osservando

che la linea di trasmissione non è adattata né in ingresso né in uscita. Il

coefficiente di riflessione in ingresso è pari a: ρS=(RS-Z0)/(RS+Z0)=-0.86; il

coefficiente di riflessione in uscita è: ρL=(R-Z0)/(R+Z0)=0.90.

La Figura 7.22 mostra il diagramma a scala corrispondente al circuito di

Figura 7.20. Le due linee verticali a sinistra ed a destra rappresentano l’ingresso

e l’uscita della linea di trasmissione.

Porte logiche ECL

17

_________________________________________________________________

VS (0)= 0.93V

0.93 0.93

0.84(1+ ρS )

VS (2TD)= 0.93+0.12= 1.05

= 0 .12 -0.72

VS (4TD)= 1.05-0.09=0.96

-0.09

VS (6TD)= 0.96+0.07= 1.03

0.07

0.84

-0.65

0.56

0.50

-0.43

0.39

1+ ρS= 0.14 ρS = -0.86

0.93(1+ ρL )

= 1 .77

VL (TD )= 1.77V

-1.37

VL (3TD)= 1.77-1.37=0.4V

1.06

VL (5TD)= 0.4+ 1.0 6=1.4 6V

-0.82

VL (7TD)= 1.46-0.82=0.64V

ρL = 0.90 1+ ρL= 1.90

Fig. 7.22 Diagramma a scala per il circuito di Figura 7.20.

Al tempo TD il gradino di tensione di ampiezza V1=0.93V raggiunge l’uscita

della linea di trasmissione. Si manifesta un’onda riflessa di ampiezza

ρLV1=0.84V che torna verso l’ingresso della linea. All’uscita della linea si ha un

gradino di tensione di ampiezza pari alla somma di V1 e dell’onda riflessa:

∆V=V1+ρLV1=(1+ρL)V1. Al tempo 2TD l’onda riflessa raggiunge l’ingresso

della linea di trasmissione, generando una ulteriore riflessione. Si ottengono in

questo modo i valori di tensione riportati nel diagramma a scala e nelle forme

d’onda di Figura 7.21.

Ritornando ai risultati della simulazione delle porte ECL di Figura 7.19, si

nota che il “ringing” è meno accentuato rispetto al circuito idealizzato di Figura

7.20. Ciò è attribuibile al fatto che il primo gradino di tensione che giunge in

ingresso alla seconda porta ECL è di ampiezza tale da portare in saturazione lo

stadio differenziale. In queste condizioni non è possibile trascurare la resistenza

di ingresso della porta ECL rispetto alla resistenza R ed il coefficiente di

riflessione ρS diviene molto minore rispetto al valore inizialmente previsto di 0.9.

Consideriamo ora il secondo transitorio in Figura 7.18, quando l’uscita della

prima porta ECL effettua una transizione alto-basso. In questo caso il transistore

di uscita della porta ECL tende a portarsi in interdizione, per cui la resistenza di

uscita della porta ECL aumenta sensibilmente rispetto al valore di RS=7.5Ω

stimato in precedenza. Il grafico di Figura 7.18 mostra che in questo caso la RS

diviene maggiore rispetto all’impedenza caratteristica della linea Z0=100Ω;

infatti l’ampiezza del primo gradino di tensione all’uscita della ECL1 è inferiore

a VSW/2. Questo secondo transitorio è particolarmente indesiderabile in un

circuito digitale sia perchè comporta un aumento del tempo di propagazione

complessivo, sia perchè il segnale di ingresso della seconda porta può “oscillare”

più volte all’interno della fascia di incertezza compresa fra VIL e VIH,

comportando commutazioni spurie all’uscita.

18

Capitolo 7

_________________________________________________________________

Fig. 7.23 Simulazione in transitorio di due porte ECL collegate con una

linea di trasmissione con terminazione in parallelo.

Gli inconvenienti evidenziati nelle forme d’onda di Figura 7.18 possono

essere eliminati adattando opportunamente la linea di trasmissione. Il caso più

semplice è quello della terminazione in parallelo, in cui il valore della resistenza

R di Figura 7.17 viene scelto pari alla impedenza caratteristica Z0 della linea di

trasmissione. La corrispondente simulazione SPICE è riportata in Figura 7.23 ed

evidenzia l’assenza di fenomeni di riflessioe.

Per ridurre la dissipazione di potenza la resistenza R è stata collegata ad un

generatore di tensione ausiliario di 2V; nonostante questo accorgimento si noti in

Figura 7.23 l’abbassamento dei valori di tensione in uscita dovuto all’aumento

della VBE dei transistori dello stadio di uscita causato dagli elevati valori di

corrente nella resistenza R.

Porte logiche ECL

19

_________________________________________________________________

ELABORATI PROPOSTI

1.

a) Progettare una porta ECL che soddisfi le seguenti specifiche: swing

logico VSW=0.6V; tensione di alimentazione: -VEE=-3.3V; corrente nello

stadio differenziale per ingresso basso: IE=1mA. Ipotizzare che la tensione

di riferimento sia prodotta da un opportuno generatore di tensione costante.

b) Simulare con SPICE il circuito progettato al punto a) e verificarne il

corretto funzionamento.

c) Progettare il generatore di tensione di riferimento per la porta ECL del

punto a). Il generatore di riferimento deve compensare possibili variazioni

di VEE e di temperatura.

d) Verificare con SPICE il corretto funzionamento della porta ECL

progettata al punto a) con il generatore di tensione di riferimento progettato

al punto c). Valutare i margini di rumore al variare di VEE fra -3.0V e -3.6V

2.

Nei circuiti digitali bipolari ad alta velocità si utilizzano delle porte logiche

pilotate in corrente (CML o current-mode logic). La Figura 7.24 mostra lo

schema di una porta CML costituita, in pratica, dal solo stadio differenziale

e da un generatore di tensione di riferimento.

a) Determinare i valori delle resistenze RE ed RC e della tensione di

riferimento VR in modo da soddisfare le seguenti specifiche: swing logico

VSW=400mV, corrente del differenziale per ingresso basso IE=1mA. La

tensione di alimentazione è: -Vee=-3.3V (suggerimento: il valore di

VOH=0V). Qual’è il valore di VCE per i due transistori per Vin=VOH e

Vin=VOL?

RC

RC

OR

NOR

V in

Q1

Q2

VR

RE

-Ve e

Fig. 7.24 Porta CML

20

Capitolo 7

_________________________________________________________________

RC

RC

OR

NOR

Q1

V in

Q2

RE

-Ve e

VR

R1

D1

R2

-Ve e

Fig. 7.25 Porta CML con generatore di tensione di riferimento.

b) La Figura 7.25 mostra una porta CML completa del generatore di

tensione di riferimento, costituito da due resistenze ed un diodo. Calcolare il

rapporto R1/R2 in modo che il generatore di riferimento eroghi la tensione

VR calcolata al punto a) (nell’analisi trascurare la corrente di base di Q2).

Dimostrare che con questo valore di R1/R2 la porta CML è compensata

rispetto a variazioni di tensione di alimentazione e di temperatura.

c) Simulare con SPICE la caratteristica di trasferimento della porta CML di

Figura 7.25 e valutare i margini di rumore per -Vee=-3V, -3.3V e -3.6V.

Simulare i tempi di propagazione del circuito, ipotizzando la presenza di

due capacità di carico alle uscite OR e NOR di 100fF. Simulare, infine, un

oscillatore ad anello costituito da tre porte CML invertenti.

3.

a) Si consideri la porta ECL di Figura 7.1 in cui le resistenze di pull-down

alle uscite OR e NOR abbiano un valore di 10kΩ invece di 1kΩ. Progettare

i valori delle altre resistenze in modo da ridurre la dissipazione di potenza

del circuito ad un valore non superiore a 10mW, mantenendo inalterati i

valori dei livelli logici.

b) Determinare le caratteristiche di ingresso e di uscita del circuito e

valutare il massimo valore del fan-out, considerando accettabile una

degradazione dei margini di rumore non superiore al 10% rispetto ai valori

nominali.

c) Simulare con SPICE il circuito progettato, valutando la potenza

dissipata, i margini di rumore ed il fan-out e verificando la correttezza del

progetto.

d) Valutare con SPICE il ritardo di propagazione del circuito al variare

della capacità di carico nel range 0.1pF-5pF e riportare i valori in un

grafico. Commentare i risultati ottenuti.

Porte logiche ECL

21

_________________________________________________________________

EC L 1

-Vee

EC L 2

(a )

EC L 2

R

R

-Vee

-Vee

EC L 1

EC L 1

-Vee

EC L 2

R1

(b )

EC L 1

(c )

-Vee

EC L 2

RS

RP

R2

-Vee

-VT =-2 V

-Vee

-Vee

-Vee

-Vee

(d )

-Vee

Fig. 7.26 Esempi di adattamento per un circuito costituito da due porte

ECL interconnesse mediante una linea di trasmissione.

4.

In figura 7.26 sono riportati alcuni esempi di adattamento per un circuito

costituito da due porte ECL interconnesse mediante una linea di

trasmissione con Z0=200Ω e TD=2ns. Il circuito (a) rappresenta un

adattamento all’uscita della linea; nel circuito (b) si ha ancora un

adattamento all’uscita, utilizzando un generatore di tensione ausiliario

VT=-2V; nel circuito (c) si ha una terminazione di tipo Thevenin; nel

circuito (d) si ha un adattamento di tipo serie.

a) Calcolare la potenza dissipata nella resistenza R=Z0=200Ω nei due

circuiti di Figura 7.27(a) e 7.27(b); calcolare inoltre il valore massimo della

corrente di emettitore del transistore di uscita della ECL1.

b) Calcolare i valori delle resistenze R1 ed R2 nel circuito di Figura

7.27(c), in modo tale la rete costituita dai due resistori e dal generatore -Vee

abbia un circuito equivalente secondo Thevenin costituito da una resistenza

equivalente R=200Ω ed una tensione equivalente V=-2V. Calcolare la

potenza dissipata nella resistenze R1 ed R2 ed il valore massimo della

corrente di emettitore del transistore di uscita della ECL1.

c) Simulare con SPICE i circuiti in Figura 7.26(a,b,c) e verificare i calcoli

dei punti a) e b) e verificare inoltre il corretto adattamento della linea di

trasmissione.

d) Simulare con SPICE il circuito di figura 7.27(d) assumendo RS=200Ω ed

utilizzando per RP i valori: 500Ω, 1kΩ, 2kΩ. In quali casi si ha un

adattamento soddisfacente della linea di trasmissione? Quanto vale la

potenza dissipata nella resistenza RP ed il valore massimo della corrente di

emettitore del transistore di uscita della ECL1?

22

Capitolo 7

_________________________________________________________________

Rx

Rx

Rx

Rx

R1

90 0

RC 2

24 0

RC 1

22 0

te rm in a le

d i m a ssa

Rx

Rx

Q2

Q3

RO R

Q1

Qa

D1

Qr

RNOR

D2

RA

5k

RE

78 0

R2

6k

R3

6k

- Ve e

- Ve e

- Ve e

Fig. 7.27 Porta ECL con resistenze parassite sulla linea di massa.

Rx

Rx

RC 1

22 0

te rm in a le

d i m a ssa

Rx

Rx

Rx

Rx

R1

90 0

RC 2

24 0

Rx

Q2

te rm in a le

d i m a ssa

Q3

RO R

Q1

Qa

D1

Qr

D2

RA

5k

RE

78 0

- Ve e

R3

6k

RNOR

R2

6k

- Ve e

- Ve e

Fig. 7.28 Porta ECL con due terminali di massa.

5.

Nelle porte ECL disponibili commercialmente ci sono due terminali di

massa, uno dedicato ai transistori dello stadio di uscita ed uno alla

rimanente parte del circuito.

Porte logiche ECL

23

_________________________________________________________________

Consideriamo il circuito di Figura 7.27, in cui è presente un solo terminale

di massa ed in cui sono evidenziate le inevitabili resistenze parassite Rx

presenti all’interno del circuito sulla linea di massa.

a) Simulare il circuto di Figura 7.27, assumendo Rx=7Ω, nei due casi:

i) ROR=RNOR=1kΩ

ii) ROR=500Ω; RNOR=1kΩ

Valutare VOH, VOL, VIH e VIL ed i margini di rumore, assumendo che sia a

monte che a valle vi siano due porte ECL caratterizzate dai valori nominali:

VOH=-0.7V; VOL=-1.7V; VIH=-1.1V; VIL=-1.3V.

A cosa è attribuibile la modifica dei livelli logici?

Nel caso (i), calcolare analiticamente il valore della tensione di riferimento.

b) Nel circuito di Figura 7.28 si utilizzano due terminali di massa. Simulare

il circuto di Figura 7.27, sempre assumendo Rx=7Ω, nei due casi i) ed ii)

del punto a).Valutare VOH, VOL, VIH e VIL ed i margini di rumore,

assumendo che sia a monte che a valle vi siano due porte ECL

caratterizzate dai valori nominali: VOH=-0.7V; VOL=-1.7V; VIH=-1.1V;

VIL=-1.3V. Commentare i risultati ottenuti.