Università degli Studi di Roma Tor Vergata

Dipartimento di Ing. Elettronica

corso di

ELETTRONICA APPLICATA

Prof. Franco Giannini

Realizzazione elettronica a cura di:

Ing. Rocco Giofrè

Ing. Marco Imbimbo

Ing. Patrick Longhi

Ing. Antonio Nanni

Ing. Augusto Ticconi

I/1

Libro di riferimento (consigliato)

Terza edizione 2005

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I/2

CIRCUITI ELETTRONICI ANALOGICI (I)

L'analisi di circuiti elettronici richiede preliminarmente la creazione di modelli matematici di

maggiore o minore complessità, a seconda del campione di frequenza di interesse, e/o di

appropriati circuiti equivalenti dei dispositivi a semiconduttore che vengono normalmente usati a

livello di realizzazione ibrida e monolitica.

Tra i dispositivi normalmente utilizzati, ci limiteremo a:

Diodi a giunzione

Diodi Schottky

Transistore bipolare a giunzione (BJT, HBT, DHBT)

Transistore ad effetto di campo (JFET, MOSFET, MESFET, LDMOS, HEMT, PHEMT, )

L'approccio da seguire può essere duplice:

Creazione di modelli matematici o circuitali o derivati dalla rappresentazione matematica dei

processi fisici che regolano il funzionamento dei dispositivi.

Creazione di modelli circuitali a partire da un'analisi delle caratteristiche esterne (ai

morsetti) del dispositivo espresse in forma puramente grafica (curve caratteristiche) senza

riferimento diretto ai processi fisici alla base del suo funzionamento.

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I/3

CIRCUITI ELETTRONICI ANALOGICI (II)

Indipendentemente dall'approccio seguito, comunque, il generico dispositivo elettronico, il diodo

a giunzione per esempio, può essere rappresentato in uno dei modi seguenti:

simbolo circuitale

+

A

K

-

i

N.B.

Le rappresentazioni hanno sempre una

validità limitata e devono pertanto essere

utilizzate con la dovuta cautela.

Per esempio tali rappresentazioni, non

esplicitano la dipendenza dalla frequenza del

funzionamento del dispositivo.

Quindi possono essere correttamente usate

solo in continua e/o per frequenze

sufficientemente basse (approssimazione

quasi statica).

⎛ v

⎞

⎜ VT

⎟

i = I 0 ⎜ e − 1⎟

⎜

⎟

⎝

⎠

legge matematica

I

Curva caratteristica I-V

V

R

D

Vγ

Circuito Equivalente

+

Ri

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I/4

Università degli Studi di Roma Tor Vergata

Dipartimento di Ing. Elettronica

corso di

ELETTRONICA APPLICATA

Prof. Franco GIANNINI

I SEMICONDUTTORI

I/5

SOMMARIO

Introduzione

I Semiconduttori

Il Diodo

Metodi di analisi di circuiti a diodi

Tipi di circuiti a diodo

Transistor a giunzione BJT

Primi circuiti a BJT

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I/6

SEMICONDUTTORI

Ad eccezione dei dispositivi bulk, che sfruttano direttamente alcune delle proprietà peculiari

del semiconduttore, la maggior parte dei dispositivi elettronici sfrutta le proprietà delle

giunzioni o tra materiali semiconduttori a differenti drogaggi, cioè con differenti concentrazioni

di impurezze (giunzione p-n), oppure tra metallo e semiconduttore (giunzione Schottky).

Lo studio di tali dispositivi richiede perciò la conoscenza delle proprietà chimiche, fisiche,

termiche ed elettriche sia del semiconduttore instrinseco, cioè "puro", sia estrinseco, cioè

"drogato", ovvero ottenuto con l'aggiunta di opportune concentrazioni di impurezze.

La moderna tecnologia elettronica utilizza un gran numero di materiali semiconduttori sia

"semplici", cioè costituiti da un'unica specie atomica, ad esempio il germanio ed il silicio, sia

"composti", cioè costituiti da più specie atomiche, come ad esempio l'arseniuro di gallio

(GaAs), il fosfuro di indio (InP), il nitruro di gallio (GaN), il carburo di Silicio (SiC), il SilicioGermanio (SiGe).

SiC

InP

GaAs

GaN

Si

Ge

Mobilità elettroni [ cm2/V·S ]

900

5400

8500

1000

1300

3800

Mobilità lacune [ cm2/V·S ]

300

500

400

200

500

1800

3

1.24

1.43

3.1

1.21

0.785

1.8/2.2

1.0/2.5

1.3/2.1

1.3/2.1

9

8

12.9

14

12

16

Concentrazione intrinseca [ cm-3 ]

106

107

1.79 x 106

1.5x106

5x1022

4.4x1022

Breakdown [ MV/cm ]

3.0

0.5

0.4

3.0

Conduc. Termica [ W/cm·K ]

4.5

0.7

0.5

1.5

Resistenza substrato [ Ωcm ]

1 -20

> 1000

> 1000

> 1000

>1000

45

MESFET, HEMT

JFET, BJT,

MOS

JFET, BJT

Energy gap [ eV ]

Vsat. degli elet. [ 107cm/s ]

Costante dielettrica relativa

Transistor

MESFET,

HEMT

MESFET, HEMT, HBT, PHEMT

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I/7

SEMICONDUTTORE INTRINSECO

elettrone

libero

lacuna

Il silicio è il più importante dei semiconduttori utilizzati nella realizzazione dei dispositivi

elettronici sia discreti che integrati. Ha una struttura cristallina che consiste nell'ordinata

ripetizione spaziale di una cella tetraedrica, con un atomo in ogni vertice, tenuta insieme dai

legami covalenti dei quattro elettroni di valenza di ogni atomo.

Allo zero assoluto, ogni elettrone rimane strettamente legato al nucleo e la conduttività è

zero. All'aumentare della temperatura alcuni legami covalenti si rompono e gli elettroni, così

liberati, possono "condurre" (conduzione per elettroni liberi).

il legame spezzato corrisponde ad un posto vuoto (lacuna) per gli altri elettroni che

partecipano al legame covalente, posto che possono facilmente occupare lasciando, a loro

volta, un altro posto vuoto.

La lacuna può perciò "viaggiare" lungo il cristallo contribuendo alla conduzione totale come

carica positiva (conduzione per lacune).

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I/8

SEMICONDUTTORE ESTRINSECO DI TIPO n

elettrone

libero

Ge

Ge

Ge

Sb

Ge

Ge

EC= Banda di conduzione

Ec

ED

ED= Livello donori

EFi

EG

Ev

Ge

Ge

Ge

EFi= Livello di Fermi

EV= Banda di valenza

Aggiungendo ad un semiconduttore intrinseco, il silicio ad esempio, quantità anche

relativamente piccole di impurezze, se ne cambiano in modo radicale le caratteristiche, a

cominciare da quelle di conduzione.

Aggiungendo ad esempio un tipo di impurezze pentavalenti (fosforo, arsenico, antimonio),

alcuni atomi del reticolo sono sostituiti dalla nuova specie atomica che satura i quattro

legami covalenti dell'atomo sostituito, ma ha ancora un quinto elettrone a disposizione.

Tale elettrone, che risulta poco legato al reticolo può facilmente "liberarsi" per effetto della

temperatura e partecipare al processo di conduzione.

In termini di bande di energia, ciò corrisponde ad inserire, all'interno dell'energy gap (EG),

un livello vicino alla banda di conduzione dal quale gli elettroni possono facilmente "saltare"

nella banda di conduzione stessa e partecipare ai processo di conduzione elettrica del

cristallo ospite, che in questo caso si dice drogato di tipo “n”.

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I/9

SEMICONDUTTORE ESTRINSECO DI TIPO p

Ge

Ge

Ge

Ec

lacuna

Ge

Ge

In

Ge

EC= Banda di conduzione

EFi= Livello di Fermi

Ge

EFi

Ge

EA

Ev

EA= Livello accettori

EV= Banda di valenza

L'aggiunta al semiconduttore intrinseco tetravalente di impurezze di tipo trivalente (boro,

gallio, indio), produce la sostituzione nel reticolo del cristallo ospite di alcuni atomi con quelli

della nuova specie atomica che non è in grado però di saturare tutti e quattro i legami

covalenti disponibili. Si vengono a creare così una serie di "disponibilità" per gli altri elettroni

del reticolo, che possono con facilità spostarsi, occupando la "lacuna" creata dall'atomo di

impurezza.

Dal punto di vista energetico ciò comporta la creazione, sempre all'interno dell'energy gap,

di un livello molto vicino alla banda di valenza, in grado di "accettare" gli elettroni della

banda di valenza stessa.

Tali elettroni lasciano a loro volta un gran numero di "lacune" che possono partecipare al

processo di conduzione del cristallo ospite che, in questo caso, si dice drogato di tipo

“p”.

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 10

PROPRIETA’ FISICHE DEI SEMICONDUTTORI (I)

Legge di azione di massa

np =

ni2

3

= A0T e

−

ni= N° portatori intrinseci

Eg

Eg= Energy gap

kT

k= Costante di Boltzmann

Aggiungendo ad un semiconduttore intrinseco impurezze di tipo "n" (donatori) si facilita

la ricombinazione delle lacune generate termicamente, diminuendone il numero. Lo stesso

dicasi per gli elettroni se si aggiungono impurezze di tipo "p" (accettori).

Si pensi, ad esempio, che a 300K si ha ni =1010/cm3 per il Si mentre il numero di atomi in

un cm3 è 1022. Solo un atomo su 1012 fornisce cioè una coppia elettrone-lacuna.

Generazione e ricombinazione di cariche

In un semiconduttore instrinseco si ha:

p=n

Si tratta comunque di un equilibrio dinamico, nel senso che nell'unità di tempo e di volume

vengono generate termicamente "g" nuove coppie ed altrettante spariscono. Possiamo

definire perciò un tempo di vita medio di un elettrone (τn) o di una lacuna (τp) come

l'intervallo di esistenza medio prima della ricombinazione.

τn e τp sono fondamentali nella fisica dei dispositivi perché definiscono il tempo medio

necessario per un sistema di cariche per tornare in condizioni di equilibrio

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 11

PROPRIETA’ FISICHE DEI SEMICONDUTTORI (II)

Densità di carica in un semiconduttore

La legge di azione di massa np=ni2 fornisce una relazione tra le

cariche "libere" in un semiconduttore. Tali cariche sono legate però

anche dalla relazione di neutralità elettrica del materiale.

Chiamando perciò ND+ il numero dei donatori ionizzati e NA- quelli

degli accettori ionizzati, deve essere:

N D+ + p = N A− + n

In un semiconduttore di tipo "n" potremmo porre

Di conseguenza:

N A− ≅ 0

n ≅ ND

portatori di maggioranza

portatori di maggioranza

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

Eg

EFi

EA

Ev

banda di conduzione

ed assumere inoltre

p≅

p << n

ni2

ND

portatori di minoranza

ed analogamente in un semiconduttore "p"

p ≅ NA

Ec

ED

banda di conduzione

n≅

ni2

NA

portatori di minoranza

I / 12

PROPRIETA’ FISICHE DEI SEMICONDUTTORI (III)

Mobilità

Per effetto della temperatura il movimento delle cariche "libere" all'interno di un semiconduttore

è di tipo random.

Le cariche positive e negative infatti “urtano” continuamente gli ioni del reticolo e cambiano

direzione percorrendo in media distanze dell'ordine di Lp o Ln dette libero cammino medio.

Non c'è in questo caso spostamento netto di cariche attraverso una qualunque sezione.

In presenza di un campo elettrico però, il fenomeno cambia. Il campo "incanala" il movimento

delle cariche che vengono accelerate tra un urto ed il successivo.

Ne risulta uno spostamento netto delle cariche, in direzione opposta per elettroni e lacune, con

una velocità media che è proporzionale al campo.

Chiamiamo mobilità tale costante di proporzionalità:

vp = μ pE

vn = μ n E

lacune

elettroni

Conduttività

Se in un semiconduttore sono presenti in numero non trascurabile sia elettroni che lacune,

ricordando che la densità di corrente J è il numero di cariche che attraversa una sezione

nell'unità di tempo, avremo:

(

)

J = nμ n + pμ p qE = σE

Corrente di conduzione

essendo σ la conducibilità del semiconduttore.

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 13

PROPRIETA’ FISICHE DEI SEMICONDUTTORI (IV)

Effetto Hall

Se un campione di semiconduttore, percorso da una

corrente I, è posto in un campo magnetico trasversale

B, su di esso viene indotto un campo elettrico E in

direzione perpendicolare sia a I che a B.

Tale fenomeno, detto Effetto Hall, viene sfruttato per

determinare se un semiconduttore è di tipo p o n e per

trovare la concentrazione dei portatori.

Forze in gioco:

In condizioni di

equilibrio le due

forze si bilanciano

vH =

BI

nqw

r

r r

FH = − q B x v

qBv = qE

r

r

FE = − qE

Poiché

d

v

-

ovvero

μH

8

=

σRH

3π

-

-

+ + +

v

E= H

d

σ = nqμ

E+ E -

w

v

x

z

da cui, introducendo il coefficiente di Hall "RH"

Perciò se si procede alla misura della conduttività

μH = σRH

+-

y

-+

e

v=

RH =

J

I

=

nq wdnq

1

v w

= H

nq

BI

si ottiene:

Se si tiene conto del fatto che non tutte le

cariche si muovono con la stessa velocità

media v

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 14

PROPRIETA’ FISICHE DEI SEMICONDUTTORI (V)

p(0)

Diffusione

p(x)

Se in un semiconduttore è presente una non uniforme

distribuzione di cariche è ovvio ritenere che il numero di

cariche che attraversa la sezione x da sinistra a destra è

diverso da quello che la attraversa in direzione opposta.

Jp

Nell'esempio di figura in particolare si ha uno spostamento netto

di lacune da sinistra a destra, in direzione opposta al gradiente.

Ci sarà di conseguenza una corrente del tipo:

J p = − qD p

δp

δx

x=0

e analogamente per gli elettroni:

δn

J n = −qDn

δx

x

Essendo Dp e Dn le costanti di diffusione di lacune ed elettroni rispettivamente.

Si noti in particolare che essendo diffusione e mobilità fenomeni statistici dello stesso tipo,

Dp e µp non sono indipendenti ma relazionati secondo la:

Dp

μp

=

Dn

μn

= VT =

T

11600

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

relazione di Einstein

I / 15

PROPRIETA’ FISICHE DEI SEMICONDUTTORI (VI)

A

Legge della giunzione

La radiazione che incide in x=0 genera coppie

elettrone-lacuna in quantità tale da variare

apprezzabilmente solo la concentrazione delle

cariche di minoranza p.

Le cariche in eccesso diffondono nello spazio

x>0 ricombinandosi con gli elettroni, sicché la

loro concentrazione diminuisce con x tendendo

al valore di equilibrio p0 secondo l'equazione:

p ( x ) = p0 + p0' (0 )e

−

tipo “n”

n=ND

p(x)

p’o

x

Lp

po

x

0

Dove p’0(0) è l'eccesso di carica ad x=0 ed Lp è il già noto libero cammino medio delle lacune:

Lp =

D pτ p

Se in particolare la causa che "inietta" le cariche in eccesso alla sezione x=0 è una tensione V≠0,

si può assumere che la concentrazione pn(0) sia legata al valore di equilibrio p0 dalla relazione:

pn (0 ) = p0 e

V

VT

legge della giunzione

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 16

PROPRIETA’ FISICHE DEI SEMICONDUTTORI (VII)

Potenziale di Built-In

NA ND

a)

b)

x1

V21

x1

x2

V0

x2

In un semiconduttore in situazione di equilibrio, la corrente totale che attraversa una qualunque

sezione è nulla (Fig. a).

Se il drogaggio non è uniforme (Fig b) si ha però che la corrente di diffusione è diversa da zero.

Sarà perciò anche diversa da zero quella di conduzione in modo che sia nulla la corrente totale.

J tot , p = qpμ p E − qD p

dp

=0

dx

Ebi =

VT dp

dV

=−

p dx

dx

campo elettrico di built-in

e quindi integrando tra x1 ed x2 (fig. a) avremo:

V21 = V2 − V1 = VT ln

p1

p2

In questo caso si avrà in particolare:

nel caso di (fig. b) avremo:

V21 = VT ln

Per le lacune

ln

n2

p

= ln 1

n1

p2

V0 = VT ln

N AND

ni2

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

n2

n1

Per gli elettroni

n1 p1 = n2 p2

perchè

p1 ≅ N A

ni2

p2 ≅

ND

I / 17

GIUNZIONE DI DUE SEMICONDUTTORI (I)

Giunzione tipo p - tipo n

-+

-+

-+

-+

ρ

-

+

+

+

+

-+

-+

-+

-+

Diagramma schematico di una giunzione pn, comprendente la densità di carica,

l’intensità

del

campo

elettrico

e

l’andamento della differenza di potenziale

d 2V

dx

E

V

2

=−

E=−

ρ

ε

ρ

dV

= ∫ dx

ε

dx

V = − ∫ Edx

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

Equazione di Poisson

Campo Elettrico

Potenziale

I / 18

GIUNZIONE DI DUE SEMICONDUTTORI (II)

Potenziale di Contatto

Andamento dei diversi livelli di

energia in una giunzione p-n

Con riferimento alla figura si può scrivere che:

E0 = E1 + E2 =

(

1

1

EG − (ECn − EF ) + EG − EF − EVp

2

2

)

qφ p

Dove:

EG = kT ln

ECn

NC NV

ni2

NC

− EF = kT ln

ND

EF − EVp

N

= kT ln V

NA

np =

ni2

= NC NV

n = NC e

−

E

− G

e kT

ECp

( EC − E F )

ECn

E2

kT

E1

EVp

p = N Ae

−

qφn

( E F − EV )

xd

kT

Potenziale di contatto:

⎛ N AND ⎞

p p0

nn 0

⎜

⎟

ln

ln

E0 = kT ln

=

kT

=

kT

⎜ n2 ⎟

pn 0

n p0

i

⎝

⎠

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

xp

tipo p

xn

tipo n

[eV]

I / 19

EVn

GIUNZIONE DI DUE SEMICONDUTTORI (III)

Polarizzazione diretta

Polarizzando

direttamente

una

giunzione,

collegando cioè il polo positivo al lato p e quello

negativo al lato n, si produce un abbassamento

della tensione alla giunzione agevolando la

diffusione delle cariche attraverso la giunzione e

lasciando inalterata praticamente la corrente di drift

che in condizioni di equilibrio bilanciava quella di

diffusione.

Il risultato è il passaggio di una corrente diretta

che è funzione della tensione applicata.

Polarizzazione indiretta

Polarizzando inversamente una giunzione, collegando cioè il polo positivo al lato n e quello

negativo al lato p, si produce un innalzamento della tensione alla giunzione che rende più

difficile la diffusione delle cariche di maggioranza, ma lascia inalterato il flusso delle cariche

generate termicamente che attraversano la giunzione non più compensata dalla corrente di

diffusione.

Idealmente tale corrente, che è una corrente inversa, non dipende dalla tensione applicata

ma solo dalla temperatura T.

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 20

GIUNZIONE DI DUE SEMICONDUTTORI (IV)

Caratteristica I-V

I

I

[mA]

Legge matematica

⎞

⎛ V

⎟

⎜ ηVT

I = I0 ⎜ e

− 1⎟

⎟

⎜

⎠

⎝

⎧1 (silicio)

η=⎨

⎩2 (germanio)

I0

V

I

[μA]

V

Zoom polarizzazione indiretta

T

VT =

11600

Circuito equivalente

caratteristica

ideale

I

500

[mA]

I

[mA]

+

Ri

V

V

10

0

0.2

pendenza

1 Ri

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 21

°C

pendenza

1 (R R

f i)

-55

Vγ

25°C

D

150

°C

Rf

0.6

1.0 V

GIUNZIONE DI DUE SEMICONDUTTORI (V)

Tensione di soglia Vγ

Nella caratteristica I-V del diodo al Ge ed al Si, si nota l'esistenza di una tensione di soglia Vγ,

sotto la quale la corrente diretta è trascurabile (convenzionalmente 1% della corrente massima

che il diodo può sopportare).

Si ha in particolare Vγ-Ge≅0.2V, Vγ-Si≅0.6V. Il motivo della differenza è duplice:

1.

2.

I0 per il germanio è dell'ordine dei mA, per il silicio dell'ordine dei nA;

η per il silicio è 2, specie per bassi valori di tensione, e per il germanio è 1.

Caratteristica Logaritmica

Se V>>VT si ha

I ≅ I0 e

V

ηVT

se la tensione continua a crescere però il legame cambia perché comincia a farsi sentire la caduta

ohmica nel corpo del semiconduttore e la tensione sulla giunzione diviene diversa da quella

applicata ai morsetti.

Il risultato è che la caratteristica I-V diventa praticamente lineare.

Effetto della temperatura

La legge

⎞

⎛ V

⎟

⎜ ηVT

I = I0 ⎜ e

− 1⎟

⎟

⎜

⎠

⎝

contiene implicitamente T sia in I0 che in VT. Al variare della

temperatura cambiano entrambe in modo percentualmente

analogo sia per il Ge che per il Si.

Si ha che:

I0 raddoppia per ogni ΔT=10°C

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

ΔV

⎡ mV ⎤

= −2 . 5 ⎢

⎥

ΔT

⎣ °C ⎦

I / 22

GIUNZIONE DI DUE SEMICONDUTTORI (VI)

Linearizzazione a tratti (1)

Nel funzionamento per grandi segnali, è spesso sufficiente sostituire alla caratteristica I-V del

diodo, una sua linearizzazione a tratti, nella quale la caratteristica logaritmica viene sostituita

da relazioni lineari.

Il diodo reale è sostituito da un circuito equivalente nel quale compaiono le quantità:

• Interruttore on-off (diodo ideale)

• Tensione di innesco Vγ

• Resistenza diretta Rf Æ r

• Resistenza inversa Ri

dove Rf è la resistenza incrementale o dinamica del diodo e vale:

V

ηVT

1

1

dI

I e

= =g=

= 0

Rf

r

dV

ηVT

=

I + I0

ηVT

Rf = r ≅

ηVT

I

mentre Ri, che si calcola in modo analogo, tiene conto del fatto che nella realtà I0 è

funzione della tensione inversa.

Nella prossima slide vedremo come

cambia la caratteristica della giunzione

con queste assunzioni

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 23

SOMME GRAFICHE

Linearizzazione a tratti (2)

Nel piano delle caratteristiche i=f(v), le operazioni di “somma”

possono farsi a parità di corrente (elementi connessi in serie),

Ovvero a parità di tensione (elementi connessi in parallelo)

Combinando due resistenze,

di equazione

I

R1

R2

R

R1+ R2

V=R1I e V=R2I

avremo

V

V=(R1+R2)I

e

V=(R1//R2)I

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 24

GIUNZIONE DI DUE SEMICONDUTTORI (VII)

Linearizzazione a tratti (3)

Rf

D

Vγ

I

I

Vγ

Rf

+

V

Vγ

Ri

Circuito Equivalente

Tensione di soglia

V

Vγ

Resistenza dinamica

I

I

I

D

Ri

β

Vγ

V

Interruttore Ideale

V

Vγ

Resistenza Inversa

⎛1⎞

β = arctg⎜⎜ ⎟⎟

⎝ Ri ⎠

α

V

Risultato

⎛ 1 ⎞

⎛

⎟ ≅ arctg⎜ 1

⎜ R f // Ri ⎟

⎜ Rf

⎝

⎠

⎝

α = arctg⎜

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

⎞

⎟

⎟

⎠

I / 25

V

GIUNZIONE DI DUE SEMICONDUTTORI (VIII)

Capacità di Transizione

Quando una giunzione viene polarizzata inversamente si ha un allontanamento dalla

giunzione di portatori maggioritari, che lasciano un numero di cariche statiche non compensate

via via sempre maggiore. Tale aumento di carica non neutralizzata può essere vista come

una capacità incrementale detta appunto capacità di transizione.

+

d 2V

dx 2

p

n

= −q

Nd

ε

N

dV

= −q D (x − W ) = − E

dx

ε

V = −q

CT =

(

ND 2

x − 2W x

2ε

)

Vj = q

ND 2

W

2ε

dQ

dW

A

= qN D A

=ε

dVd

dV j

W

avendo posto:

Q = qN DWA

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

V j = V0 − Vd

I / 26

GIUNZIONE DI DUE SEMICONDUTTORI (IX)

Modello del controllo di carica

concentrazione

Nella figura a lato è riportata la

distribuzione dei portatori minoritari nelle

condizioni di polarizzazione diretta e

inversa.

Polarizzazione diretta: supponiamo per

semplicità che la corrente I che

attraversa la giunzione sia data dalle

sole lacune presenti nella zona n cioè

che la zona p sia molto più drogata della

zona n ed è quindi possibile trascurare

Polarizzazione diretta

polarizzazione inversa

la corrente dovuta agli elettroni minoritari

presenti nella zona p.

Ricordando la legge della giunzione che regola l’andamento dei portatori minoritari, è possibile

calcolare la carica Q dei portatori in eccesso nella regione n. Possiamo quindi scrivere che:

∞

−x Lp

A= area della sezione tratteggiata

Q = Aqp' (0)e

dx = AqL p p' (0)

q= carica dell’elettrone

0

dp AqD p

−x Lp

I p (x )

= AqD p

=

p' (0)e

x =0

dx

Lp

x =0

Tale espressione mostra come la corrente in

una giunzione sia proporzionale alla carica

Aq D p p ' (0 ) Q

L2p

τ=

I=

=

immagazzinata Q dei portatori minoritari in

Dp

Lp

τ

eccesso

∫

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 27

GIUNZIONE DI DUE SEMICONDUTTORI (X)

Capacità di diffusione

Si consideri il fenomeno di accumulo della carica iniettata

attraverso la giunzione in funzione del tempo, quando il

potenziale applicato subisce delle variazioni.

Una variazione incrementale di dV provocherà una variazione di

carica dQ nell’intervallo dt. A regime (dopo che siè ristabilito

l’equilibrio) tale variazione di carica corrisponde ad un valore di

capacità dato da:

CD =

dQ

dI

=τ

=

dV

dV

CD =

τI

ηVT

Capacità di diffusione statica

Quando la tensione applicata alla giunzione varia in modo continuo (quando per esempio si

applica un segnale sinusoidale), la variazione di carica che si crea dQ’ è tempo dipendente e

crea un flusso di corrente dato da:

dQ ' dQ

i=

≠

dt

dt

e quindi una capacità di

dQ

'

C

=

diffusione dinamica diversa

D

dV

da quella statica

1τ

⎧ '

=

C

per ωτ << 1

D

⎪⎪

2r

1/ 2

⎨

Se la tensione V varia sinusoidalmente

1

⎛ τ ⎞

'

⎪C D

=⎜

per ωτ << 1

⎟

⎪⎩

r

⎝ 2ω ⎠

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

'

≠ CD =

I / 28

dQ

dV

Università degli Studi di Roma Tor Vergata

Dipartimento di Ing. Elettronica

corso di

ELETTRONICA APPLICATA

Prof. Franco GIANNINI

IL DIODO

I / 29

DIODI (I)

Tempi di commutazione

vi (t)

i(t)

RL

Quando un diodo cambia stato, la risposta

elettrica presenta un transitorio ed il diodo

ritorna in uno stato stazionario solo dopo che è

trascorso un certo tempo.

Nella figura a fianco ( passaggio dallo stato di

conduzione diretta all’interdizione ) sono

riportati gli andamenti delle grandezze elettriche

presenti nel circuito, al variare del tempo

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 30

DIODI (I)

pn(0)

IF= VF /RL

ts

IF= - VF /RL

pn0

x

I0

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

all’istante ts

I / 31

DIODI (II)

Varactor

E’ un

diodo costruito in modo da esaltare il

comportamento da capacità variabile (CT) quando ai suoi

capi viene applicata una tensione tempo variante.

simbolo

25°C

3.2

2.4

1N914

1.6

Rr

1N916

0.8

Rs

Circuito equivalente

00

CT

5

10

15

20

25

Polarizzazione inversa [V]

Rr= resistenza in polarizzazione inversa

Rs= resistenza bulk del semiconduttore

CT= capacità in polarizzazione inversa

CT =

Capacità CT [pF]

4.0

εA

w

Tipico circuito

impiegante un

varactor

w = f (V ) ≡ V n

( )

CT = f V − n

n<1 (dipende dal drogaggio)

Dipende dalla tensione

inversa applicata

Ro

L

C1

CT

V

Pulsazione di risonanza del circuito

ϖ0 ≅

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

1

L ( C1 + C T )

Varia

con

la

tensione applicata

I / 32

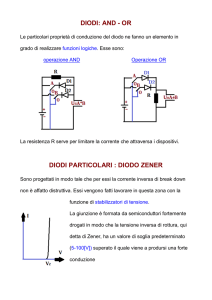

DIODI (III)

Diodo Zener

Diodo realizzato con caratteristiche di dissipazione di

potenza adeguate per funzionare nella regione di

breakdown. Viene impiegato come regolatore o

stabilizzatore di tensione.

A grandi variazioni di corrente corrispondono piccole variazioni di tensione

L’andamento brusco della corrente inversa è dovuto al verificarsi contemporaneo di due fenomeni:

l’effetto valanga e l’effetto Zener.

Effetto valanga: l’aumento della tensione inversa accelera gli elettroni che acquistano energia

sufficiente per ionizzare gli atomi del reticolo

dVZ

>0

dt

prevale sopra i 6V

Effetto Zener: l’aumento della tensione inversa può “estrarre”, spezzando il legame covalente, gli

elettroni dagli atomi del reticolo

dVZ

<0

dt

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

prevale sotto i 6V

I / 33

DIODO ZENER (Stabilizzatore di tensione)

Variando il carico e/o la tensione di alimentazione, entro

opportuni limiti, la tensione ai capi dello Zener varia poco

+

R//RL

+

vo

v’

-

-

V’Z

V’= VRL/(R+RL)

RL crescente

Variando il carico RL

la tensione ai capi dello Zener varia da VZ a V’Z

V’’Z

Variando la tensione V,

la tensione ai capi dello Zener varia da VZ a V’’Z

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

V’/R

I / 34

DIODI (IV)

Diodo Tunnel

Se si incrementa in modo significativo la concentrazione degli atomi di impurità, sino a circa 1

parte su 103 (corrispondente ad una densità di drogante superiore a 1019 cm-3) si riesce ad avere

una diminuzione sostanziale della zona svuotata della barriera (si passa da dimensioni

dell’ordine di un micron a circa 0.01 micron) ottenendo cosi un diodo dalla caratteristica I-V

completamente diversa.

I

IP

simbolo

VP= tensione di picco

VV= tensione di valle

VF= tensione diretta di picco

Circuito equivalente

IP= corrente di picco

IV= corrente di valle

IV

VP

VV

VF

V

Per tensioni inferiori a VP il diodo si comporta come una normale resistenza (dI/dV è positiva)

Per tensioni maggiori di VP la corrente diminuisce cioè dI/dV è negativa per cui il diodo Tunnel

presenta una resistenza negativa tra IP e IV

Per tensioni maggiori di VV la resistenza mostrata dal diodo ridiventa positiva.

Per correnti comprese tra IP e IV la curva si presenta a tre valori, poiché ogni valore di corrente può

essere ottenuto con tre differenti valori di tensione applicata. Questa caratteristica rende il diodo

Tunnel adatto alle applicazioni impulsive e digitali.

A RF può essere utilizzato come oscillatore e come amplificatore a riflessione.

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 35

DIODI (V)

Se una giunzione viene illuminata, vengono create delle coppie elettrone lacuna che vanno ad

alterare in modo sensibile le concentrazioni dei portatori di minoranza.

In condizioni di polarizzazione inversa (terzo quadrante) la corrente diventa Iinv = Is + Io

essendo Is il contributo dovuto all’illuminazione

Retta di carico

Inoltre, poiché i portatori utili ai fini dell’incremento di

corrente sono solo quelli che attraversano la giunzione,

l’efficienza dell’illuminazione è funzione della distanza dello

spot dalla giunzione stessa e della lunghezza di diffusione

Ln o Lp del portatore.

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 36

DIODI (V)cont.

Fotodiodo /Cella solare

II

Se la giunzione illuminata la si utilizza nel quarto quadrante, essendo

negativo il prodotto I V , si produce energia elettrica (cella solare).

RL

Fotodiodo

VF

IC

Is

V

Cella solare

Fotodiodo

I

I = Is + Io (1- exp( V/ ηVT))

Caratteristica del fotodiodo

IC ⇒ corrente di cortocircuito. E’ proporzionale

V

Pmax

Valori della

resistenza

RL

all’intensità dell’illuminazione

VF

⇒

potenziale

fotovoltaico.

Corrisponde

all’abbassamento del potenziale di contatto dovuto

alla creazione delle coppie elettrone–lacuna generate

dalla radiazione incidente.

⎛

Vmax = ηVT ln⎜⎜1 +

⎝

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

Is

Io

⎞

⎟⎟

⎠

nel silicio

VF ≅ 0.5 ÷ 0.6

I / 37

DIODI (VI)

Retta di carico

Dall’equazione di Kirchoff alla seguente maglia risulta:

+

vA

-

+

+

vi

-

i

vA = v i − R L i

che rappresenta la retta

di carico ai capi del

diodo

La retta di carico, insieme alla caratteristica del diodo

i = f (v )

individua il punto di lavoro “A” del dispositivo.

vo

RL

-

Nell’approssimazione di bassa frequenza,

implicita in quanto su posto, la retta di carico

è il luogo di tutti e soli i possibili punti

di lavoro del dispositivo.

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 38

DIODI (VII)

Curva dinamica, curva di trasferimento

Vo

Vo

V0= iRL

b

a

VoA

i

c

i

d e

ViA

h

t’

Vi

t

A

t’

B

E

F

f g

k

G

D

C

+

vA

-

+

H

+

I

J

vi

K

-

i

vo

RL

-

t

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 39

DIODI (VIII)

Linea di carico

L’equazione di Kirchoff applicata alla maglia è:

v

+

i=f(v)

i

Vi

Vi =v(i) +v’(i’) dove:

+

i’

i=f(v) v’

-

i = i'

i ' = f ( v' )

caratteristica di B

i = f ( v)

caratteristica di A

Si hanno 4 incognite i, i’, v, v’. Il sistema si può ridurre nel modo seguente:

v = Vi - v '

linea di carico di A

i=f(v)

caratteristica di A

Nel caso in cui A e B siano due diodi uguali

il punto di lavoro di A si individua

graficamente come nella figura a lato

iI

i = f ( v)

Q

Vi

v

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 40

DIODI (IX)

Linearizzazione a tratti

Rf

D

Vγ

+

iI

Circuito equivalente

Rf

Ri

Ri

Stato off

Ri

v

V٧

Rf

Vγ

+

Stato on

Caratteristica linearizzata

Esistono due possibili metodi di analisi:

Metodo degli stati

Si assume che ogni diodo presente nel

circuito sia in uno stato preciso (ON o OFF)

sostituendolo con il circuito equivalente

relativo allo stato scelto. Il circuito, reso

lineare, è esaminato con le leggi di Kirchkoff

verificando che siano corrette le assunzioni

iniziali e ripetendo l’analisi in caso di

assunzione non corretta (es. corrente

positiva in un diodo considerato OFF)

Metodo degli scatti

Si determinano i punti di scatto di ogni diodo nel

circuito imponendo la condizione id=0A e vd=v٧

( nel caso ideale id=0A e vd=0V ). Nel piano

della curva di trasferimento v0=f(vi) si riportano i

punti di scatto così individuati e si uniscono con

tratti di retta. I lati estremi della caratteristica

linearizzata si determinano calcolando la

pendenza delle semirette per i punti di scatto

estremi calcolate per vi<<0 e vi>>0 .

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 41

DIODI (X)

Circuiti limitatori ad un livello (clipper)

+

R

+

Diodo on

Diodo off

Vo

Vo

Slope=Rf /(Rf+R)

vo

vi

output

VR

-

VR +V٧

Condizioni di scatto:

t

Vi

R

VD= Vγ

Vo = VR + Vγ

ID= 0

Vi = Vo

Slope 1

Vi

input

t

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 42

DIODI (XI)

Circuiti limitatori ad un livello (clipper)

+

R

+

Diodo on

Vo

vo

vi

Diodo off

Vo

Slope 1

output

Slope=Rf /(Rf+R)

VR

-

t

Vi

VR -V٧

Condizioni di scatto:

VD= Vγ

Vo = VR - Vγ

ID= 0

Vi = Vo

Vi

input

N.B. Le condizioni di scatto

sono le stesse

t

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

N.B. VR determina solo

il livello del taglio

I / 43

DIODI (XII)

Circuiti limitatori ad un livello (clipper)

In questa slide vengono riportati alcuni ulteriori esempi di circuiti a diodi che possiedono la stessa

transcaratteristica dei precedenti ma in cui i diodi sono connessi sia in serie che in parallelo:

R

+

+

vo

vi

VR

-

Vo

input

+

+

R

vi

vo

VR

-

Vo

R

+

+

vo

vi

VR

-

-

+

+

R

vi

vo

VR

-

Vo

Vo

VR

t

t

t

t

output

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 44

DIODI (XIII)

Circuiti limitatori a due livelli (slicer)

D1 on, D2 off

R

+

+

vo

vi

VR1

D1 off, D2 on

Vo

output

VR2

D2

D1

Vo

D1 off

D2 off

Slope 1

VR1

VR2

-

-

VR2

t

Vi

VR1

Input vi

Output vo

Stato Diodi

vi≤ VR1

Vo=VR1

D1 on, D2 off

VR1 < vi< VR2

Vo=Vi

D1 off, D2 off

Vi ≥ VR2

Vo=VR2

D1 off, D2 on

Vi

input

t

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 45

DIODI (XIV)

Circuito campionatore I

Circuito formato da un ponte di diodi la cui funzione è quella di fornire in uscita l’esatta replica del

segnale d’ingresso nell’intervallo di campionamento.

+

VC

vo

RL

D1

RC

P3

+vC

D2

-Vn

RC

P2

P4

P1

D3

TC

-vC

Tn

t

Vi

D4

input

vs

t

Vo

output

Fuori dell’ intervallo di campionamento

l’uscita è nulla (caso ideale).

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

t

I / 46

DIODI (XV)

Circuito campionatore II

L’analisi del circuito può essere effettuata applicando il teorema della sovrapposizione degli effetti

(possibile solo nei circuiti lineari, applicabile solo se i diodi non cambiano stato)

Condizioni di funzionamento:

VC

2R C

VC

2R C

+vC

1.

Intervallo di campionamento TC: tutti i

diodi

devono

essere

polarizzati

direttamente. Dall’analisi delle correnti

questo si verifica solo se

Vs

V

V

+ s ≤ C

RC 2 R L 2 RC

RC

RC

P3

P4

VC

RC

P1

P2

Vs

2R L

RC

VC

RC

VC

2R C

VC

2R C

⎛

R ⎞

VC ≥ Vs ⎜⎜ 2 + C ⎟⎟

RL ⎠

⎝

Vs

RL

Vs= 0

Vs

2R L

RL

P3

RC

P4

vs

Vs

RC

Vs

V

+ s

R C 2R L

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

RL

Vs

V

+ s

R C 2R L

P1

Vs

RC

Vc= 0

I / 47

-vC

DIODI (XV)2

Circuito campionatore III

2.

Intervallo Tn: tutti i diodi devono essere

aperti. Questo si verifica facilmente per

D1, D2, D3 per D4 quando:

+

V s ≤ Vn

D1

Questa condizione, con la precedente

RC

⎛

RC ⎞

⎟⎟

VC ≥ Vs ⎜⎜ 2 +

RL ⎠

⎝

vo

RL

-vn

consente di dimensionare il segnale di controllo.

P3

D3

D2

RC

P2

P4

P1

D4

+vn

vs

N.B. Il circuito campionatore realizza una “porta” che agisce sull’asse delle

ascisse (tempo).

Lo “slicer” realizza una “porta” che agisce sull’asse delle ordinate (ampiezza).

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 48

DIODI (XVI)

Circuito raddrizzatore a una semionda

Il raddrizzatore a una semionda è un caso particolare di clipper con VR=0. Analizzando il circuito

reale, ponendo però Ri=∞, si hanno lo schema e la risposta elettrica seguente:

Circuito

Caratteristica

Circuito equivalente

Vm sin α − Vγ

i=

R f + RL

⎛ Vγ

φ = arcsin⎜⎜

⎝ Vm

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

⎞

⎟

⎟

⎠

(da

i = 0)

I / 49

DIODI (XVII)

Circuito raddrizzatore a doppia semionda

Si può pensare a questo circuito come all’insieme di due raddrizzatori a una semionda, connessi

in modo che la corrente scorra nel carico attraverso un diodo durante mezzo ciclo della tensione

di rete e attraverso l’altro diodo durante l’altro mezzo ciclo.

Circuito

1

I dc =

2π

Im =

2π

∫

0

Vm

2I

sin α dα = m

π

R f + RL

Vm

R f + RL

Vdc = I dc R L =

2I m

π

RL

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 50

DIODI (XVIII)

Gli strumenti di misura in alternata sfruttano spesso dei circuiti raddrizzatori al loro interno,

invece che degli effettivi misuratori di valore efficace. In questi casi è utile definire una

grandezza che tenga conto del fatto che la tensione in continua fornita da un raddrizzatore è

funzione della corrente in continua che viene ceduta al carico RL.

Equivalente di Thevenin di un raddrizzatore

La tensione utile in uscita è ovviamente la tensione Vdc che

nel caso di raddrizzatore a doppia semionda è pari a:

2I

Vdc = I dc RL = m RL

π

dove Im=Vm/(RL+Rf)

il parametro regolazione viene definito come:

V

− V RL

% regolazione = RL=∞

x100%

V RL

VRL= caso reale (resistenza di carico finita)

VRL=∞= caso ideale ( resistenza di carico infinita)

Vdc= 2 ImRL/ π + 2 ImRf / π - 2 ImRf / π

Vdc= 2 Vm / π - IdcRf

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 51

DIODI (IV)

Raddrizzatore con filtro capacitivo

Il condensatore accumula energia durante il periodo di conduzione del diodo e la cede al carico

durante l’intervallo in cui il diodo non conduce.

Con ciò si diminuisce il ripple, cioè la deviazione della tensione di uscita dal suo valore medio.

Periodo di conduzione (t0-t1)

v

dv

i= 0 +C 0

RL

dt

v0 = vi = Vm sin (ωt )

e quindi:

i = I m sin (ωt + ψ )

L’istante t1 in cui il diodo si apre è quello in cui i=0 cioè

I m = Vm

sin(ωt1 + ψ ) = 0

Periodo di non conduzione (t1-t2)

Nell’intervallo t1-t2 il diodo non conduce. Assumendo Rf=∞ avremo:

1

R L2

+ ω 2C 2

ψ = arctan(ωCRL )

ω t1 = π − ψ

v0 = (Vm sin (ωt1 ))e

−

t'

RLC

t ' = t − t1

Nuovo periodo di conduzione (t2-t3)

Inizia quando

Vm sin (ωt 2 ) = (Vm sin (ωt1 ))e

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

−

t 2−t1

RLC

I / 52

DIODI (IV)

Analisi approssimata del raddrizzatore a doppia semionda con filtro capacitivo

Il circuito si ottiene inserendo nel circuito sottostante un condensatore C tra i nodi A e B, cioè in

parallelo alla resistenza RL:

Se

ωCR L >> 1

ωt1 →

π

2

v 0 → Vm

per t=t1

inoltre l’andamento esponenziale può essere approssimato linearmente. Si avrà perciò:

V

Vdc = Vm − r

2

e quindi, per l'approssimazione lineare

I T

Vr = dc 2

C

Migliore è l'effetto del filtro, minore è l'intervallo di conduzione (se diminuisce T1 aumenta la corrente

T

1

T

sarà: T2 = =

di picco nel diodo nell’intervallo di conduzione) T1=t0-t1. Perciò per T2 →

2 2f

2

In conclusione

I

Vdc = Vm − dc

4 fC

che corrisponde

all'equivalente di

Thevenin

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 53

DIODI (IV)

Rivelatore di picco

Il raddrizzatore ad una semionda con filtro capacitivo, può essere impiegato per misurare, o

rivelare, il valore di picco di una tensione qualsiasi.

vi (t ) = Vm (1 + m sin (Ωt )) sin (ωt )

m rappresenta l’indice di modulazione

La costante di tempo ottima, τ0, si trova imponendo che a t=t0 la pendenza dell’inviluppo sia

minore (scenda più lentamente) dell’esponenziale dovuto al gruppo RC

t −t 0

−

Vm

dv 2 (t )

(1 + m sin (Ω t 0 ))e τ

=−

τ

dt t = t 0

cioè

⎛ 1 + m sin (Ωt

<

t =t 0

dv 2 (t )

= mΩVm cos(Ωt 0 )

dt t =t 0

)⎞

0 ⎟

τ 0 < −⎜⎜

⎟

⎝ mΩ cos(Ωt 0 ) ⎠ min

e, derivando rispetto a t0

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

1 1 − m2

τ0 <

Ω

m

I / 54

DIODI (IV)

Circuito agganciatore (clamper) o DC restorer

Per una forma d’onda periodica si può richiedere di agganciare il valore estremo ricorrente,

positivo o negativo, ad un livello di riferimento costante VR , con un circuito del tipo seguente:

VC

Se RC>>T ed il diodo è ideale

Vc=(Vm – VR)

Vo= Vi - Vc= Vmsin(ωt) – (Vm – VR)

Il segnale d’uscita è agganciato al valore di riferimento VR e presenta un livello medio diverso da zero.

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 55

Università degli Studi di Roma Tor Vergata

Dipartimento di Ing. Elettronica

corso di

ELETTRONICA APPLICATA

Prof. Franco GIANNINI

IL BJT

I / 56

TRANSISTOR (I)

Transistore a giunzione (BJT)

Un transistor a giunzione è costituito dall’unione di due giunzioni n-p-n o p-n-p

Base

Emettitore

E

P

N

JE

IE

+

vEB

-

Collettore

B

C

P

JC

- vCE +

IB

Base

Emettitore

Il verso delle correnti è

assunto per convenzione

sempre entrante

E

N

P

JE

IE

IC

Collettore

B

JC

- vCE +

+

vCB

+

vEB

-

-

C

N

IC

+

vCB

IB

-

Gli andamenti delle figure sottostanti sono relativi al caso di struttura completamente

simmetrica in cui si è trascurata l’estensione delle zone di transizione. Inoltre di solito la base è

meno drogata dell’emettitore e del collettore

Potenziale, V

Concen trazione

portatori minoritari

+

Vo

JE

emettitore

tipo-p

base

tipo-n

JC

collettore

tipo-p

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

JE

emettitore

tipo-p

-

base

tipo-n

JC

collettore

tipo-p

I / 57

TRANSISTOR (II)

Tecnologie costruttive dei transistori di tipo discreto

Tipo di realizzazione per crescita

•

Il monocristallo viene estratto da un crogiuolo contenente il semiconduttore fuso. Durante

l’operazione vengono aggiunte impurezze di tipo diverso realizzando le varie zone

Tipo di realizzazione per lega

•

Sulle due facce di una barretta di semiconduttore (n-Ge per esempio) vengono poste due

sferette di Indio che ad alta temperatura si sciolgono nella barretta. Durante il raffreddamento

le zone in cui si sono sciolte ricristallizzano drogandosi p

Tipo di realizzazione planare

•

In un substrato semiconduttore, attraverso finestre realizzate con metodi fotolitografici, viene

fatto diffondere il drogante che realizza prima la base e poi l’emettitore. Il metallo infine

realizza i contatti ohmici

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 58

TRANSISTOR (III)

Transistore in zona di funzionamento attivo

iE

E

C

iC

IE

B

vCB

VEB

RL

vL

Pn

VCC

np

La giunzione base–emettitore è polarizzata

direttamente: la barriera diminuisce di |VEB|

np

Pn0

np0

La giunzione base–collettore è polarizzata

inversamente: la barriera aumenta di |VCB|

np0

α IE

WB

In base alla legge della giunzione, si ha per le cariche

di minoranza:

V EB

n p ( J E ) = n p 0 e VT

Vo

|VEB|

V EB

>> n p 0

n p ( J E ) = n p 0 e VT

>> n p 0

|VCB|

per quanto riguarda le lacune nella base si assume

ugualmente:

V EB

p n ( J E ) = p n0 e

VT

>> p n0

p n ( J C ) = p n0 e

−

VCB

VT

<< p n0

p-type

Emettitore

JE

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

p-type

Collettore

n-type

Base

JC

I / 59

TRANSISTOR (IV)

Correnti nel BJT (I)

JE

JC

p

IE

n

p

IpC1

IpE

IpE-IpC1

IC

IpC0

InE

IC0

InC0

IB

+

+

VEB

VBC

Corrente di emettitore

I E = I pE + I nE = I pn (0) + I np (0)

Corrente di collettore

I C = I C 0 − I pC1 = I C 0 − I pn w + = I C 0 − αI E

( )

Tale approssimazione per la corrente di collettore è valida solo in zona attiva,

(IC praticamente indipendente dalla tensione di collettore)

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 60

TRANSISTOR (V)

Correnti nel BJT (II)

Le correnti nelle diverse sezioni possono scriversi come:

( )

( )

JE

I pn w + = δI pn w −

n

IpE

IE

I pn (0) = γI E

IpE-IpC1

( )

IB

+

I −I

α = − C C0

IE

γ =

Vc

⎛

⎞

Vt ⎟

⎜

I C = −αI E + I CO ⎜1 − e ⎟

⎝

⎠

I pn (o)

I pn (o) + I np (o)

rendimento di base

VBC

rendimento di collettore

I pn ( w−)

β *=

I pn (o)

δ =

I pn ( w+ )

I pn ( w−)

Equazione delle corrente IC generalizzata

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

p

+

VEB

rendimento di

emettitore

IC

IC0

InC0

p

I pC1 = γ β*δ IE = α IE

IpC1

IpC0

InE

I pn w − = β * I pn (0 )

fattore di amplificazione

in corrente per grandi

segnali

JC

I / 61

TRANSISTOR (VI)

Connessione base comune

B

vCB

RL

vL

-10V<

VEB

VCC

IC (mA)

0.4 0.5 0.6 0.7

Regione

interdetta

VEB (V)

Caratteristiche di ingresso

Regione

attiva

Regione di

saturazione

tore a

p

VCB <-1

V

C

E

erto

IE(mA)

iC

Collet

iE

VCB (V)

Caratteristiche di uscita

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 62

Università degli Studi di Roma Tor Vergata

Dipartimento di Ing. Elettronica

corso di

ELETTRONICA APPLICATA

Prof. Franco GIANNINI

CONFIGURAZIONI

CIRCUITALI E LORO

CONFIGURAZIONI

I / 63

SOMMARIO

La connessione ad emettitore comune

Le zone di saturazione ed interdizione

I parametri da cui dipende l’hFE

La curva di trasferimento

Equazioni i Ebers-Moll

Espressioni analitiche

Moltiplicazione per valanga

Reach trough

Fototransistore

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 64

Connessione emettitore comune

I

+VCC

Dalla

I C = −αI E + I C 0

e dalla

I E = −(I C + I B )

si ottiene

RL

I

αI

I C = C 0 + B = I CE 0 + βI B

1−α 1−α

I CE 0 = (1 + β )I C 0

I C − I CE 0

IB

B

VBE

dove

β=

C

→

→

IC

VCE

E

IE

Corrente di saturazione inversa con base aperta

Fattore di amplificazione in corrente per grandi segnali

per la connessione ad emettitore comune

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 65

Connessione emettitore comune

II

Guadagno in corrente per la connessione ad emettitore comune :

Abbiamo definito

e inserito nella relazione

da cui

β=

α

1−α

I C = (1 + β )I CB 0 + βI B

(1)

I C − I CB0

β=

I B − (− I CB0 )

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 66

Connessione emettitore comune

III

Poiché in interdizione valgono le relazioni :

IE = 0

I C = − I B = I CB 0

β rappresenta il rapporto tra l’incremento di IB e IC a partire dall’interdizione ed è perciò

il guadagno di corrente per grandi segnali della connessione emettitore comune.

In modo del tutto analogo possiamo definire, come guadagno di corrente in

continua, la quantità :

β dc = hFE =

IC

IB

e guadagno di corrente per piccoli segnali :

∂I C

β =

= h fe

∂I B V =cos t

CE

'

Che in base alla (1), diventa :

∂β

β = β + (I CB 0 + I B )

∂I B

'

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 67

Connessione emettitore comune

Infine imponendo

h fe = β '

h fe =

e

β ≅ hFE

IV

si ottiene :

hFE

1 − (I CB 0 + I B )

∂hFE

∂I C

h fe

h FE

1

IC

Relazione che lega il guadagno a piccolo segnale

hfe al guadagno in continua hFE.

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 68

Emettitore comune: zona di saturazione

I

Ic[mA]

200μ

200μA

VCC

RL

rsat

160μ

160μA

120μ

120μA

rsat≈nΩ

80μ

80μA

20

40μ

40μA

10

20μ

20μA

0

0.1

0.2

0.3

VCE

0.5

Vce[v]

In saturazione sia la giunzione di emettitore che di collettore sono polarizzate

direttamente. In questa situazione, aumentando la corrente di base, la corrente di

collettore rimane praticamente costante e vale:

I Csat ≅

V CC

RL

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 69

Emettitore comune: zona di saturazione

II

+VCC

V[v]

0.8

Ic/IB=10

Tj=25°

=25°C

R1

Vbesat

0.4

0.2

V1

Vcesat

0

RL

VBC

0.6

5

10

20

50

100

VCE

VBE

IE

Ic[mA]

VCE = VBE - VBC

La tensione di saturazione è funzione di IC e di IB. Poiché è la differenza di due tensioni ai

capi di due diodi in conduzione ed è ovviamente inferiore a ciascuna delle due.

N.B. La tensione Vbesat è circa uguale alla Vcbsat nel base comune.

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 70

Dipendenza di hFE con T, VCE, IC

N.B.

I Csat

VCC

I Bsat =

≅

hFE

hFE R L

La variazione di hFE con VCE è dovuta all’effetto Early.

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 71

Emettitore comune: zona di interdizione

I

La condizione di interdizione, per definizione, è quella per cui

IE=0

Per cui si ha

IE=0

→

IC=IC0

IC= - αIE+ ICO

Ne segue che, se si lascia aperta la base (IB=0), il transistor ad emettitore comune

non è in interdizione. Si ha infatti:

IB=0

→

I

I C = C 0 = I CE 0

1−α

Per avere l’interdizione è necessario introdurre una opportuna controtensione

tra base ed emettitore (V≅0.1V per Ge, V≅0 per Si), per annullare la corrente

di emettitore

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 72

Emettitore comune: zona di interdizione

II

+VCC

Nelle condizioni indicate (IE=0)

I B = − I CB 0

Inoltre, poiché si deve avere VBE ≅0.1V, sarà:

V1 ≅ − R1 I CB 0 − 0.1

R1

V1

ICB0

VBE

RL

IE=0

Quanto a ICB0, è in genere diversa da IC0 per due motivi:

1.

Per effetto della VCE (si hanno infatti fenomeni di moltiplicazione nello strato svuotato

base-collettore).

2.

Per effetto della corrente di leakage.

Si noti inoltre che ICB0 è molto diversa da transistore a transistore e varia inoltre con la

temperatura. Ciò comporta seri problemi se la V1 è stata scelta in corrispondenza ad alti

valori di ICB0. Una sua riduzione aumenta VBE e può portare in breakdown il diodo baseemettitore (βVBE0≅1V).

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 73

Curva di trasferimento IC-VBE per l’emettitore comune I

I C = I CES ≅ I C 0

I C = I CE 0 ≅ I C 0

-0,1

Cutoff

Interdizione:

0 0,06

Vγ =0,5

Open-circuit

base

IE = 0 → IC = ICO

Active

region

Vσ =0,8

Saturation

quando VBE ≅ 0 volt

Ciò perché a bassi livelli di corrente α→0 per effetto della ricombinazione

nello strato svuotato

Base cortocircuitata:

VBE = 0 → IC = ICES

Che è dello stesso ordine di grandezza di IC0

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 74

Curva di trasferimento IC-VBE per l’emettitore comune II

Base aperta:

IB = 0 → IC = ICEO

Che è ancora dello stesso ordine di IC0 perché α→0

I CE 0 =

IC

≅ IC0

1−α

Si ha inoltre che VBE è “leggermente positivo”

Tensione di innesco Vγ:

Il transistore entra in zona attiva quando la corrente di collettore raggiunge un

valore di riferimento (ad esempio ICγ ≅0.01 ICsat), che è dello stesso ordine di

grandezza di IC0

Tensione di saturazione Vσ:

Il transistore entra in saturazione ad un valore di VBE che dipende dal tipo di

costruzione del componente e dalla retta di carico. In linea di massima vale ≅0.8

volt per il silicio.

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 75

Curva di trasferimento IC-VBE per l’emettitore comune III

Ic[μA]

40

IB=> 0

RL

IB= 0

ICE0

20

IB= IBR

ICER

IB= IBS

ICES

IB= -ICB0

ICB0

0.1

0.2

0.3

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

Vcc

Vce[v]

I / 76

Curva di trasferimento IC-VBE per l’emettitore comune IV

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 77

Curva di trasferimento IC VBE per l’emettitore comune V

IB

Correnti di base corrispondenti

alle diverse definizioni di

interdizione

V°BE

IB=0

IBR

V’BE

D

B

A

IB= -ICB0

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

VBE

V’’BE

IBS

I / 78

Equazioni di Ebers-Moll

I

- VCE +

+ VE -

E

IE

Emitter

junction

- VC +

B'

rbb'

IB

Collector

junction

C

IC

- VCB +

+ VEB -

B

La dipendenza delle correnti IC ed IE in un transistore dalle tensioni di giunzione sono, per le

correnti di collettore :

⎞

⎛ Vc

I C = −α N I E − I CO ⎜⎜ e Vt − 1⎟⎟

⎠

⎝

E analogamente per la corrente IE :

⎛ Ve

⎞

I E = −α I I C − I EO ⎜⎜ e Vt − 1⎟⎟

⎝

⎠

Dove ll pedice “I” del termine α, sta per modo di funzionamento inverso ed “N” per modo di

funzionamento normale.

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 79

Equazioni di Ebers-Moll

II

Si dimostra inoltre che i quattro parametri αI αN ICO IEO presenti nelle due formule non

sono indipendenti, ma vale la relazione seguente che ne lascia liberi solo tre su quattro:

α I I CO = α N I EO

Si noti infine che il calcolo di VC ed VE a partire da VCB e VEB comporta la conoscenza almeno

della caduta sulla resistenza rbb’ detta resistenza di spreading di base, essendo le tensioni

sulla giunzione diverse dalle tensioni “esterne”, a causa della caduta nel corpo del

semiconduttore.

N.B. La resistenza rbb’ è “aggiunta” al modello monodimensionale usato fino ad ora per tener

conto del movimento “trasversale” delle cariche che escono o entrano dal contatto di base in

seguito ai fenomeni di ricombinazione delle cariche in viaggio dall’emettitore al collettore.

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 80

Equazioni di Ebers-Moll

III

α1IC

αNIE

IE

IC

N

P

I'

N

(-IE0)

VE

(-IC0)

IB

I

P

VC

Circuito equivalente di Ebers-Moll

E’ l’interpretazione in termini circuitali delle equazioni di Ebers-Moll e consente in particolare

una semplice interpretazione della dinamica del transistore. Se α1 = αN = 0, infatti, lo schema

si riduce a due diodi “punta a punta” non interagenti e non si ha l’”effetto transistore”.

Perché αI e αN risultino diversi da zero è necessario che le cariche iniettate dal diodo di

emettitore “diffondano” attraverso il secondo diodo. Ciò è possibile se la distanza fra le due

giunzioni è inferiore alla lunghezza di diffusione delle cariche nel semiconduttore che funge da

base e, in questo caso, da “catodo” per i due diodi.

Si noti altresì che nel modello non è compresa la rbb’ . Il modello è, come si è detto,

“monodimensionale” e non può quindi portare alla definizione di effetti legati a movimenti di

cariche in direzione normale a quella presa in esame (modello monodimensionale).

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 81

Espressione analitica delle carat. di out a emettitore comune

I

IC/IB

0.9 β

β=100

0.1

V T ln

1

α1

0.2

0.3

0.4

0.5

-VCE,V

0.006

Le equazioni di Ebers-Moll possono risolversi per VC e VE. Si ha :

⎛ I E + α I IC

VE = VT ln⎜⎜1 −

I EO

⎝

⎞

⎟⎟

⎠

⎛ IC + α N I E

VC = VT ln⎜⎜1 −

I CO

⎝

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 82

⎞

⎟⎟

⎠

Espressione analitica delle carat. di out a emettitore comune

Ricordando ora che

I B = −(I E + I C )

I B >> I EO

e ponendo

VCE

Dove

II

,

I B >>

I CO

αN

→ avremo :

1 IC

⎛ 1

+

⎜

αI βI IB

⎜

= VC − V E ≅ ±VT ln

⎜

IC

1

β

−

⎜

N

IB

⎝

α

βI = I

1 − αI

⎞

⎟

⎟

⎟

⎟

⎠

αN

βN =

1 − αN

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 83

Espressione analitica delle carat. di out a emettitore comune III

In particolare se IC=0 allora :

'

CE

V

⎛ 1

= ±VT ln⎜⎜

⎝αI

⎞

⎟⎟

⎠

Inoltre, poiché αN> αI , se il transistore è fatto funzionare al contrario,

ovvero scambiando i ruoli tra emettitore e collettore :

''

CE

V

⎛ 1

= ±VT ln⎜⎜

⎝αN

⎞

'

⎟⎟ < VCE

⎠

Questo risultato è utilissimo nei circuiti digitali potendosi così ridurre

ulteriormente la tensione residua in saturazione.

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 84

I

Moltiplicazione per valanga

α

1

VCE

BVCE0 BVCB0

Aumentando la tensione di collettore, le cariche accelerate nello strato svuotato possono

raggiungere una velocità tale da generare per urto nuovi portatori (δ>1). Ciò porta ad un

aumento di α e quindi della corrente di collettore.

La tensione a cui il fenomeno si verifica, tensione di breakdown (BV), è diversa a seconda

del tipo di connessione. A base comune è necessario avere α→∞ . A emettitore comune

basta che sia α = 1, il che comporta β→∞.

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 85

II

Moltiplicazione per valanga

Analiticamente di ha :

BVCEO = BVCBO n

1

hFE

Si noti inoltre che se la base non è aperta, la tensione di breakdown è maggiore di BVCE0

ma sempre inferiore a BVCB0. Ciò porta a caratteristiche IC, VCE con tratti a R<0

(es. il caso di IB=ICER indicato in figura )

Ic[mA]

IB=40μ

=40μA

30

3

R<0

20

2

10

1

<0

10

20

30

40

50

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

Vce[v]

I / 86

Reach Through

Quando la tensione VCB aumenta, lo strato svuotato penetra sempre più profondamente nella

base, raggiungendo, se la base è molto sottile, lo strato svuotato della giunzione di emettitore.

V

In questo caso la corrente può aumentare tanto

da superare la corrente massima ammessa

WB

V0

V'

|VEB|

dal dispositivo. Si noti che il punch-through

(o reach-through) avviene sempre allo stesso

valore di tensione tra base e collettore ed è

|VCB|

quindi indipendente dalla configurazione

circuitale (in ciò si differenzia dal breakdown).

La tensione massima che un transistore non

deve superare è ovviamente la minore tra quella

di breakdown e quella di punch-through.

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

JE

W

JC

I / 87

Fototransistore

C

IC

IC

IL>

n

Radiation

6

JC

VCE

JE

n

4

2

E

10

20

30

40

50

60

VCE

Il fototransistore è generalmente montato ad emettitore comune con base aperta (IB=0).

In queste condizioni, al buio, la corrente di collettore vale:

I C = (β + 1)I CO =

I CO

= I CEO

1−α

Con un notevole incremento rispetto all’analogo fenomeno nel fotodiodo, dovuto al fattore di

moltiplicazione (β+1) .

Ovviamente se IB ≠0 la corrente IC deve aumentare del termine βIB. Sarà perciò

I C = βI B + (β + 1)(I CO + I L )

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 88

Università degli Studi di Roma Tor Vergata

Dipartimento di Ing. Elettronica

corso di

ELETTRONICA APPLICATA

Prof. Franco GIANNINI

I FET

I / 89

SOMMARIO

Le caratteristiche dei FET

La tensione di pinch-off

MOSFET

MOSFET ad enhancement

Espressioni analitiche dei MOSFET

MOSFET a canale “n” di tipo depletion

Processi e “trend” tecnologici

FET con carico saturato e non saturato

NMOS enhancement con carico di tipo depletion

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 90

Caratteristica del FET

Il transistore ad effetto di campo è un dispositivo in cui l’azione di controllo è

effettuata dal campo elettrico.

Ne esaminiamo due tipi:

z

JFET

(transistore a effetto di campo a giunzione)

z

MOSFET

(transistore ad effetto di campo del tipo metallo-ossido-semiconduttore)

Il FET differisce dal BJT per i seguenti aspetti:

1.

Il FET è unipolare. Per il suo funzionamento necessita di un solo tipo di cariche

(elettroni o lacune)

2.

Occupa meno spazio e consente livelli di integrazione più elevati

3.

Può essere utilizzato come carico resistivo (carico attivo), realizzando circuiti di soli

FET e quindi molto compatti

4.

Presenta altissima resistenza di ingresso e consente quindi alti fanout (numero di porte

pilotabili in parallelo contemporaneamente da un solo FET)

5.

Funziona come interruttore bilaterale

6.

Può funzionare come elemento di memoria dinamica, sfruttando la piccola carica

interna che è in grado di immagazzinare

7.

E’ meno “rumoroso”

8.

Non presenta tensioni di offset in corrispondenza a corrente di drain nulla

Il principale svantaggio è il suo relativamente basso prodotto banda per guadagno.

In altre parole il BJT opera a frequenze generalmente più elevate del MOSFET (ma

non della versione ad alta frequenza di quest’ultimo realizzato con GaAs e del tipo

MESFET, FET a giunzione metallo-semiconduttore).

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 91

Transistore ad effetto di campo (tipo JFET)

Applicando solo una tensione negativa

alla porta “G” si polarizza inversamente

la giunzione p+- n, restringendo il canale

a disposizione delle cariche

-VGS

G

n

S

2a

2b(x)

-VGS

D

VDS =0

G

VD

Applicando una tensione VDS≠0 e positiva, scorrerà

una corrente ID che varierà punto-punto la tensione

0

x

VJ (x)

effettiva applicata alla giunzione p+-n e di

VGS

conseguenza il profilo dello strato svuotato.

VG

Fissato VGS quindi è evidente che esisterà un valore

S

D

di VDS che “strozza” il canale ed, in teoria, annulla b(x).

E’ altresì evidente che questo evento non è reale perché o si annulla la corrente ID e quindi

cessa la causa che ha provocato il restringimento oppure la densità di corrente, nel punto di

strozzamento va all’infinito: ipotesi entrambe non fisiche.

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 92

Tensione di pinch-off

I

La tensione Vp di pinch-off è quella tensione di drain (VDS ) che annulla (praticamente) la

larghezza del canale per un dato valore di VGS e, analogamente, la tensione di gate (VGS ) che

annulla il canale per VDS=0.

Sarà perciò, a partire da :

2ε

[Vo − V (x )]

eN D

2W (x ) = 2[a − b( x )] =

V0

(tensione di Built-in)

Nell’ipotesi ID=0 e V0<<V(x)=cost , che la tensione di pinch-off è quella per cui b(x)=b=0 cioè :

V p = (2a )

2

eN D

2ε

Risulta così per 2b(x) l’espressione :

⎡

V

2b = 2a ⎢1 − GS

Vp

⎢⎣

⎤

⎥

⎥⎦

A cura del Prof. F. Giannini, R. Giofrè, M. Imbimbo, P. Longhi, A. Nanni, A. Ticconi

I / 93

Tensione di pinch-off

II

Analizziamo ora due situazioni una relativa al comportamento del FET prima del pinch-off

(VDS<VP ) e una dopo il pinch-off (VDS>VP).

VDS<VP