DIAGRAMMI TEMPORALI DEI LATCH CON CIRCUITLAB

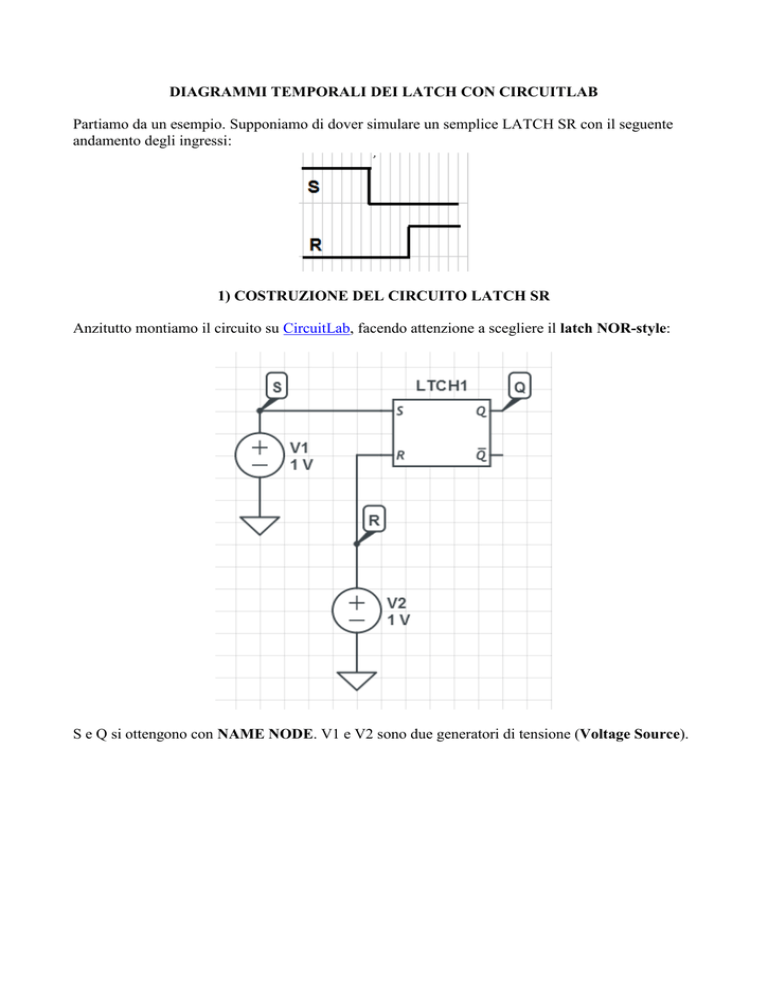

Partiamo da un esempio. Supponiamo di dover simulare un semplice LATCH SR con il seguente

andamento degli ingressi:

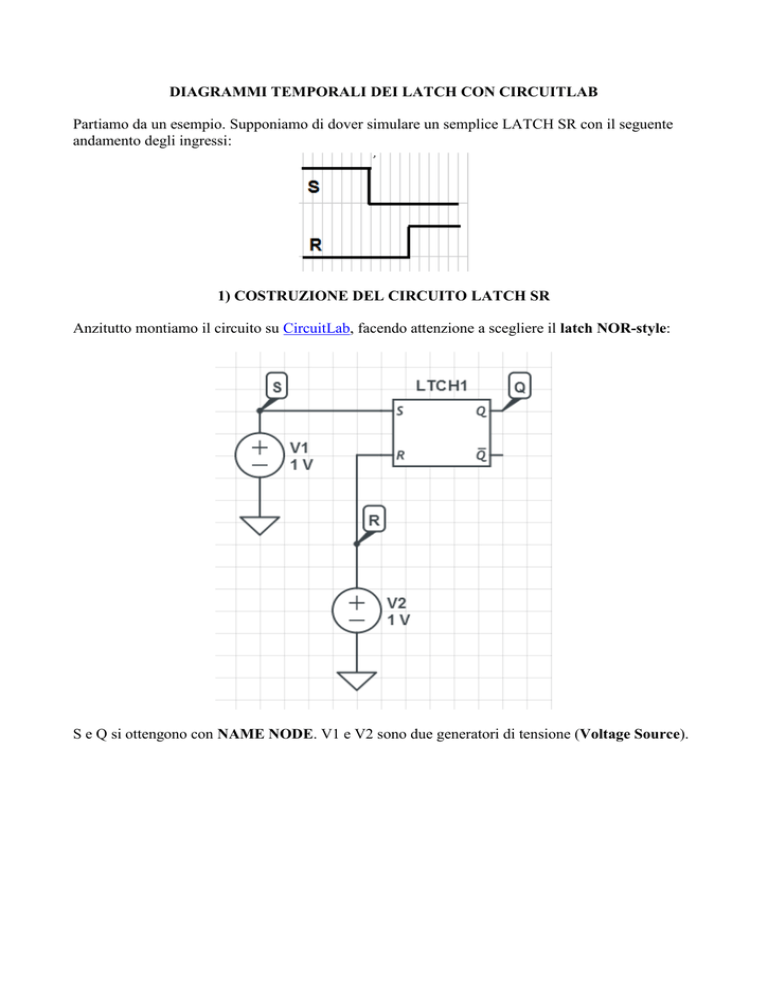

1) COSTRUZIONE DEL CIRCUITO LATCH SR

Anzitutto montiamo il circuito su CircuitLab, facendo attenzione a scegliere il latch NOR-style:

S e Q si ottengono con NAME NODE. V1 e V2 sono due generatori di tensione (Voltage Source).

2) IMPOSTARE I GENERATORI DI INGRESSO

Facciamo quindi doppio click sul generatore V1 (Set) e nel campo riservato ai valori della tensione

scriviamo: PWS(0,5,7,0)

In questo modo il generatore V1 non produce più una tensione costante, ma una sequenza di valori

binari nel tempo secondo la seguente (vedi la figura più in basso): PWS(0,5,7,0) significa che

all’istante 0 la tensione da produrre vale 5 volt (cioè un livello alto) e all’istante 7 (bisogna contare

il numero dei quadretti per sapere il valore dell’istante) la tensione vale 0 (livello basso):

Con lo stesso metodo scriviamo nel campo riservato alla tensione prodotta dal generatore V2

(Reset): PWS(0,0,11,5)

3) SIMULAZIONE

Procediamo quindi alla simulazione del circuito. Scegliamo Simulate, Time Domain e riempiamo i

campi come mostrato in figura:

Il valore 15 di Stop Time è stato scelto in modo da coprire l’intero intervallo della simulazione

(dato che Reset va a 1 all’istante 11, abbiamo abbondato un po’, in modo da ottenere un grafico

completo).

Il valore 0.01 di Time Step è fisso per tutte le simulazioni di questo tipo.

V(S), V(R) e V(Q) si ottengono cliccando sui rispettivi nodi di ingresso e di uscita.

Infine clicchiamo su Advanced Graphing e trasciniamo l’etichetta di ogni segnale di ingresso e di

uscita su un grafico separato, come mostrato in figura:

Infine avviamo la simulazione cliccando su Run Time-Domain Simulation. Se non abbiamo

commesso errori dovremmo ottenere i diagrammi temporali mostrati in figura:

4) LATCH SR CON ABILITAZIONE

Realizzate in CircuitLab il seguente circuito (usando sempre latch nor style):

Fornite ai tre ingressi S, E e R i segnali seguenti (usando i generatori come spiegato prima; la scala

sull’asse dei tempi è in secondi). Simulate il circuito e copiate qui i grafici dei segnali S, E e R.

5) LATCH D

Seguendo le indicazioni di http://www.elemania.altervista.org/digitale/ff/ff5.html realizzate con

CircuitLab lo schema di un latch D. Copiate qui sotto il circuito:

Scegliete ora a piacere un andamento sensato per i segnali D e E di ingresso al latch e realizzate una

simulazione, copiando qui sotto i grafici di D, E e dell’uscita Q. Non svolgete questa parte a caso!!!

Pensateci…