ISTITUTO TECNICO INDUSTRIALE “P. HENSEMBERGER”

Laboratorio

di Elettronica

Data

22 /03/08

Relazione

n° 6

Classe

Villa Andrea

Cognome e Nome

3^B1

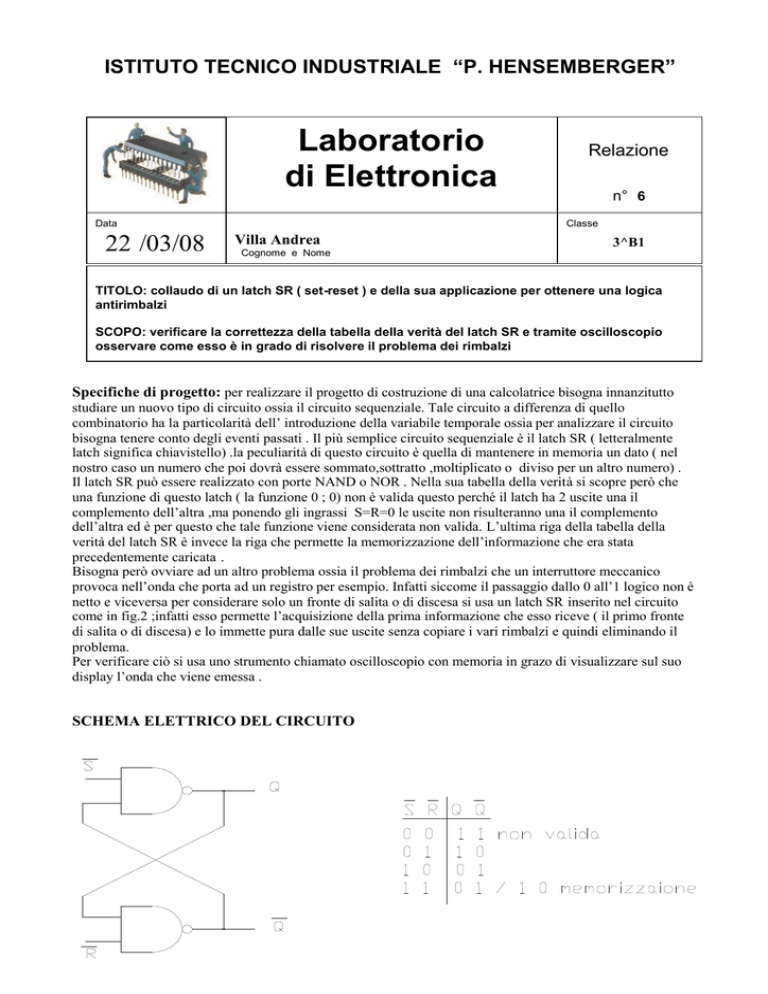

TITOLO: collaudo di un latch SR ( set-reset ) e della sua applicazione per ottenere una logica

antirimbalzi

SCOPO: verificare la correttezza della tabella della verità del latch SR e tramite oscilloscopio

osservare come esso è in grado di risolvere il problema dei rimbalzi

Specifiche di progetto: per realizzare il progetto di costruzione di una calcolatrice bisogna innanzitutto

studiare un nuovo tipo di circuito ossia il circuito sequenziale. Tale circuito a differenza di quello

combinatorio ha la particolarità dell’ introduzione della variabile temporale ossia per analizzare il circuito

bisogna tenere conto degli eventi passati . Il più semplice circuito sequenziale è il latch SR ( letteralmente

latch significa chiavistello) .la peculiarità di questo circuito è quella di mantenere in memoria un dato ( nel

nostro caso un numero che poi dovrà essere sommato,sottratto ,moltiplicato o diviso per un altro numero) .

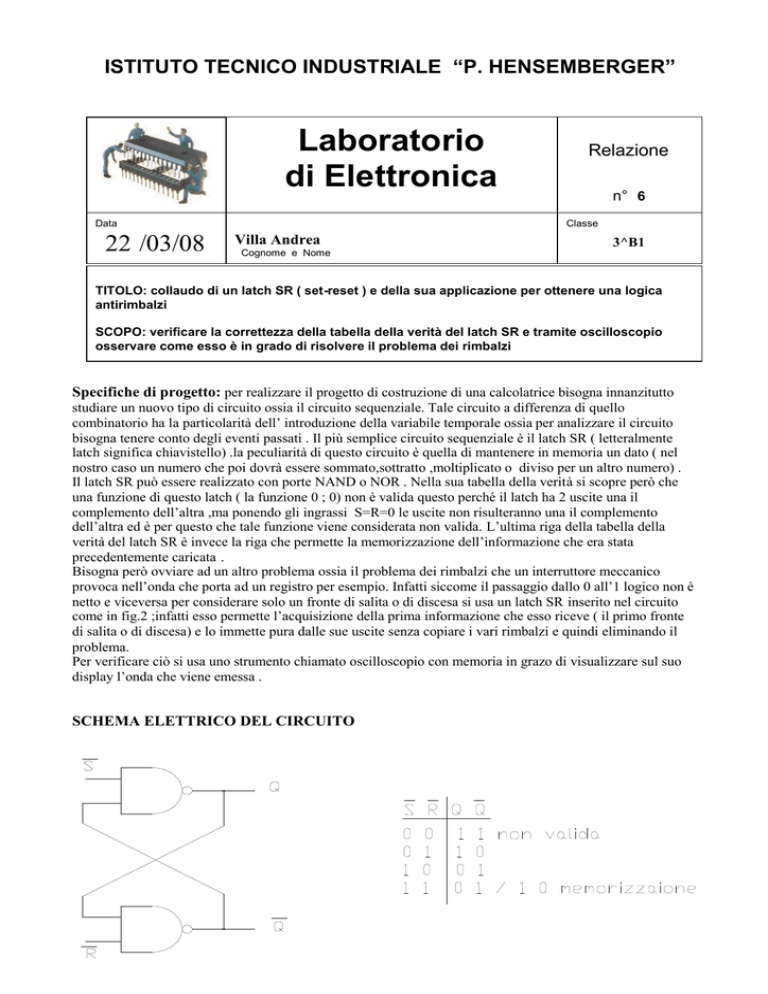

Il latch SR può essere realizzato con porte NAND o NOR . Nella sua tabella della verità si scopre però che

una funzione di questo latch ( la funzione 0 ; 0) non è valida questo perché il latch ha 2 uscite una il

complemento dell’altra ,ma ponendo gli ingrassi S=R=0 le uscite non risulteranno una il complemento

dell’altra ed è per questo che tale funzione viene considerata non valida. L’ultima riga della tabella della

verità del latch SR è invece la riga che permette la memorizzazione dell’informazione che era stata

precedentemente caricata .

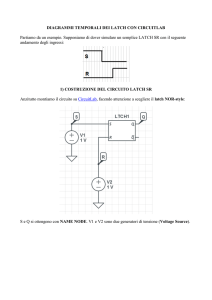

Bisogna però ovviare ad un altro problema ossia il problema dei rimbalzi che un interruttore meccanico

provoca nell’onda che porta ad un registro per esempio. Infatti siccome il passaggio dallo 0 all’1 logico non è

netto e viceversa per considerare solo un fronte di salita o di discesa si usa un latch SR inserito nel circuito

come in fig.2 ;infatti esso permette l’acquisizione della prima informazione che esso riceve ( il primo fronte

di salita o di discesa) e lo immette pura dalle sue uscite senza copiare i vari rimbalzi e quindi eliminando il

problema.

Per verificare ciò si usa uno strumento chiamato oscilloscopio con memoria in grazo di visualizzare sul suo

display l’onda che viene emessa .

SCHEMA ELETTRICO DEL CIRCUITO

circuito antirimbalzi

Elenco componenti e strumentazione utilizzati:

N°1 bradboard

N°1 alimentatore a tensione costante 5 V

N°1 integrato 74LS00

Fili elettrici

Pulsante elettro-meccanico

N°1 led giallo

N°1 resistenza da 380 Ohm

Oscilloscopio

N°2 resistenze da 1KΩ

Conclusioni: Dopo aver montato il circuito abbiamo verificato la tabella della verità del latchSR

in particolare ci siamo soffermati sulla funzione di memorizzazione abilitata con la combinazione

di ingresso set e reset a 1. Dopo grazie all’oscilloscopio abbiamo osservato come l’onda prima del

latch sia disturbata con la presenza di molteplici fronti di salita e di discesa,mentre all’uscita del

latch l’onda risulta regolare con uno stacco netto tra il livello logico basso e alto . Quindi si è

osservato come in questa applicazione tale latch permette di ovviare al problema dei rimbalzi

presentati da parti meccaniche all’interno del circuito.

.