![Digitale ASIC [modalità compatibilità]](//s1.studylibit.com/store/data/004260298_1-216dae74e3ba93542de699caff89a76f-768x994.png)

- M. Poli e S. Rocchi – diapositiva 1

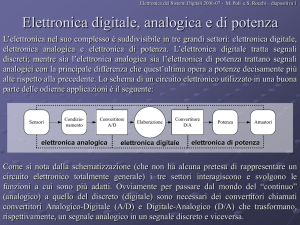

Elettronica digitale, analogica e di potenza

L’elettronica nel suo complesso è suddivisibile in tre grandi settori: elettronica digitale,

elettronica analogica e elettronica di potenza. L’elettronica digitale tratta segnali

discreti; mentre sia l’elettronica analogica sia l’elettronica di potenza trattano segnali

analogici con la principale differenza che quest’ultima opera a potenze decisamente più

alte rispetto alla precedente. Lo schema di un circuito elettronico utilizzato in una buona

parte delle odierne applicazioni è il seguente:

elettronica analogica

elettronica digitale

elettronica di potenza

Come si nota dalla schematizzazione (che non ha alcuna pretesa di rappresentare un

circuito elettronico totalmente generale) i tre settori interagiscono e svolgono le

funzioni a cui sono più adatti. Ovviamente per passare dal mondo del “continuo”

(analogico) a quello del discreto (digitale) sono necessari dei convertitori chiamati

convertitori Analogico-Digitale (A/D) e Digitale-Analogico (D/A) che trasformano,

rispettivamente, un segnale analogico in un segnale discreto e viceversa.

M. Poli e S. Rocchi – diapositiva 2

Alcune caratteristiche importanti dei settori

dell’elettronica

Settore

Digitale

Potenza istantanea ●

Analogico

Potenza

●●

●●●

●●

●●●

Corrente di picco ripetitiva ●

●

●●●

Corrente di picco non ripetitiva ●

●

●●●

●●

●

●

●

Rumore ●

●●●

●

Sensibilità alle condizioni operative ●

●●●

●●

●●

●●●

Tolleranze di processo ●

●●●

●

Linearità ●

●●●

●

●●

●●

Potenza media ● ●

Frequenza ● ● ●

Scala di integrazione ● ● ●

Rendimento di conversione ●

Limiti operativi in corrente e tensione ●

M. Poli e S. Rocchi – diapositiva 3

Convertitore analogico-digitale

Il convertitore analogico-digitale (abbreviato come ADC, A/D) è un circuito elettronico

il cui scopo è quello di convertire segnali analogici (tensione, corrente, carica elettrica)

in segnali discreti (digitali). La conversione analogico-digitale si compone di due passi:

campionamento e quantizzazione.

Il campionamento è l’operazione mediante la quale si estraggono campioni del segnale

ad intervalli di tempo regolari

Segnale continuo

Segnale campionato

Detta fH la massima frequenza del segnale [s(t)] da campionare, dal segnale campionato

[sc(t)] è ricostruibile il segnale originario se e solo se la frequenza di campionamento

(fS=1/∆T) è maggiore di 2 fH (teorema di Nyquist-Shannon): fS > 2fH.

M. Poli e S. Rocchi – diapositiva 4

Convertitore analogico-digitale

Dall’operazione di campionamento vengono restituiti campioni “continui” del segnale;

tali valori non possono essere rappresentati in un dominio discreto, dunque devono

essere discretizzati. La quantizzazione è l’operazione che associa ad un insieme

continuo (contenente infiniti elementi) un insieme discreto (contenente un numero finito

di valori) secondo una determinata funzione di quantizzazione.

Segnale campionato

Segnale quantizzato

Nella figura precedente si sono usati 16 livelli di quantizzazione (4 bit=24 livelli) e si è

usata una funzione di quantizzazione che associa ad ogni livello continuo il livello

discreto più prossimo. Più è alto il numero di bit utilizzati nella quantizzazione e minore

è l’errore che si commette nella quantizzazione (errore di quantizzazione), cioè si riduce

la distanza media tra il valore campionato e il corrispondente valore quantizzato.

M. Poli e S. Rocchi – diapositiva 5

Caratteristiche statiche invertitore

vi

vo

►Caratteristica di trasferimento vo/vi

►Soglia logica

►Swing logico di ingresso

►Swing logico di uscita

►Margine di rumore

M. Poli e S. Rocchi – diapositiva 6

Caratteristica di trasferimento Vo/Vi

La caratteristica di trasferimento (f.d.t.) in tensione di un invertitore è la relazione che

lega la tensione di uscita vo con la tensione di ingresso vi

vo = f (vi )

La f.d.t. si costruisce a tratti facendo riferimento ad una catena di invertitori uguali

vo,k-2

K-2

vi,k-2

v i , k +1 = v o , k

K-1

vi,k-1

vo,k

vo,k-1

K

vi,k

v o , k = f k (v i , k − 1 )

vo,k+1

K+1

vi,k+1

v o , k + 1 = f k + 1 (v i , k + 1 ) = f k + 1 (v o , k ) = f k + 1 ( f k (v i , k − 1 ))

M. Poli e S. Rocchi – diapositiva 7

vo,k = vi,k+1

Caratteristica di trasferimento vo/vi

vo ,k = f k (vi , k )

vo ,k = f k (vi ,k )

Le curve

B

vo ,k +1 = f k +1 (vi , k +1 )

vo ,k +1 = f k +1 (vi , k +1 )

hanno 3 punti di intersezione: A, B, C. Le

coordinate di A e B vengono definite valori

di ingresso nominali

A = {viHnom , voLnom }

B = {viLnom , voHnom }

C

Le coordinate del punto C, vengono definite

soglia logica (SL), cioè il punto della

caratteristica di un invertitore in cui Vo=Vi

45°

A

vi,k = vo,k-1

C = {viSL , voSL }

M. Poli e S. Rocchi – diapositiva 8

Swing logico

Si individuano inoltre i punti D e E tali che

dvo

= −1

dvi

vo

voHmin

D

vo = f (vi )

di coordinate

D = {viL max ,voH min }

E = {viH min , voL max }

Si definiscono swing logico di ingresso (ILS) e

di uscita (OLS) le seguenti grandezze

E

voLmax

viLmax

viHmin

I LS = viH min − viL max

vi

OLS = voH min − voL max

M. Poli e S. Rocchi – diapositiva 9

Zone operative dell’invertitore

La derivata dvo/dvi può essere vista come il limite per ∆vi che tende a zero del guadagno differenziale di

tensione, in altri termini

dvo

∆vo

= lim

dvi ∆vi →0 ∆vi

Da un punto di vista geometrico, quindi, dvo/dvi=-1 rappresenta quei punti in cui si ha un guadagno in

tensione unitario e invertente, ovvero quei punti in cui ad una variazione positiva/negativa dell’ingresso

corrisponde una uguale variazione negativa/positiva dell’uscita. Da queste considerazioni derivano le

seguenti:

Se vi≤viLmax oppure vi≥viHmin allora:

dvo

≤1

dvi

in tale zona l’invertitore sopprime i

disturbi (rumore) della tensione di

ingresso (proprietà rigenerativa)

Se viLmax ≤ vi≤viHmin allora:

dvo

≥1

dvi

in tale zona l’invertitore amplifica la

tensione di ingresso, l’uscita

dell’invertitore è instabile e tende ad

andare o verso voLnom, o verso voHnom.

M. Poli e S. Rocchi – diapositiva 10

Margini di rumore

Il rumore nel dominio digitale rappresenta variazioni indesiderate del valore logico di un nodo. Si definisce

margine di rumore di un invertitore il massimo livello di rumore che può essere sostenuto dall’invertitore (un

livello maggiore porta ad un malfunzionamento dell’invertitore e quindi ad un valore indeterminato del nodo

di uscita) quando è messo in cascata con un altro invertitore uguale.

vi1

vo1= vi2

I1

vo2

vi2 = vo1

I2

voHmin

viHmin2

Si definisce margine di rumore

alto (NMH) la differenza

NM H = voH min − viH min 2

viLmax2

analogamente si definisce

margine di rumore basso

(NML) la differenza

NM L = viL max 2 − voL max

NMH

NML

voLmax

vo2

viLmax

viHmin

Dal momento che i due invertitori sono uguali si ha: viHmin2 = viHmin e viLmax2 = viLmax dunque

NM H = voH min − viH min

NM L = viL max − voL max

vi1

M. Poli e S. Rocchi – diapositiva 11

Significato fisico dei margini di rumore

Supponiamo che vi1 sia basso (vi1≤viLmax), di conseguenza vo1= vi2 è alto (vo1≥voHmin, vi2 ≥viHmin) e vo2 è basso

(vo2≤voLmax). Adesso ipotizziamo che per qualche ragione (rumore) il nodo vo1 subisca una variazione di

tensione superiore a NMH+δ e che dunque si posizioni ad un livello pari a voE. Quale sarà il valore di tensione

di uscita vo2? Inizialmente vo2 avrà un valore vo2E, ma tale valore, come discusso in precedenza, si trova in una

zona di instabilità della caratteristica, quindi dopo un certo transitorio, vo2 tenderà o a voLnom oppure a voHnom.

Il problema risiede nel fatto che a priori non è possibile stabilire a quale valore tende, dando così una

indeterminazione funzionale non voluta in un circuito digitale.

Da questa breve considerazione si deduce che i margini di rumore sono delle variazioni di tensione superate

le quali non è più garantito il funzionamento del circuito digitale.

vi1

vo1= vi2

I1

vo2

I2

vi2 = vo1

δ

voHmin

NMH

viHmin2

voE

viLmax2

NML

voLmax

vo2

vo2E

viLmax

viHmin

vi1

M. Poli e S. Rocchi – diapositiva 12

Potenza media statica

Siano IoL e IoH rispettivamente le correnti (statiche) erogate dalla tensione di alimentazione VDD in

corrispondenza delle tensioni nominali di uscita voLnom e voHnom. Si definisce potenza media statica la quantità

PST = VDD

I oL + I oH

2

VDD

vo

IoH

voHnom

INV

voHnom

VDD

IoL

INV

voLnom

voLnom

vi

M. Poli e S. Rocchi – diapositiva 13

Fan-in e fan-out

►Si definisce fan-in il numero massimo di ingressi ad una

porta logica che ne garantiscono il funzionamento

►Si definisce fan-out il numero massimo di porte logiche che

una data porta può pilotare garantendo il suo funzionamento

fan-in

Con riferimento allo specifico caso riportato in figura,

entrambe le definizioni sono associate all’invertitore INV;

in tal caso il fan-in e il fan-out sono, rispettivamente, il

numero massimo di invertitori che possono pilotare e

essere pilotati da INV mantenendo il suo funzionamento

logico corretto. Ciascun invertitore (così come tutte le

porte logiche) ha una capacità di ingresso e una capacità

di uscita. Le capacità di uscita degli invertitori Ii1…Iim

contribuisco ad aumentare la capacità in ingresso a INV,

mentre quelle di ingresso di Io1…Ion aumentano la sua

capacità di uscita. Si comprende quindi come

all’aumentare di m e n si possa raggiungere un carico

capacitivo di ingresso/uscita non più sostenibile da INV:

in altri termini trattandosi di un invertitore questo

significa che INV non effettuerebbe più correttamente

l’inversione dell’ingresso.

fan-out

Ii1

Io1

Ii2

Io2

Iim

INV

Ion

M. Poli e S. Rocchi – diapositiva 14

Caratteristiche dinamiche invertitore

vi

vo

►Tempo di salita

►Tempo di discesa

►Ritardo di salita (tempo di propagazione basso-alto)

►Ritardo di discesa (tempo di propagazione alto-basso)

►Ritardo di propagazione (tempo di propagazione)

M. Poli e S. Rocchi – diapositiva 15

Caratteristiche dinamiche invertitore

Si consideri un invertitore k inserito in una catena di invertitori come riportato in figura. Siano note CI e CO,

rispettivamente la capacità di ingresso e di uscita di tale invertitore, allora è possibile trovare un circuito

equivalente al precedente sostituendo all’ingresso e all’uscita di k i carichi capacitivi equivalenti (CT e CL):

vi

k+1

k-1

vi

k

vo

k+2

CO + C I = CT

k

vo

C L = CO + n ⋅ C I

vi

vo

t

k+n

t

Ovviamente la presenza di capacità di ingresso e di uscita altera il funzionamento del circuito portando a

delle distorsioni delle forme d’onda di ingresso e uscita. La capacità CT è la somma di due capacità

solitamente sufficientemente piccole da non causare distorsioni in vi, mentre la capacità CL è tale da causare

distorsioni nella forma d’onda di uscita (vo). Chiaramente questo è solo un esempio, a seconda dell’entità dei

carichi capacitivi equivalenti si hanno più o meno distorsioni.

M. Poli e S. Rocchi – diapositiva 16

Tempi di salita e di discesa

Con riferimento alla figura, si individuino i punti in cui vo è pari al 90% e al 10% della massima escursione in

tensione di uscita (vOH - vOL); vo raggiunge i suddetti valori rispettivamente nei tempi tf90, tf10 per la transizione

alto-basso e tr90, tr10 per quella basso-alto.

vi

vo

vOH

tir

tif

t

vO90%=vOL+0.9(vOH-vOL)

vO10%=vOL+0.1(vOH-vOL)

vOL

tf90

tf10 tr10

tr90

t

Si definisce tempo di salita tr la differenza tr90-tr10

t r = t r 90 − t r10

Si definisce tempo di discesa tf la differenza tf10-tf90

t f = t f 10 − t f 90

M. Poli e S. Rocchi – diapositiva 17

Esempio di calcolo del tempo di salita/discesa

In un modello semplificato dell’invertitore, per il teorema di Thevenin, l’uscita dell’invertitore può essere

vista come un generatore di tensione con in serie una resistenza. Quanto l’uscita dell’invertitore transita da

basso (vOL ) a alto (vOH) il generatore di tensione equivalente di Thevenin è pari a vOH, quanto transita da alto

(vOH) a basso (vOL ) il suo valore è nullo. Dunque si ha

R

k

CL

vEQ

cL

Supponendo per semplicità che vOH = VDD e vOL = 0, il tempo di salita/discesa si calcola come segue.

Rr

0

VDD

Rf

VDD

cL

cL

t −tif

−

tr 90% − tif = − ln(0.1) ⋅ Rr CL ≅ 2.3Rr CL

Rr CL

⇒

⇒ vO = VDD 1 − e

tr10% − tif = − ln(0.9) ⋅ Rr CL ≅ 0.1Rr CL

⇒ vO = VDDe

−

t −tir

R f CL

⇒

⇒ tr ≅ 2.2Rr CL

t f 90% − tir = − ln(0.9) ⋅ R f CL ≅ 0.1R f CL

⇒ t f ≅ 2.2R f CL

t f 10% − tir = − ln(0.1) ⋅ R f CL ≅ 2.3R f CL

Si noti che l’invertitore è stato modellato con due diverse resistenze equivalenti per la transizione basso-alto

(Rr) e per quella alto-basso (Rf) dato che, in generale, non è detto che l’invertitore abbia un comportamento

“simmetrico” nelle due transizioni. Nel caso in cui l’invertitore sia simmetrico e quindi Rr = Rf = R si ha

t r = t f ≅ 2.2 RC L

M. Poli e S. Rocchi – diapositiva 18

Ritardi di salita e di discesa

Analogamente a quanto fatto prima, si individuino i punti in cui vo è pari al 50% della massima escursione in

tensione di uscita (vOH - vOL); vo raggiunge i suddetti valori rispettivamente nei tempi tof50 per la transizione

alto-basso e tor50 per quella basso-alto. Si individuino inoltre i punti in cui vi è pari al 50% della massima

escursione in tensione di ingresso (vIH - vIL); vi raggiunge i suddetti valori rispettivamente nei tempi tif50 per la

transizione basso-alto e tir50 per quella alto-basso (vi è un’onda quadra quindi tali valori coincidono con

l’inizio delle transizioni).

vi

Si definisce ritardo di salita τpLH o

tempo di propagazione basso-alto

vIH

τ pLH = tor 50 − tif 50

vIL

vo

tir50

tif50

t

vOH

vO50%=vOL+0.5(vOH-vOL)

Si definisce ritardo di discesa τpHL

o tempo di propagazione altobasso

τ pHL = tof 50 − tir 50

vOL

τpLH

tof50

τpHL

tor50

t

Si definisce inoltre ritardo di propagazione τpd o tempo di propagazione la quantità

τ pd =

τ pLH + τ pHL

Nel caso di invertitore simmetrico si parla solo di tempo di propagazione e si ha τpLH = τpHL = τpd.

2

M. Poli e S. Rocchi – diapositiva 19

Esempio di calcolo del tempo di propagazione

Come fatto in precedenza si usa il seguente modello semplificato dell’invertitore

R

k

CL

vEQ

cL

e per semplicità si suppone che vOH = VDD e vOL = 0, quindi

Rr

0

VDD

Rf

VDD

cL

cL

t − tif 50

−

Rr C L

⇒ vO = VDD 1 − e

⇒ τ pLH = − ln (0.5) ⋅ Rr CL ≅ 0.69 Rr C L

⇒ vO = VDD e

−

t − tir 50

R f CL

⇒ τ pHL = − ln (0.5) ⋅ R f C L ≅ 0.69 R f CL

Come nel caso precedente, l’invertitore è stato modellato con due diverse resistenze equivalenti per la

transizione basso-alto (Rr) e per quella alto-basso (Rf).

Nel caso in cui l’invertitore sia simmetrico e quindi Rr = Rf = R si ha

1

1

τ pd = τ pLH = τ pHL ≅ 0.69 RC L ≅ t r = t f

3

3

M. Poli e S. Rocchi – diapositiva 20

Stima della massima frequenza operativa

Sia T il periodo (f = 1/T la frequenza) dell’onda quadra in ingresso all’invertitore, quale è il minimo periodo

consentito (la massima frequenza consentita) affinché il funzionamento dell’invertitore sia garantito?

Il funzionamento dell’invertitore è garantito quando è possibile ricostruire il segnale digitale di uscita, in altri

termini quando è possibile discernere lo stato alto dell’uscita da quello basso. Dunque è sufficiente garantire

che una transizione basso-alto dell’ingresso porti l’uscita al di sotto della soglia logica vSL e che una

transizione alto-basso dell’ingresso porti l’uscita al di sopra della soglia logica: da questi punti in poi,

trovandosi l’uscita in una zona di instabilità, tenderà a convergere verso i punti stabili (voHnom, voLnom) più

vicini al valore di tensione iniziale. In realtà, come si è discusso in precedenza, la zona di instabilità non dà

assoluta garanzia del funzionamento dell’invertitore, quindi il metodo precedente offre una stima per eccesso

della massima frequenza operativa.

vo

voHnom

45°

voLnom

vSL

vi

M. Poli e S. Rocchi – diapositiva 21

Stima della massima frequenza operativa

Una stima più conservativa (per vi

difetto) si può ottenere garantendo

per l’uscita dell’invertitore un tempo

maggiore della somma del tempo di

salita e del tempo di discesa (tr + tf);

in tal caso infatti ci si troverebbe

nella condizione limite in cui

l’uscita è molto simile ad un’onda vo

triangolare. Dunque

Tmin

Tmin ≥ tr + t f ≅ 2.2 ⋅ C L (Rr + R f )

tf90 tf10

Garantendo un ulteriore 20% di margine la stima di Tmin risulta

tr10

t

tr90

Tmin = 1.2 ⋅ 2.2 ⋅ CL (Rr + R f ) = 2.64 ⋅ C L (Rr + R f )

Che nell’ipotesi di invertitore simmetrico diviene

Tmin = 5.28 ⋅ RCL

t

M. Poli e S. Rocchi – diapositiva 22

Dissipazione di potenza

In un circuito digitale (e non solo) la dissipazione di potenza è strettamente legata la calore dissipato dal

circuito e all’energia richiesta da ciascuna operazione, quindi è legata a

►Numero di dispositivi integrabili per chip

►Tipo di package

►Tipologia di sistema di raffreddamento richiesta

►Massima tensione e massima corrente richieste

Mentre il “Numero di dispositivi integrabili per chip” è un problema che riguarda tutte le tipologie di circuiti

digitali perché, in genere, si vuole la più alta scala di integrazione possibile, per quanto riguarda gli altri punti

essi sono legati alle applicazioni specifiche. Ad esempio per un circuito digitale che viene utilizzato in un

dispositivo portatile sono di primaria importanza il package (più piccolo possibile per ridurre le dimensioni),

la tipologia di raffreddamento (sempre per evitare dimensioni e pesi troppo elevati) e la massima tensione e

corrente richieste (per consentire una maggiore durata della batteria); mentre per un sistema non portatile è di

primaria importanza la tipologia di raffreddamento (il package non è rilevante in quanto si presume si abbia

tutto lo spazio che si vuole per realizzare il circuito; la massima tensione e corrente non sono rilevanti perché

si suppone che l’alimentazione provenga dalla tensione di rete). In definitiva, dunque, la dissipazione di

potenza coinvolge la realizzabilità, il costo e l’affidabilità di un circuito digitale.

M. Poli e S. Rocchi – diapositiva 23

Contributi alla dissipazione di potenza

Dato un circuito digitale sia Va la tensione di alimentazione (costante) e ia(t) la corrente da

essa erogata. Si definisce potenza istantanea P(t) il prodotto

Va

P(t ) = Va ⋅ ia (t )

ia(t)

Circuito

digitale

tale potenza è la potenza erogata, istante per istante, dall’alimentazione. Si definisce potenza

di picco Ppeak il massimo della potenza istantanea o in altri termini il prodotto della massima

corrente (ipeak) erogata dall’alimentazione per la tensione di alimentazione stessa Va

Ppeak = max (P(t )) = i peak ⋅ Va

La potenza istantanea è dunque quella grandezza che determina la massima corrente richiesta dal circuito.

Quasi tutti i circuiti digitali (sono rare le eccezioni) posseggono un clock che ne scandisce le operazione.

Detto T il periodo (frequenza f = 1/T) di clock di un circuito digitale si definisce potenza media Pavg la

potenza dissipata dal circuito in un periodo di clock

Pavg

1

=

T

Va

∫0 Va ⋅ ia (t )dt = T

T

∫ i (t )dt

T

0

a

Com’è facile intuire, alla potenza media sono legati la “tipologia di sistema di raffreddamento“ e la massima

tensione di alimentazione richiesta e dunque la durata della batteria nei dispositivi portatili è strettamente

correlata ad essa.

M. Poli e S. Rocchi – diapositiva 24

Potenza dinamica

EH = ∫ VDD ⋅ ic (t )dt = VDD ∫ ic (t )dt

Durante una transizione basso-alto l’energia totale EH erogata dall’alimentazione è

VDD

∞

ic

INV

∞

= VDD ⋅ C L ∫

0

0

vOH

vOL

dV = VDD ⋅ C L ⋅ (vOH − vOL )

cL dove con vOH e vOL si è indicata, rispettivamente, la tensione di uscita massima e

minima. Solo metà dell’energia totale erogata viene immagazzinata (e quindi non

viene persa) in CL il resto viene dissipata (e quindi persa) dai dispositivi che

compongono l’invertitore.

VDD

Durante la transizione alto-basso CL perde la carica immagazzinata

precedentemente (e quindi l’energia ad essa associata) che viene dissipata nei

dispositivi usati per scaricare il condensatore: in questa fase l’alimentazione non

INV

fornisce energia. Quindi durante una transizione completa basso-alto-basso

cL

l’energia EL→H →L dissipata è

ic

E L→ H → L = VDD ⋅ C L ⋅ (vOH − vOL )

Dato il clock di periodo T (f = 1/T) si definisce potenza dinamica Pd =

Nel caso in cui vOH = VDD e vOL = 0 la potenza dinamica diviene

EL → H → L

= VDD ⋅ C L ⋅ (vOH − vOL ) ⋅ f

T

2

Pd = VDD

⋅ CL ⋅ f

La potenza dinamica dipende dalle capacità del circuito, dalla tensione di alimentazione e dalla frequenza

operativa: cresce linearmente con la frequenza e in modo quadratico con la tensione di alimentazione.

M. Poli e S. Rocchi – diapositiva 25

Potenza di cortocircuito

vi

vo

t

vOH

vOL

icc

icc1

t1

icc2

t2

t3 t4

t

Si definisce potenza di cortocircuito la potenza necessaria per far

commutare la tensione di uscita da vOL a vOH e viceversa attraverso

zone delle caratteristiche dei dispositivi corrispondenti a correnti

non nulle: spesso la commutazione dell’uscita passa attraverso zone

di funzionamento dei dispositivi in cui si crea un percorso diretto

(cortocircuito) tra l’alimentazione e massa, in tal caso

l’alimentazione eroga una corrente non nulla generando una

dissipazione di potenza. Dette icc1(t) e icc2(t) le correnti di

cortocircuito, rispettivamente per la transizione dell’uscita altobasso e basso-alto si definisce potenza di cortocircuito Pcc la

quantità

Pcc =

t

t4

VDD t 2

(

)

i

t

dt

+

icc1 (t )dt

cc

1

∫

∫

t3

T t1

Nell’ipotesi di comportamento simmetrico le correnti icc1(t) e icc2(t) hanno un andamento uguale e quindi

Pcc = 2

VDD

T

∫

t2

t1

icc1 (t )dt

In generale, nei comuni circuiti digitali, la potenza di cortocircuito è molto minore della potenza dinamica

Pcc << Pd

M. Poli e S. Rocchi – diapositiva 26

Circuiti ASIC

Un circuito integrato per applicazioni specifiche ASIC (Application Specific Integrated Circuit) è un circuito

integrato (IC) adattato alle esigenze di una particolare applicazione, piuttosto che progettato per un uso

generale. Ad esempio un chip progettato solamente per essere utilizzato in un telefono cellulare è un ASIC.

Un ASIC è progettato cercando di soddisfare prima di tutto le specifiche funzionali (il modo in cui dovrà

operare) e in secondo luogo cercando di ottimizzare simultaneamente vari vincoli di progetto (design

constraints). I seguenti sono vincoli di progetto comunemente tenuti in considerazione (ovviamente non sono

i soli):

► Vendibilità: un ASIC è progettato solo se esiste un mercato di vendita. Il

tipo di mercato determina la scelta della tipologia di progetto.

► Produttività: il prodotto deve essere producibile con un minimo scarto

(circuiti non funzionanti) e deve essere adatto a qualsiasi condizione

operativa prevista dal mercato di destinazione: consumer, militare, ecc.

► Tempo di ingresso sul mercato (time-to-market)

► Costo

► Flessibilità: la possibilità di cambiare le funzionalità del sistema senza

doverlo riprogettare completamente

► Prestazioni: densità di componenti integrati per IC, potenza dissipata,

velocità del sistema

M. Poli e S. Rocchi – diapositiva 27

Tempo di immissione sul mercato (time-to-market)

Guadagni

Previsione di guadagno

È il tempo necessario per portare un sistema ad uno sviluppo tale da

poter essere immesso sul mercato e quindi venduto (mediamente tale

tempo è fissato ad 8 mesi). La progettazione di un ASIC è preceduta da

un’analisi di mercato che fornisce la cosiddetta “finestra di mercato”

(market window), vale a dire il periodo durante il quale il sistema

Finestra di mercato

potrebbe avere le maggiori vendite: uno slittamento dei tempi di

Market window

immissione sul mercato potrebbe produrre un enorme perdita economica

da parte dell’industria che sta progettando il sistema. Si consideri il

modello triangolare semplificato dei guadagni in figura. In tale modello

Tempo in mesi

si suppone che il tempo di vita del prodotto (2V) sia in eguale misura

ripartito tra la fase di crescita e diminuzione delle vendite

Incasso massimo senza

Incasso massimo in

(entrambe di durata V) e i guadagni sono rappresentati

ritardo di immissione

caso di ritardo IMR

IM

dall’aria sottesa dal triangolo. In presenza di un ritardo R di

immissione dunque si avrebbe:

Guadagni senza ritardo = V ·IM

Guadagni con ritardo = (2V – R)·IMR /2

Fase di crescita

delle vendite

Nell’ulteriore ipotesi esemplificativa in cui il fattore di

crescita sia unitario si ha IM = V e IMR = V – R, per cui le

perdite percentuali P% risulterebbero pari a

P% = [V ·IM – (2V – R)·IMR /2] / (V ·IM) ·100% =

= R (3V – R) /(2V2)

(es. V = 12 mesi: R = 2 mesi → P% ≈ 24%; R = 4 mesi → P% ≈ 44%)

R

V

Immissione in tempo

Immissione in ritardo

Fase di

diminuzione

delle vendite

Tempo

2V

M. Poli e S. Rocchi – diapositiva 28

Costo

Il costo di mercato S di un prodotto (il prezzo di vendita) è dato da

S=

CTOT

(1 − m)N

dove CTOT è il costo totale sostenuto dall’industria per produrre quel prodotto, m è il margine di profitto

desiderato e N è il numero di pezzi prodotti. Il costo totale è a sua volta legato ai cosiddetti costi non

ricorrenti CNR (i costi di sviluppo e progettazione sostenuti prima dell’immissione sul mercato) e ai costi

ricorrenti CR (il costo necessario alla produzione di N unità) secondo la relazione

CTOT = C NR + C R = C NR + N ⋅ CU

con CU si è indicato il costo per unità, vale a dire il costo affrontato per la produzione di un singolo pezzo.

Come è facilmente intuibile tale costo è legato al processo tecnologico e quindi alla resa di processo, al tipo

di package usato, al test e al collaudo: ogni singolo chip viene testato e collaudato, e quindi, in fase di

progettazione, è necessario aggiungere dei sistemi che ne facilitano il test e collaudo come circuiti per il

Built-in Self Test (BIST), contatti aggiuntivi sul die, test patterns, ecc.

Contatti aggiuntivi sul die usati per il

test e collaudo. Le strisce nere in figura

sono le punte (molto piccole) di una

macchina per il collaudo appoggiate sui

contatti aggiuntivi.

M. Poli e S. Rocchi – diapositiva 29

Tecnologia

Il progetto di un ASIC è ovviamente fatto con strumenti software CAD che semplificano la progettazione e la

fase di test funzionale mediante strumenti di simulazione circuitale. Alla fine delle simulazioni software il

circuito che si trova in una fase descrittiva a livello di gate (gate-level) deve essere mappato in un circuito

integrato: il modo in cui questo avviene si chiama tecnologia. La tecnologia, in genere, differisce da industria

ad industria ma si possono individuare le seguenti tipologie principali

M. Poli e S. Rocchi – diapositiva 30

Full-custom

Il circuito è progettato in maniere completamente dedicata all’applicazione specifica: in tal caso i progettisti

si occupano della disposizione dei singoli componenti e delle interconnessioni fra essi ottimizzando area e

prestazioni dell’intero circuito integrato. Com’è facile intuire, tale approccio richiede un notevole impiego di

risorse umane e strumentali e un know-how adeguato dell’azienda produttrice. Inoltre i costi e i tempi di

progettazione risultano elevati e giustificati solo per produzioni relativamente grandi (più di 2000000 pezzi) o

per applicazioni particolari. Oggi vengono prodotti con tale tecnica principalmente microprocessori e

memorie da immettere nel mercato consumer.

Vantaggi:

► Elevate prestazioni: maggiore frequenza operativa, maggior numero di componenti integrati

per chip, minore potenza dissipata

► Minore costo per unità: questo è legato alla più alta scala di integrazione e quindi alla minore

area occupata dal chip (a parità di componenti).

► Minore ingombro

Svantaggi:

► Elevati costi non ricorrenti dato che il tempo di progettazione è solitamente molto più lungo e

sono necessari un più largo numero di prototipi rispetto ad altri approcci

► Elevati tempi time-to-market: prima che si arrivi ad una versione del circuito vendibile sul

mercato passano parecchi mesi

► È richiesta una elevata conoscenza specialistica delle tecniche di lavorazione del silicio

M. Poli e S. Rocchi – diapositiva 31

Semi-custom

L’approccio semi-custom fa uso di un numero molto elevato di blocchi funzionali elementari le cui

interconnessioni sono lasciate appositamente incomplete dal costruttore. Il progettista, avvalendosi di

strumenti CAD, definisce le interconnessioni in modo da comporre il circuito integrato adatto alle specifiche

esigenze.

Vantaggi (rispetto all’approccio full-custom):

► Costi non ricorrenti inferiori dato che il tempo di progettazione è solitamente più breve e sono

necessari un più basso numero di prototipi

► Minori tempi time-to-market: il progettista deve solo utilizzare dei blocchi funzionali già

realizzati e testati riducendo così i tempi di progettazione

► È richiesta una bassa conoscenza specialistica delle tecniche di lavorazione del silicio

Svantaggi (rispetto all’approccio full-custom):

► Minori prestazioni: minore frequenza operativa, minore numero di componenti integrati per

chip, maggiore potenza dissipata

► Maggiore costo per unità: l’area di silicio a disposizione non è interamente occupata, infatti

un blocco elementari occupa un’area di silicio sicuramente maggiore di quella effettivamente

richiesta dai componenti in esso contenuti

► Maggiore ingombro

M. Poli e S. Rocchi – diapositiva 32

Semi-custom: standard cells, gate array

►Standard cell (celle standard): Con l’approccio a standard cell, un

circuito integrato viene realizzato mediante il posizionamento e

l’interconnessione di blocchi di base, denominati appunto celle standard.

Con tale approccio la realizzazione di un circuito è effettuata usando

solamente dei blocchi funzionali (flip-flop, full-adder, ecc.) che si trovano

in una libreria software fornite dal costruttore. Ogni cella della libreria ha

quindi delle caratteristiche che non possono essere modificate dal

progettista che si occupa solamente del loro posizionamento e delle

interconnessioni (nemmeno quest’ultime sono totalmente libere dovendo il

progettista seguire determinate regole e percorsi).

►gate array (matrici di gate): la casa costruttrice fornisce via software dei

circuiti integrati formati da matrici di transistori o gate più complessi (ma

comunque tutti uguali) e il progettista stabilisce solamente le interconnessioni tra essi.

M. Poli e S. Rocchi – diapositiva 33

Programmabili

Con questo approccio il progettista acquista un circuito integrato già pronto all’uso. Il compito del progettista

è solo quello di stabilire, attraverso la programmazione del chip, quali interconnessioni attivare e quali

disattivare. La diversa procedura di programmazione (EPROM, E2PROM, SRAM, ecc.) e la tipologia di

tecnologia distingue diverse famiglie di dispositivi programmabili nelle principali tipologie: Complex

Programmable Logic Device (CPLD), Field Programmable Gate-Array (FPGA), Memorie.

Vantaggi (rispetto ai precedenti):

► Costi non ricorrenti bassi dato che la progettazione è molto più breve e non sono richiesti

prototipi (la maggior parte di tali dispositivi si possono programmare più volte)

► Bassi tempi time-to-market: il progettista deve solo utilizzare dei blocchi funzionali già

realizzati e testati riducendo così i tempi di progettazione

► Non è richiesta alcuna conoscenza specialistica delle tecniche di lavorazione del silicio

Svantaggi (rispetto ai precedenti):

► Basse prestazioni: minore frequenza operativa, numero di componenti integrati per chip

fissato, maggiore potenza dissipata

► Costo per unità approssimativamente1 fisso: il dispositivo programmabile ha un costo fisso a

prescindere dal numero di pezzi prodotti (questo rende i dispositivi programmabili adatti a

piccoli numeri di pezzi)

► Alto ingombro

1

Molte ditte fanno prezzi di vendita diversi a seconda del numero di chip acquistati.

M. Poli e S. Rocchi – diapositiva 34

Field Programmable Gate-Array (FPGA)

Un Field Programmable Gate-Array (FPGA) è un chip che contiene blocchi logici e interconnessioni

programmabili. I blocchi di logica programmabile (logic blocks) possono essere configurati per agire da

blocchi logici di base (AND, OR, XOR, NOT, flip-flop, multiplexer) oppure da funzioni combinatorie più

complesse, ad esempio decoder o funzioni matematiche elementari. I blocchi di logica programmabile

conservano la programmazione in elementi di memoria come flip-flop oppure, nei modelli più complessi, in

memorie statiche (SRAM): interconnessioni gerarchiche tra blocchi logici consentono al progettista di

effettuare qualunque funzione logica richiesta.

{

matrici di

interruttori

interconnessioni

A

logic

cell

logic

cell

B

interruttori

controllati da

SRAM

{

logic

cell

logic

cell

cella

SRAM

SRAM

A

B

M. Poli e S. Rocchi – diapositiva 35

Tabella sinottica ASICs

Unità prodotte

CNR

CR

TM

Prestazioni

Full-custom

>2.000.000

Alto

Basso

Alto

Elevate

Semi-custom

Standard cell

Da 200.000

a 2.000.000

↓

↑

↓

↓

Semi-custom

Gate array

Da 20.000

a 200.000

↓

↑

↓

↓

Programmabili

<20.000

↓

↑

↓

↓

Basso

Alto

Basso

Minori

![Digitale ASIC [modalità compatibilità]](http://s1.studylibit.com/store/data/004260298_1-216dae74e3ba93542de699caff89a76f-768x994.png)