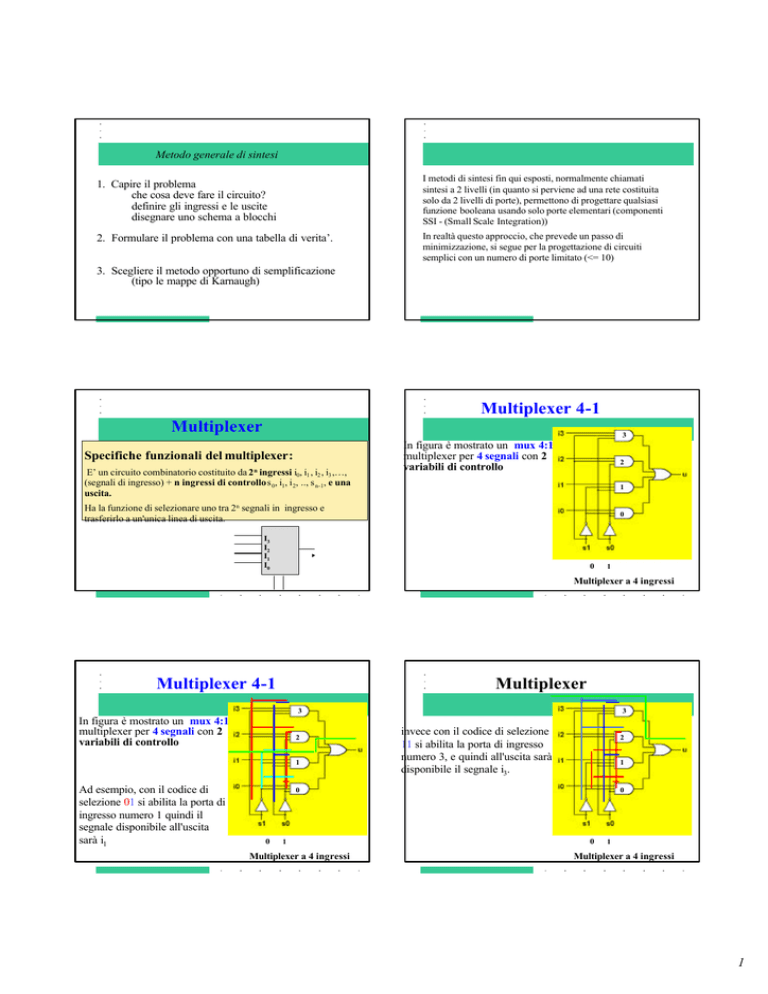

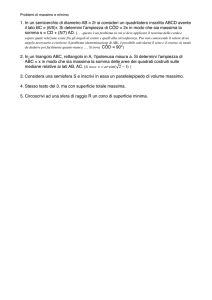

Metodo generale di sintesi

I metodi di sintesi fin qui esposti, normalmente chiamati

sintesi a 2 livelli (in quanto si perviene ad una rete costituita

solo da 2 livelli di porte), permettono di progettare qualsiasi

funzione booleana usando solo porte elementari (componenti

SSI - (Small Scale Integration))

1. Capire il problema

che cosa deve fare il circuito?

definire gli ingressi e le uscite

disegnare uno schema a blocchi

2. Formulare il problema con una tabella di verita’.

In realtà questo approccio, che prevede un passo di

minimizzazione, si segue per la progettazione di circuiti

semplici con un numero di porte limitato (<= 10)

3. Scegliere il metodo opportuno di semplificazione

(tipo le mappe di Karnaugh)

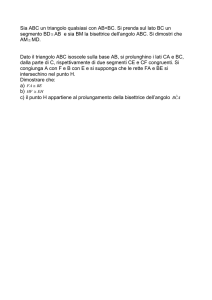

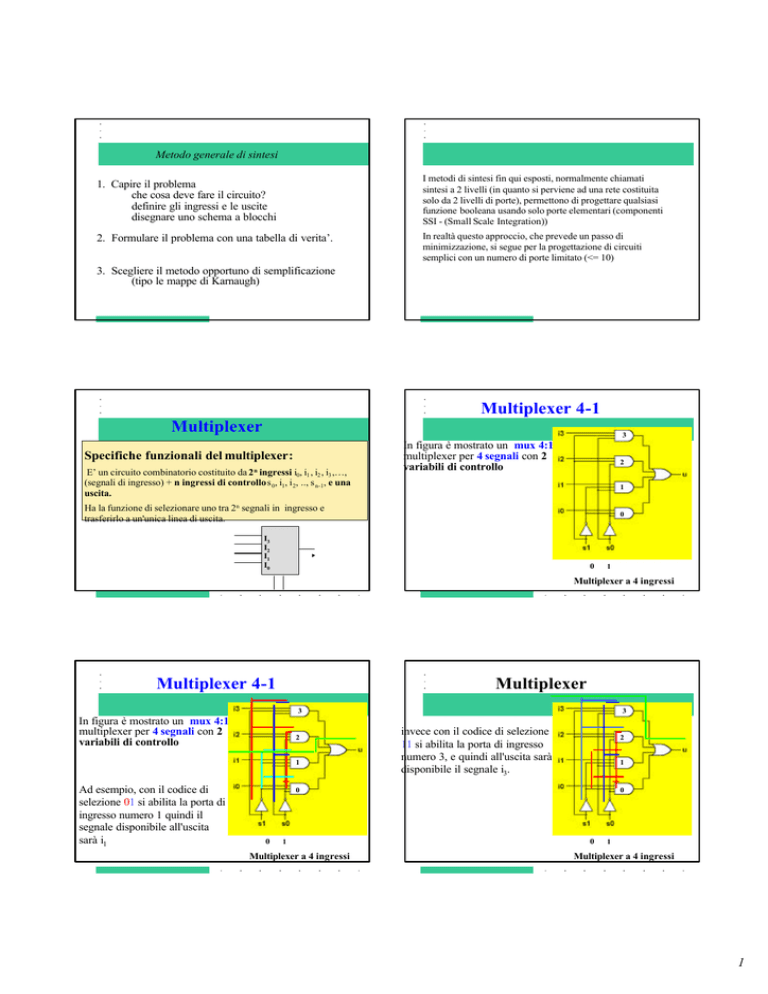

Multiplexer 4-1

Multiplexer

3

Specifiche funzionali del multiplexer:

E’ un circuito combinatorio costituito da 2 n ingressi i0, i1 , i2 , i3 ,…,

(segnali di ingresso) + n ingressi di controllos 0, i1, i 2, .., s n-1, e una

uscita.

In figura è mostrato un mux 4:1

multiplexer per 4 segnali con 2

variabili di controllo

2

1

Ha la funzione di selezionare uno tra 2n segnali in ingresso e

trasferirlo a un'unica linea di uscita.

0

I3

I2

I1

I0

0

1

Multiplexer a 4 ingressi

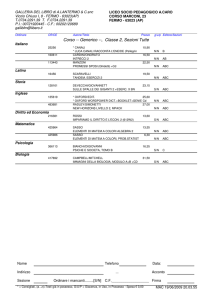

Multiplexer 4-1

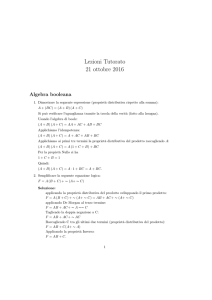

Multiplexer

3

In figura è mostrato un mux 4:1

multiplexer per 4 segnali con 2

variabili di controllo

2

1

Ad esempio, con il codice di

selezione 01 si abilita la porta di

ingresso numero 1 quindi il

segnale disponibile all'uscita

sarà i1

3

invece con il codice di selezione

11 si abilita la porta di ingresso

numero 3, e quindi all'uscita sarà

disponibile il segnale i3.

2

1

0

0

1

Multiplexer a 4 ingressi

0

0

1

Multiplexer a 4 ingressi

1

Multiplexer a 2 ingressi

In figura è mostrato un mux 2:1 per 2 segnali e 1

variabile di controllo

Multiplexer a 2 ingressi

La funzione di uscita del multiplexer 2-1 vale:

__

u = S i0 + S i1

Se s=0 sull'uscita u viene

posto il valore di i0 , altrimenti

( s = 1) viene posto in uscita il

valore di i1.

Una rappresentazione semplificata

del Multiplexer

esempio

_

I3

I2

I1

I0

s=0 ? s=1 viene posto sull'uscita u il valore i0, altrimenti

se s = 1 viene posto in uscita il valore i1.

Il circuito e' rappresentato nel disegno seguente:

S1 S0

__

u = S i0 + S i1

0

Lo schema semplificato del MUX

evidenzia che la sua struttura è

assimilabile ad un commutatore a

posizioni multiple (selettore); la

posizione dipende dai bit di controllo.

Di seguito è riportata la tabella di verità per un

selettore a 4 ingressi A B C D e 2 linee di

controllo (o selezione) S1 e S0 e la funzione di

uscita Y.

__ __

__

__

Y = S1·S0·A + S1·S0·B + S1·S0·C + S1·S0·D

Ingressi di selezione uscita

S1

S0

Y

0

0

A

0

1

B

1

0

C

1

1

D

2

DEMULTIPLEXER

Il Demultiplexer è un dispositivo

che realizza la funzione inversa del

multiplexer, consiste di:

G

3

Il Demultiplexer attiva solo la linea di uscita

il cui “indirizzo” corrisponde al mintermine

•una linea di ingresso (G),

2

•n linee pure di ingresso (che

fungono da linee di controllo)

s0,s1 e

1

scelto come segnale di controllo.

Pertanto attraverso i segnali di controllo

•2 n linee di uscita (O0,O1,O2,O3)

di cui è attiva una sola per volta.

si sceglie la linea da attivare in uscita.

0

Demultiplexer a 4 uscite

0

1

Demultiplexer a 4 uscite :

DEMULTIPLEXER

Il Demultiplexer viene tipicamente usato come decodificatore.

Demultiplexer a 4 uscite

s0 s1 o0 o1 o2 o3

E’ noto che con n bit è possibile rappresentare 2n diverse

informazioni.

001000

Quindi con un Demultiplexer a n ingressi si può realizzare un

decoder di 2n informazioni

010100

100010

110001

DEMULTIPLEXER come

decodificatore

Se mandiamo in input le combinazioni binarie prefissate le uscite

possono essere utilizzate per la decodifica.

DECODER come generatore di

mintermini

Un decoder con n ingressi e 2 n uscite è di fatto un generatore di

mintermini in quanto realizza i 2 n distinti prodotti di n variabili.

In questo caso con 2 ingressi posso generare 2n combinazioni

quindi posso decodificare ad esempio 2n caratteri.

U0

Ogni uscita corrisponde ad un carattere.

U2

G

Output0

W

W=G•0•0

EN

Output1

X

X=G•0•1

A

B

Output2

Y

Y=G•1•0

Output3

Select0

0

1

U1

Z

Z=G•1•1

Enb

3:8

dec

U3

S2

A

S1

B

S0

2

3

4

5

6

7

ABC

ABC

ABC

ABC

ABC

ABC

ABC

ABC

C

Quando EN=1, vale 1 l’uscita il cui pedice, in decimale, corrisponde al

numero binario in ingresso (A bit di minor peso)

Select1

3

Esempio

Questa caratteristica può essere utilizzata per fare la sintesi

di funzioni.

In figura è riportato un Decoder a 3 ingressi e 8 uscite, ciascuna delle quali

implementa praticamente ognuno dei mintermini di una funzione a tre

variabili .

0

1

Infatti utilizzando un dispositivo di questo genere, che implementa

praticamente ognuno dei mintermini di una funzione , basta posizionare

Enb

3:8

dec

esternamente al decoder una porta OR che

raccoglie tutte le uscite, che restituiscono un 1, in modo

da implementare effettivamente la funzione.

S2

A

S1

B

S0

2

3

4

5

6

7

ABC

ABC

ABC

ABC

ABC

ABC

ABC

ABC

C

Esempio

0

1

Enb

3:8

dec

S2

A

S1

B

S0

2

3

4

5

6

7

ABC

ABC

ABC

ABC

ABC

ABC

ABC

ABC

C

A

0

0

0

0

1

1

1

1

B

0

0

1

1

0

0

1

1

C

0

1

0

1

0

1

0

1

F

0

0

0

1

0

1

1

1

0

1

Enb

3:8

dec

S2

A

S1

B

S0

2

3

4

5

6

7

ABC

ABC

ABC

ABC

ABC

ABC

F

ABC

ABC

C

F = A' B C + A B' C + A B C’ +ABC

Per implementare una particolare funzione basta che posizioniamo

esternamente al decoder una porta OR che raccoglie tutte le uscite relative ai

mintermini pari a 1 della tabella di verità della funzione stessa.

4