LA LOGICA SEQUENZIALE

Quali sono i componenti fondamentali della logica sequenziale?

1

Sono i LATCH (senza e con abilitazione) e i FLIP-PLOP dei vari tipi (JK,

D, T)

Cos'è un latch e perché si chiama così?

2

Un latch è un dispositivo in grado di memorizzare un bit di informazione.

Si chiama latch (catturare) perché è capace di catturare il livello del

segnale d'ingresso e di mantenerlo in memoria

Che differenza c'è fra latch senza abilitazione e con abilitazione?

3

segnale di

sincronismo

Nei primi cambiando le configurazioni attive degli ingressi varierà l'uscita.

Nei secondi si può inibire l'effetto degli ingressi sulle uscite in dipendenza

di un segnale di abilitazione. Se il segnale di abilitazione viene portato a

livello attivo solo in determinati intervalli di tempo, di durata tanto breve da

poterli considerare impulsi istantanei (treno d'impulsi: vedi figura), si

otterrà un dispositivo che potrà cambiare di stato solo in corrispondenza di

tali istanti.

Partendo allora dai latch con abilitazione si potranno ottenere dei circuiti

con funzionamento sincronizzato, in cui cioè il cambiamento di stato delle

diverse uscite avviene su comando di un segnale di sincronismo (clock)

Qual è il simbolo di un latch senza abilitazione?

4

Sono possibili due configurazioni: latch a porte NOR e a porte NAND.

Il primo ha ingressi attivi alti, il secondo ha ingressi attivi bassi.

Il simbolo di entrambi è indicato in figura

Il simbolo pone in evidenza che in un caso gli ingressi S = Set (mandare

ad 1) ed R = Reset (mandare a 0) sono attivi alti, cioè agiscono sull'uscita,

settandola o resettandola, quando sono a livello alto. Nell'altro caso (S, R)

sono attivi bassi.

Il simbolo indica inoltre la presenza di due uscite: una principale, indicata

con Q, e l'altra, complementare alla precedente, indicata con Q

Come viene realizzato un latch a porte NOR? Qual è il suo

funzionamento?

5

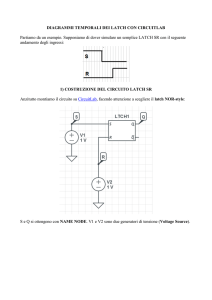

Lo schema utilizzato è quello di figura:

Il comportamento del circuito è quello indicato in tabella:

R

Q

S

0

0

memoria

0

1

0 reset

1

0

1 set

1

1

proibita

1) La configurazione SR=00 (S=0, R=0) è una configurazione di

memoria. Ovvero l'uscita Q mantiene il suo valore.

Supponiamo infatti che sia Q=0 (Q è l'uscita della seconda porta,

quella in basso). Tale valore viene riportato all'ingresso della prima

porta che avendo 00 agli ingressi fornisce Q =1 alla sua uscita. Tale 1

viene riportato all'ingresso della seconda porta, che avendo 01 ai suoi

ingressi conferma il valore 0 alla sua uscita.

Analogo discorso vale se si suppone Q=1.

2) La configurazione SR=01 (S=0,R=1) è la configurazione di reset:

essa cioè porta l'uscita a livello basso.

Si noti infatti che porre un 1 all'ingresso di una NOR forza la sua uscita

a zero (quale che sia l'altro ingresso). Quindi Q=0. Tale 0 viene

riportato all'ingresso della prima porta (quella in alto) che darà un 1

alla sua uscita.

Analogamente si capisce che la configurazione simmetrica della

precedente (SR=10) produrrà uscite simmetriche rispetto al caso

precedente (Q=1, Q=0).

3) La configurazione 10 setta allora il dispositivo, cioè ne porta l'uscita

principale a livello alto.

4) Infine la configurazione SR=11 è una configurazione PROIBITA,

poiché entrambe le uscite Q e Q verrebbero forzate al livello 0, e

quindi non sarebbero l'una complementare dell'altra come richiesto.

Qual è la struttura di un latch a porte NAND? Qual è il suo

funzionamento?

6

latch a porte

NAND

La struttura è analoga a quella del latch a porte NOR, con la differenza

che adesso si utilizzano porte NAND e l'uscita principale Q si prende

sulla prima porta (quella in alto).

Osserviamo la figura.

00=configurazion

e proibita

11=memoria

Come si vede, gli ingressi sono indicati adesso con S, R per

segnalare che sono attivi bassi. Infatti è noto che una NAND se ha

uno dei due ingressi a 0 porta la sua uscita ad 1.

Allora se entrambi gli ingressi sono a 0, entrambe le uscite andranno

ad 1 (e questo è da evitare: configurazione proibita). Se invece uno

solo degli ingressi è a zero l'uscita corrispondente andrà ad 1 (SR=01

sarà allora la configurazione di set, mentre SR=10 sarà la

configurazione di reset)

Infine se entrambi gli ingressi sono disattivi (SR=11) l'uscita manterrà

il suo valore (configurazione di memoria).

Esistono latch SR statici (senza abilitazione) integrati?

7

latch statico

279

Si, esistono, anche se sono poco diffusi perché la loro utilità è limitata.

Il tipo più noto è il 279 che contiene quattro latch statici a porte NOR.

Quale può essere una possibile applicazione del latch statico?

8

antirimbalzo

Può essere il circuito antirimbalzo di un interruttore.

Si consideri un interruttore meccanico S che venga azionato per fornire

corrente ad un carico (figura).

In teoria se l'interruttore viene chiuso all'istante t0, si dovrebbe misurare

sul carico una tensione a gradino. In realtà come mostra la figura,

l'uscita, prima di portarsi al valore di regime, subito dopo t0 presenta

delle oscillazioni che in molti casi possono essere indesiderate.

Per eliminare tale effetto, dovuto ai rimbalzi di S, si può utilizzare un

latch statico con funzione antirimbalzo, come indica la figura:

A riposo l'interruttore si trova in posizione A. Il latch è resettato e

l'uscita è bassa. Portando l'interruttore in posizione B il latch viene

settato e l'uscita si porta a livello alto. Anche se il latch dopo aver

toccato B rimbalza portandosi in una posizione INTERMEDIA fra A e B,

il latch si troverà nella configurazione di memoria (SR=11), per cui

l'uscita si manterrà alta)

Come si può ottenere un latch con abilitazione (gated), partendo

da un latch statico?

9

latch con

abilitazione

E' sufficiente far precedere un latch nand da due porte nand A,B alle

quali si applicano i segnali di set e reset ed un segnale comune di

abilitazione del latch (E=Enable) [vedi

figura].

Si noti che se E=0 le due porte d'ingresso bloccano il passaggio dei

due segnali di comando del dispositivo (S,R), perciò il latch si troverà

nello stato di memoria.

Se viceversa E=1 i due segnali S,R si trasferiranno a valle delle porte

d'ingresso, divenendo S'R'. Tuttavia avranno un valore INVERTITO

rispetto al loro valore di partenza.

Questo significa che la configurazione SR=00 diventerà S'R'=11 dopo

le porte d'ingresso, e poiché la configurazione 11 è la configurazione

di memoria per il latch nand, ne segue che SR=00 è la configurazione

di memoria per il latch con abilitazione.

E=0 stato di

memoria

E=1, SR=00:

memoria

Analogamente la configurazione SR=01 diventerà S'R'=10 a valle

delle porte d'ingresso. Quest'ultima è la configurazione di reset per il

latch nand. Allora SR=01= reset del latch con abilitazione.

La configurazione SR=10 diventerà S'R'=01 (set del latch nand) .

Allora SR=10= configurazione di set.

Infine SR=11 si trasforma in S'R'=00 che è la configurazione proibita

per il latch nand.

Allora SR=11= configurazione proibita.

Riassumendo allora il latch gated con E=1 si comporta esattamente

come un latch NOR (ingressi attivi alti, configurazione proibita SR=11)

E=1, SR=01:

reset

E=1, SR=10: set

E=1, SR=11:

proibita

Quali sono i vantaggi del letch gated rispetto al latch statico?

Può fare qualche esempio?

10

alee

Uno dei vantaggi è quello di consentire l'eliminazione di errori che

nascono nei circuiti in conseguenza dei tempi di commutazione non

nulli dei dispositivi. Tali errori vengono dette ALEE e sono

assolutamente da evitare nella logica sequenziale, perché possono

portare a memorizzare livelli errati di segnale.

Può fare un esempio di circuito in cui si verifica una ALEA?

11

Si consideri il circuito:

In teoria, se il tempo di propagazione di una porta fosse nullo, l'uscita

U del circuito si dovrebbe mantenere sempre a zero, anche dopo che

A passa da livello alto a basso (istante t0). In pratica a causa del

ritardo di propagazione della porta NOT, l'uscita B si porterà dallo

stato basso a quello alto solo dopo il tempo tp. La porta EXNOR (porta

d'eguaglianza) segnala il fatto che durante tp i due ingressi sono

uguali fornendo in tale intervallo un impulso spurio.

Tali impulsi nella logica combinatoria sono generalmente innocui,

viceversa nella logica sequenziale sono generalmente da evitare

perché possono venire memorizzati come stati logici del circuito.

Come è possibile eliminare l'impulso dovuto all'alea servendosi

di un latch con abilitazione?

12

Se il segnale d'uscita del circuito precedente (che presenta una alea in

coincidenza della transizione di A verso il basso) deve servire ad

esempio da segnale di set di un latch NOR (con ingressi attivi attivi

alti), per evitare che il latch venga abilitato dall'impulso di alea, basterà

utilizzare un latch con abilitazione, abilitato un tempo tp dopo che A ha

cambiato di stato.

Può indicare come ottenere un latch D gated?

13

latch D gated

Un latch di tipo D (Data latch) è un latch che riproduce il dato D al

suo ingresso quando è abilitato, mentre mantiene il dato in memoria

quando non è abilitato. Si ottiene dal latch SR gated collegando S

con R mediante una porta NOT, cosicchè adesso se S=1 si avrà R=0

(configurazione di set : se il latch è abilitato l'uscita si porta ad 1),

mentre se S=0 si avrà R=1 (configurazione di reset : se il latch è

abilitato l'uscita si porta a 0). Come si vede se il latch è abilitato

(E=1), l'uscita riproduce l'ingresso. Viceversa se il latch non è abilitato

(E=0) l'uscita permane nel suo stato (memoria)

Può indicare per quale motivo in un registro a scorrimento l'uso

dei latch D gated non è indicato?

14

Si consideri il circuito di figura:

Si desidera che nel caso in cui E sia un segnale ad onda quadra

(clock) ad ogni impulso di clock il dato D=1 si trasferisca da un latch

al successivo, cioè scorra verso destra.

Tuttavia poiché il tempo in cui E=1 è molto maggiore del tempo di

propagazione dei latch, nel circuito precedente (che utilizza latch D

gated) il primo impulso di clock produrrà il trasferimento del dato D=1

non solo all'uscita del primo latch (come si desidera) ma anche

all'uscita dei latch successivi al primo.

Come si passa da un latch SR gated al un flip flop SR?

15

da latch SR gated E' sufficiente aggiungere un circuito in grado di trasformare un'onda

quadra, quale è generalmente il segnale di clock, in un treno

a flip flop

d'impulsi molto stretti e di durata uguale al tempo di propagazione di

una porta. In questo modo nel caso del registro a scorrimento la

durata del segnale di abilitazione sarà sufficiente a far trasferire il

dato solo all'uscita del primo dispositivo, e non all'uscita di tutti gli altri

dispositivi che lo seguono.

Come è possibile trasformare un'onda quadra (segnale di clock)

in un treno d'impulsi?

16

generare impulsi E' sufficiente utilizzare un circuito simile a quello già visto parlando

delle ALEE.

brevissimi

Cioè:

Quando il segnale A passa da basso ad alto, il segnale B passerà da

alto a basso. Tuttavia la transizione di B avverrà un tempo tp dopo la

transizione di A. Durante tale intervallo entrambi i segnali sono alti,

per cui all'uscita della AND si otterrà un impulso di durata tp ( 10

nsec)

In definitiva, qual è lo schema di un flip flop SR, e qual è il suo

simbolo logico?

18

Schema FF SR

Lo schema è rappresentato in figura:

Il simbolo logico è simile a quello del latch SR gated, con la

differenza che il terminale di abilitazione viene chiamato CK (clock)

ed indicato con un triangolino per significare che nel caso del flip flop

sono i FRONTI del segnale di clock che consentono la

commutazione, e non i livelli come avveniva nel latch gated. La

presenza di un circoletto sul terminale di clock indica che il fronte

attivo del clock è quello di DISCESA.

Quali sono i diversi tipi di flip flop?

19

diversi tipi di FF: Sono i flip flop SR, già visto. Il tipo D (Data) che si ottiene collegando

S con R attraverso una NOT: l'arrivo del fronte attivo del clock

tipo D

tipo JK

causerà un trasferimento del dato dall'ingresso all'uscita.

Il tipo JK, che è il più utilizzato. Per ottenere un JK a partire da un FF

di tipo SR è sufficiente la semplice modifica indicata in figura:

Il flip flop JK si comporta come il flip flop SR (J corrisponde al set e K

corrisponde al reset) in tutti i casi tranne nel caso JK=11. In

quest'ultimo caso l'uscita del dispositivo, all'arrivo del fronte attivo del

clock, COMMUTA rispetto al valore che aveva in precedenza

(funzionamento TOGGLE) .

Indichiamo con P1,P2 le due porte d'ingresso, e con P3,P4 quelle di

uscita.

Sia Q=0. Tale valore viene riportato all'ingresso di P2 la quale fornirà

un 1 alla sua uscita. La porta P4 si trova 01 agli ingressi e fornirà 1

alla sua uscita. Tale 1 viene riportato all'ingresso di P1, la quale,

quando arriva il fronte del clock si trova con tre 1 all'ingresso e

fornisce 0 alla sua uscita. La porta P3 dovrà allora presentare un 1

alla sua uscita (transizione da 0 ad 1).

Nel tempo necessario a P3 per passare da 0 ad 1 l'impulso prodotto

dal clock sull'ingresso di abilitazione è ridivenuto basso, per cui P2

porterà la sua uscita a livello alto. Quindi P4 si troverà due 1

all'ingresso e produrrà uno 0 alla sua uscita (transizione da 1 a 0).

Un discorso analogo vale se si suppone che inizialmente sia Q=1.

Allora la configurazione JK=11 provoca, all'arrivo del fronte del clock

un cambiamento di stato dell'uscita.

Qual è il flip flop JK integrato più noto? Quali sono le sue

caratteristiche?

20

FF tipo JK

integrato: 112

E' il 112 che contiene due flip flop JK attivi sul fronte di discesa del

clock (negative edge triggered). Esso possiede inoltre due terminali di

set diretto (preset) e reset diretto delle uscite (clear). Sia il preset che

il clear sono attivi bassi.

Il simbolo di un FF con le caratteristiche precedenti è quello indicato:

Cosa sono i registri a scorrimento?

21

registri a

scorrimento

Un registro è un insieme di celle di memoria che permettono la

memorizzazione di una parola di bit (4 bit=nibble, 8 bit= byte, 16 bit=

word) .

Nei registri a scorrimento i bit possono scorrere verso destra, verso

sinistra o in entrambe le direzioni. Ciò può essere utili nei circuiti di

calcolo. Uno shift a destra equivale infatti ad una divisione per 2. Si

consideri ad esempio il numero 8=(1000)2. Effettuando uno

scorrimento a destra di ogni bit si ottiene : (0100)2=4.

Analogamente uno shift a sinistra equivale a una moltiplicazione per 2.

Un altro uso dei registri a scorrimento è quello di consentire la

trasformazione di un dato da parallelo in seriale. Ad esempio i dati in

uscita da un microprocessore 8088 sono posti in parallelo su 8 piedini.

Volendo trasferirli ad un altro microprocessore può essere conveniente

utilizzare un unico cavo di connessione fra i due micro. In questo caso

per la trasmissione andrà effettuata dapprima una conversione

parallelo seriale (trasmissione) e poi una conversione seriale parallelo

(ricezione).

Com'è possibile realizzare un registro a scorrimento?

22

realizzazione

registro a

scorrimento con

FF tipo D

E' sufficiente porre in cascata n flip flop di tipo D con l'ingresso di clock

posto in comune e collegato al segnale di clock ck (figura)

Supponendo che inizialmente le quattro uscite siano state azzerate, al

primo impulso di clock il dato D si trasferirà su Q0 (la durata

dell'impulso di clock è troppo breve perché succeda che il dato si

trasferisca da Q0 a Q1). Al secondo impulso di ck il dato su Q0 si

trasferirà su Q1, mentre il secondo dato presente su D si trasferirà su

Q0. Al quarto impulso di ck i quattro dati che sono stati posti su D si

saranno trasferiti sulle quattro uscite. A questo punto il nibble che è

stato memorizzato nel registro potrà essere prelevato in modalità

seriale (prelevando un bit alla volta dall'uscita Q3) oppure in modalità

parallela (prelevando i quattro bit contemporaneamente dalle quattro

uscite Q0,Q1,Q2,Q3.

23

inserimento dati

in parallelo

Si è visto che in un registro a scorrimento i dati possono essere

prelevati in parallelo. E' possibile anche inserire i dati in

parallelo?

Si. E' sufficiente utilizzare il circuito di figura:

Come si vede quattro multiplexer a due ingressi consentono di inviare

all'ingresso di ciascun flip flop il nibble in parallelo (P0P1P2P3) oppure le

uscite del flip flop che lo precede. Ciò a seconda del valore di PE:

l'ingresso Parallel Enable consente cioè l'inserimento in parallelo se

PE=1, lo scorrimento dei dati se PE =0.

Oltre ai registri a scorrimento quali sono le applicazioni più

comuni dei flip flop?

24

Sono i contatori asincroni e sincroni. I primi sono ottenuti

semplicemente ponendo in cascata n flip flop in configurazione

TOGGLE (SR=11), i secondi sono invece ottenuti utilizzando i flip flop

D o JK.

Quali sono vantaggi e svantaggi dei contatori asincroni rispetto a

quelli sincroni?

25

contatore

asincrono con FF

tipo toggle

Il contatore asincrono è molto più semplice da progettare.

Ad esempio per un contatore asincrono modulo 8 (che conti cioè da

uno a 7) basterà mettere in cascata tre FF di tipo toggle:

Si noti che si sono utilizzati FF con ingresso di clock attivo sul fronte di

DISCESA. Ciò consente di ottenere un conteggio crescente. Infatti se

si analizzano le tre uscite Q 2Q1Q0 dopo il primo clock valgono 001,

dopo il secondo clock valgono 010, dopo il terzo clock: 011 eccetera.

Si ha cioè un conteggio binario crescente da 0 a 7. Dopo il settimo

impulso di clock il conteggio reinizia da zero (si hanno otto stati diversi

delle uscite: modulo 8).

Se si utilizzano dei FF attivi sul fronte di salita si otterrà un conteggio

decrescente, da 7 a 0.

Un altro modo di ottenere un conteggio decrescente è quello di

utilizzare le uscite NEGATE.

Come è possibile ottenere un contatore asincrono con modulo

qualsiasi ?

26

contatore

asincrono modulo

qualsiasi

Se il modulo è la potenza ennesima di due basteranno n FF toggle in

cascata. Se invece il modulo è qualsiasi (ad esempio m=10) occorrerà

utilizzare un numero n di FF toggle tale che 2n sia la più piccola

potenza di due maggiore di m. Ad esempio con m=10 occorreranno

n=4 flip flop.

Il conteggio andrà arrestato quando il numero binario presente sulle

uscite è uguale al modulo. Cioè tale numero dovrà far ricominciare il

conteggio da zero. Quindi tale configurazione delle uscite dovrà essere

portata ad una porta NAND ad n ingressi e l'uscita di quest'ultima

dovrà essere portata sull'ingresso di reset diretto (che si suppone

attivo basso) dei FF che in quel momento sono alti.

Qual è lo svantaggio dei contatori asincroni?

27

Lo svantaggio è legato al fatto che il ritardo di propagazione tp dei FF

svantaggio

contatori asincroni non consente di ottenere velocità di conteggio molto elevate.

Infatti essendo gli n flip flop in cascata i ritardi di propagazione si

sommano. Quando n tp > Tck sull'ultimo FF si produce un errore

(Tck= periodo del clock). Per ovviare a tale inconveniente si utilizzano i

contatori SINCRONI.

Qual è lo schema di un contatore sincrono (modulo 2n)?

28

Consideriamo la tabella che ci fornisce le uscite di un contatore

modulo 8:

Q2

Q1

Q0

S0

0

0

0

S1

0

0

1

S2

0

1

0

S3

0

1

1

S4

1

0

0

S5

1

0

1

S6

1

1

0

S7

1

1

1

stato

Come si vede

1) Q0 deve variare ad ogni ciclo di clock. Per ottenere ciò è sufficiente

contatore sincrono

connettere un JK in configurazione toggle.

2) Q1 deve variare quando Q0 vale 1. Si può ottenere allora che

quando Q0=1 il FF che fornisce Q1 funzioni da toggle (basta inviare Q0

ai due ingressi JK)

3)Q2 deve variare il proprio stato quando sia Q0 che Q1 valgono 1. Si

può ottenere ciò mandando Q0 e Q1 ad una AND l'uscita della quale

viene mandata agli ingressi JK del FF che fornisce Q2 in modo da

farlo funzionare da toggle.

Si ottiene allora lo schema:

Esiste un metodo per progettare un contatore sincrono con

modulo qualsiasi?

29

contatore sincrono Si. Illustriamo il metodo con un esempio: sia da progettare un

modulo 6: progetto contatore sincrono modulo m=6.

1) Decidiamo anzitutto il numero n di FF da utilizzare. La più

piccola potenza di due maggiore di 6 è 8=23. Quindi n=3:

decidiamo allora di utilizzare 3 FF di tipo JK attivi sul fronte di

tabella stato

discesa.

presente stato

Costruiamo adesso una tabella che riporta lo stato presente, lo

futuro

stato futuro ed i valori che dovranno assumere j,k per passare

dallo stato presente allo stato futuro. Questi ultimi valori li

dedurremo dalla tabella di eccitazione, che fornisce i valori di

J,K per ogni transizione possibile dell'uscita, cioè per ogni

coppia di valori Qn, Qn+1 (Qn=uscita all'istante tn;

Qn+1=uscita all'arrivo del successivo impulso di clock).

tabella di eccitazione

stato

futuro

n ° stato

presente

Q2Q1Q0

Q2Q1Q0 J2K2 J1K1 J0K0

Qn

Qn+1

J

K

0 0

0 0 0 0 1 0x

0x

1x

0

0

0

x

1 0

0 1 0 1 0 0x

1x

x1

0

1

1

x

2 0

1 0 0 1 1 0x

x0

1x

1

0

x

1

3 0

1 1 1 0 0 1x

x1

x1

1

1

x

0

4 1

0 0 1 0 1 x0

0x

1x

5 1

0 1 0 0 0 x1

0x

x1

Per costruire la tabella di eccitazione si ragiona come segue:

per passare da Qn=0 a Qn+1=0 occorre mantenere il JK in stato di

tabella di eccitazione memoria (J=0,K=0) oppure resettarlo (J=0,K=1). Allora occorre

mantenere J=0, mentre il livello di K è indifferente (J=x).

Analogamente per le altre righe.

Per costruire la tabella stato presente, stato futuro , si ragiona

come segue:

1) un contatore modulo 6 che conti in avanti dovrà presentare alle

sue uscite Q2Q1Q0 i seguenti numeri (codificati in binario)

0,1,2,3,4,5,0,1,2,3,4,5….

Quindi l'uscita 0 dovrà essere seguita dall'uscita 1, questa

dall'uscita 2 …, l'uscita 5 dovrà essere seguita dall'uscita 0.

Affinché ciò accada si vede che l'uscita Q2 dovrà subire le

transizioni indicate dalle due colonne in rosso. Tali transizioni sono

possibili se gli ingressi J2K2 assumono i valori indicati (ricavati dalla

tabella di eccitazione).

Si possono adesso costruire le mappe di Karnough per le diverse

variabili:

Q2Q1

Q0

00

01

11

10

Q2 Q1

Q0

00

01

11

10

0

0

0

x

x

0

x

x

x

0

1

0

1

x

x

1

x

x

x

1

J2= Q1Q0

(raggruppando l'1 con lo stato indefinito ad

esso prossimo)

K2=Q0

00

01

11

10

Q2 Q1

Q0

00

01

11

10

0

0

x

x

0

0

x

0

x

x

1

1

x

x

0

1

x

1

x

x

Q2Q1

Q0

J1= Q2 Q0

(raggruppando l'1 con lo stato indefinito ad

esso prossimo)

00

Q2Q1

Q0

01

11

10

K1=Q0

raggruppando lo stato indefinito

Q2Q1Q0=111 con gli altri tre stati sulla

seconda riga

Q2 Q1

Q0

00

01

11

10

0

1

1

1

0

x

x

x

1

x

x

x

1

1

1

1

J0= 1

K0=1

In definitiva lo schema del contatore sincrono modulo 6 è quello

indicato in figura

Dopo aver fatto il progetto di un contatore sincrono utilizzando le

mappe di Karnaugh, c'è qualche controllo da fare?

30

controlli sul

progetto

Si. Occorre controllare in che modo evolva il conteggio nel caso in cui

venga a trovarsi per qualche motivo in uno degli stati indesiderati, che

nel caso del contatore appena visto sono n=6 (Q 2Q1Q0=110) ed n=7

(Q2Q1Q0=111). Guardando il circuito si vede che lo stato successivo

ad n=6 è n=7 (controllare), mentre lo stato successivo ad n=7 è n=0.

Quindi se per qualche motivo il contatore va a finire in uno stato

indesiderato, dopo due od un impulso di clock rientra nello stato di

reset iniziale. Quindi il progetto appena eseguito va bene.

Se fosse accaduto viceversa che il contatore ciclava indefinitamente

fra due o più stati indesiderati il progetto sarebbe stato da rivedere,

imponendo esplicitamente il rientro nel ciclo corretto.