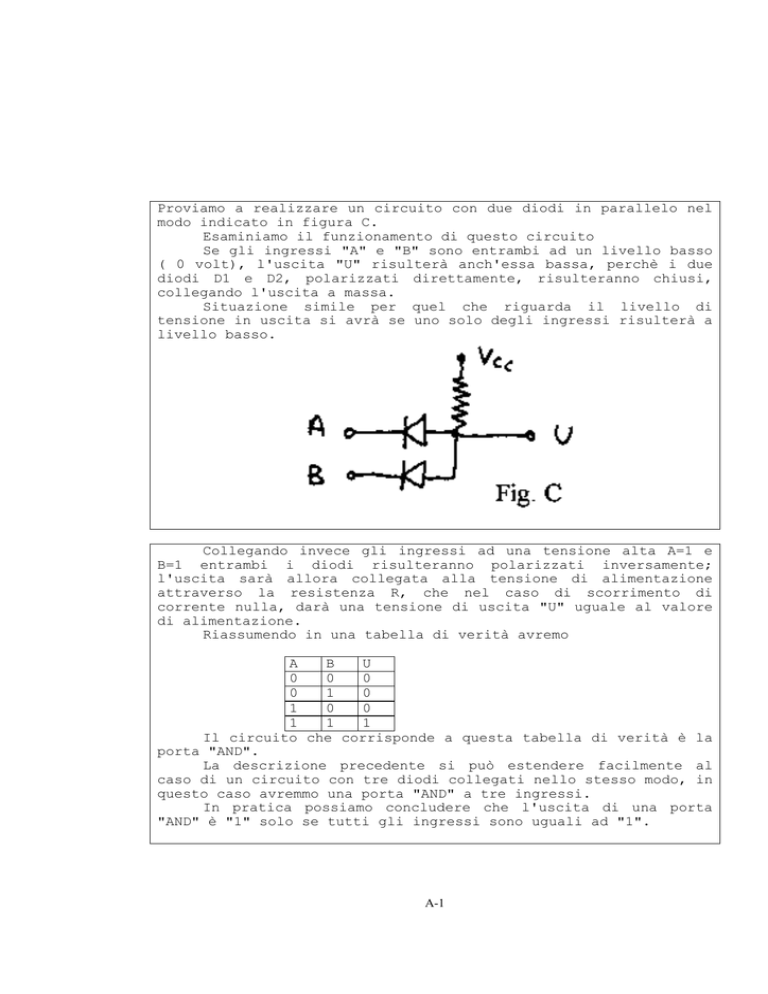

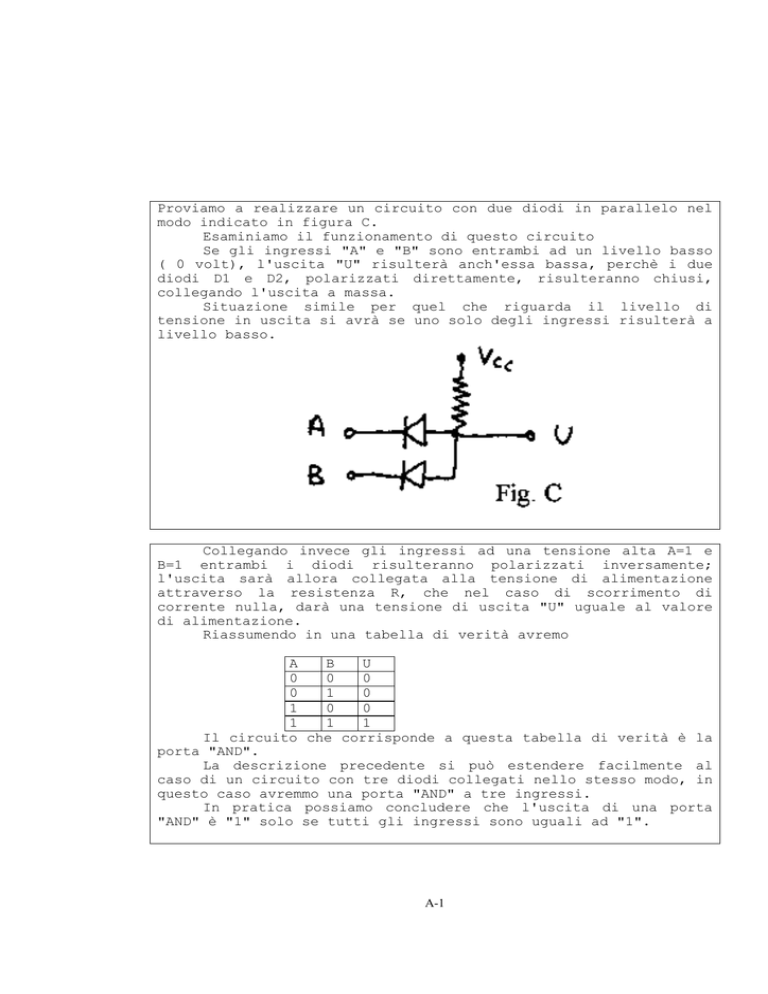

Proviamo a realizzare un circuito con due diodi in parallelo nel

modo indicato in figura C.

Esaminiamo il funzionamento di questo circuito

Se gli ingressi "A" e "B" sono entrambi ad un livello basso

( 0 volt), l'uscita "U" risulterà anch'essa bassa, perchè i due

diodi D1 e D2, polarizzati direttamente, risulteranno chiusi,

collegando l'uscita a massa.

Situazione simile per quel che riguarda il livello di

tensione in uscita si avrà se uno solo degli ingressi risulterà a

livello basso.

Collegando invece gli ingressi ad una tensione alta A=1 e

B=1 entrambi i diodi risulteranno polarizzati inversamente;

l'uscita sarà allora collegata alla tensione di alimentazione

attraverso la resistenza R, che nel caso di scorrimento di

corrente nulla, darà una tensione di uscita "U" uguale al valore

di alimentazione.

Riassumendo in una tabella di verità avremo

A

B

U

0

0

0

0

1

0

1

0

0

1

1

1

Il circuito che corrisponde a questa tabella di verità è la

porta "AND".

La descrizione precedente si può estendere facilmente al

caso di un circuito con tre diodi collegati nello stesso modo, in

questo caso avremmo una porta "AND" a tre ingressi.

In pratica possiamo concludere che l'uscita di una porta

"AND" è "1" solo se tutti gli ingressi sono uguali ad "1".

A-1

FAMIGLIE LOGICHE

CIRCUITI RTL

Proseguendo

con

l'analisi

dei

circuiti

logici,

ci

soffermeremo a descrivere le varie famiglie di circuiti porta

realizzate mediante tecnologia discreta ed integrata.

Iniziamo quindi con la famiglia RTL ( resistor-transistorlogic). Questo tipo di famiglia, non più usata, risulta utile

come aspetto introduttivo alla tecnica elettronica delle porte

logiche. Lo schema elementare di una porta RTL ad "n" ingressi è

data dalla figura 1

Fig. 1

Volendone citare alcune caratteristiche, possiamo dire che

è realizzata mediante "n" transistor NPN i cui emettitori sono

connessi a massa ed i relativi collettori, collegati insieme,

attraverso una sola resistenza R sono collegati ad una tensione

di alimentazione.

Gli ingressi V1, V2.......Vn vengono applicati alle singole basi

attraverso una resistenza Rb.

Esaminiamone il funzionamento:

a)se tutti gli ingressi sono collegati a massa, tutte le basi

risultano anch'esse collegate a massa e quindi tutti gli n

transistor risultano interdetti; la tensione di uscita Vu è

allora uguale alla tensione di alimentazione Vc, cioè per

ingressi tutti "0" uscita "1".

b)se tutti gli ingressi sono connessi ad "1", cioè ad una

tensione di valore praticamente coincidente con la tensione di

alimentazione, tutti i transistor si trovano in zona attiva, in

particolare risultano dimensionati in modo da portarsi in

saturazione e quindi uscita a "0".

c)se ad essere uguale ad "1" è soltanto un solo ingresso, allora

tuttti gli n-1 transistor sono interdetti, mentre l'unico

connesso ad "1" si porta in saturazione e di conseguenza l'uscita

a "0".

A-2

Se lo applichiamo ad un circuito con due soli ingressi,

avremo la tabella S.

Questa corrisponde ad una funzione "NOR"

A

0

0

1

1

TAB

B

0

1

0

1

S

U

1

0

0

0

Quanto detto per il circuito RTL

vale

anche

per

un

circuito

realizzato omettendo le resistenze

di base Rb; in questo caso il

circuito

prende

il

nome

DCTL

(direct-coupled-transistor-logic).

V

cc 0, 7

Ib1

Rc

V

cc 0, 73

I b2

Rc

A-3

Fig. 2

Ib2 Ib1

Si può allora avere una corrente che scorre nella base del

transistor T2 insufficiente a portare lo stesso transistor alla

saturazione, mentre lo porterà soltanto nella regione attiva

diretta.

A causa di questa scarsa affidabilità nel funzionamento,

questo tipo di porta è stato poco utilizzato.

Ritornando alla porta "NOR" realizzata con tecnica RTL

possiamo precisare che la resistenza di base normalmente ha un

valore di circa 450 Ohm mentre la resistenza Rc collegata sui

collettori è di circa 640 Ohm.

Si può anche segnalare un tipo di porta RTL a bassa

dissipazione con valori di resistenza di base di 1,5 KOhm e per

Rc un valore di 3,6 KOhm. Naturalmente per questo tipo di porta

ci si trova con una velocità di commutazione molto più bassa.

La resistenza Rc prende il nome di resistenza di pull-up;

in queste condizioni si ha un pull-up passivo.

Per migliorare le caratteristiche di velocità di una porta

si può utilizzare un circuito di uscita con una resistenza di

pull-up attiva. Con questo sistema si ottiene un aumento della

possibilità di pilotare una capacità connessa in uscita e quindi

una velocità di funzionamento maggiore. Il circuito che realizza

quanto detto è quello indicato in figura 3.

A-4

Fig. 3

Il transistor T2 è la resistenza di pullup attiva. Il transistor T1 è il circuito

invertente per poter pilotare la coppia di

uscita T2 e T3 collegati in controfase.

DIODE TRANSISTOR LOGIC

A-5

Rc 2 K

R 2 K

R b 20 K

A="0"

B="1"

A 0, 2 Volt

valore che corrisponde alla tensione di saturazione dello stadio

precedente e

B Vc

la tensione nel punto M sarà data da

VM VA VD

La corrente che scorre in questo diodo

sarà (se risulta nullo il valore della corrente che fluisce nei

due diodi D3 e D4) data da

ID

V C V D V A 5 0,7 0,2 2 mA

R

2000

Fig. 2

Perché possa passare corrente nei due

diodi e di conseguenza anche nella base

A-6

occorre una tensione nel punto “M” di

almeno 3x0,7=2,1 V

l'uscita "U" è uguale a Vc e quindi "1".

Poniamo ora in ingresso

A="0"

B="0"

anche in queste condizioni il transistor risulta interdetto e

quindi uscita uguale a "1"; infatti il punto "M" si porta ad una

tensione molto simile a quella del caso precedente: quindi

seguono considerazioni analoghe.

Vediamo ora il caso in cui

A="1"

B="1"

Analiticamente avremo infatti che:

Ib IM Ih

la tensione sulla base del transistor Vb sarà

Vb 0, 7 Volt

Ih

0,7 2

0,14 mA

20000

Il valore della tensione nel punto "M" sarà

dato da da

VM VD3 VD4 Vb 0, 7 0, 7 0, 7 2,1 Volt

la corrente nei due diodi è la stessa che fluisce

in R e , in particolare risulta uguale a:

Im

VC VM 5 2 ,1 1, 45 mA

R

2000

l'effettiva corrente che scorre

transistor è invece data da

nella

base

del

Ib IM Ih 1, 45 0,14 1, 31 mA

valore

più

che

sufficiente

a

portarlo

in

saturazione; infatti nel nostro caso, ammettendo

una tensione di saturazione di 0,2 Volt, si ha:

A-7

Icsat

VC Vcesat 5 0, 2 2, 4 mA

2000

Rc

assumendo un guadagno di corrente di 50 occorre per

la saturazione un valore di base dato da

Ib

IC 2, 4 0, 048 mA

hFE 50

nel nostro caso la corrente di base che abbiamo è di 1,31 mA,

circa 27 volte più grande, possiamo quindi concludere che si ha

non solo la saturazione, ma addirittura un valore di tensione

Vcesat di saturazione abbastanza basso (dell'ordine di 0,1 Volt).

La presenza di una resistenza Rb connessa ad una tensione

negativa di 2 Volt permette uno scarico più rapido delle cariche

memorizzate nella base del transistor.

Riassumendo, c'è da dire che la porta DTL qui analizzata

realizza una funzione logica del tipo "NAND".

Prima di passare ad un esame delle varie famiglie logiche

definiamo alcuni

dei parametri comuni a tutti gli integrati

logici.

- VIH (min)Rappresenta

il

valore

minimo della tensione di uscita, della

porta che sta a monte, che viene

riconosciuto come valore di tensione di

ingresso a livello “ALTO”.

- VIL (max) -Rappresenta

il

più

alto

valore di tensione presente in ingresso

riconosciuto come livello “BASSO”.

- VOH (min) Rappresenta

il

valore

minimo

della

tensione

d'uscita

a

livello

“ALTO”.E'

il

livello

di

tensione in uscita corrispondente al

livello logico "1".

A-8

- VOL (max) Rappresenta il valore

massimo

della

tensione

d'uscita

a

livello “BASSO”. E' il livello di

tensione in uscita corrispondente al

livello logico "0".

-IIH - Rappresenta il valore della

corrente d'ingresso corrispondente al

livello alto. E' il valore che fluisce

in un ingresso allorchè viene applicato

un livello di tensione alto.

-IIL - Rappresenta il valore della

corrente d'ingresso corrispondente al

livello basso. In pratica è il valore

di corrente che fluisce in un ingresso

allorchè viene applicato in ingresso un

livello di tensione basso.

-IOH - Rappresenta il valore della

corrente di uscita corrispondente al

livello alto. In pratica è il valore

della corrente che fluisce da una

uscita che si trova nello stato alto.

-IOL- Rappresenta il valore della

corrente di uscita corrispondente al livello alto. In

pratica è il valore della corrente che fluisce da una uscita che

si trova nello stato alto.

"tempo di ritardo di

A-9

- t PLH : ritardo nel passare dallo stato

logico "0" allo stato logico "1" (da BASSO

ad ALTO)

- t PHL : ritardo nel passare dallo stato

logico "1" allo stato logico "0" (da ALTO a

BASSO )

Due esempi sono riportati in figura 6

Questi tempi sono caratteristiche di

ogni famiglia logica.

FAN-OUT

Il

fan-out

è

definito

come

il

massimo numero di ingressi logici della

stessa famiglia che un'uscita è in

grado di pilotare in modo affidabile.

"immunità al rumore".

"Margine di rumore";

una sua rappresentazione grafica è indicata in figura 7

A-10

Fig. 7

In essa vediamo il diagramma delle tensioni possibili in

uscita da un circuito logico. Un valore di tensione maggiore di

V OHm

viene considerata dal circuito logico come un

livello "1" mentre un valore di tensione inferiore a

V OLM

viene considerato dal circuito logico come un livello logico "0".

Tutte

le

tensioni

comprese

in

questo

intervallo

detto

"indeterminato" non dovrebbero, in condizioni normali, comparire

all'uscita di un circuito logico.

Nella figura vediamo l'andamento, in entrata, delle

tensioni in ingresso ad un circuito logico. Un valore di tensione

superiore a

V IHm

è considerato dal circuito come un valore di

V

"1" logico, mentre valori di tensione minori di

sono dal

ILM

circuito viste come livello logico "0". Tutti i valori compresi

in questo intervallo determinano in uscita una risposta

imprevedibile per cui non devono mai essere utilizzate.

Si possono allora definire due margini di rumore uno

relativo al livello alto ed uno al livello basso.

Il margine di rumore nello stato alto

V

V NH V OHm V IHm

NH

è definito come

questo è il valore corrispondente alla differenza fra il

minimo valore possibile di una uscita ALTA e la minima tensione

A-11

d'ingresso richiesta per un un riconoscimento sicuro di livello

ALTO. Quando un livello logico di uscita "ALTO" pilota l'ingresso

di una porta logica la presenza di impulso di tensione di rumore

negativo che si sovrappone al livello d'uscita di ampiezza

maggiore del valore corrispondente al margine di rumore può

causare la discesa della tensione nella zona di tensione

indeterminata e quindi non si ha più un funzionamento garantito.

Il margine di rumore nello stato basso

è definito come

NL

V

V NL V ILM V OLM

PORTE

TTL

Fig. 1

Poniamo l'ingresso al valore "0": la giunzione baseemettitore di T1 viene polarizzata direttamente-fluisce una

corrente di base Ib1, una corrente di emettitore e, di

conseguenza, anche una corrente di collettore Ic1 che scaricherà

a terra, con una resistenza molto bassa, le cariche memorizzate

nella base del transistor T2.

Per avere una valutazione quantitativa osserviamo che nel

caso della porta DTL la scarica delle cariche di base del

transistor di uscita avviene solo attraverso la Rb perchè il

diodo D3 risulta interdetto; in particolare, il valore di questa

corrente sarà:

A-12

Fig. 2

dell'uscita dal valore "0" al valore "1" rallentato dalla

necessità di dover caricare la capacità con una costante di tempo

Fig. 3

Il tipo base di questa famiglia è una porta "NAND".

Tracciamo una caratteristica ingresso-uscita.

A-13

I vari costruttori individuano la loro produzione

con una lettera iniziale SN per la Texas, DM per la

National Semiconductor ad esempio.

Il numero che individua il circuito logico invece

sarà uguale per tutti i costruttori. Della famiglia

TTL ne sono state sviluppate nel tempo numerose

versioni ciascuna con caratteristiche particolari

(74LS, 74S, 74L ecc.).

Per effettuare quest'analisi ci riferiamo al

data sheet relativo ad una porta logica, ad esempio

la 7400 ( una quadrupla porta Nand a due ingressi).

In questo data sheet possiamo evidenziare tutte

le caratteristiche operative elettriche e di

commutazione nonchè i limiti massimi da non

superare senza danneggiare il circuito integrato.

La tensione di alimentazione nominale è di " 5

Volt". Tuttavia occorre anche sapere i limiti

accettabili per il valore della tensione di

alimentazione: La serie 74 ha un intervallo di 4,75

- 5,25 Volt, mentre per la serie 54 questi limiti

vanno da 4,5 - 5,5 Volt; per la temperatura di

funzionamento abbiamo invece 0 - 70 °C per la serie

74 mentre avremo -55 - +125 °C per la serie 54.

Ovviamente la serie 54 sarà più costosa e quindi

sarà riservata ad applicazioni che ne giustifichino

il maggior costo, ad esempio applicazioni militari.

Dal data sheet vediamo che il livello di

tensione massimo di uscita a livello basso è di 0,4

volt mentre il massimo valore di ingresso è di 0,8

volt, quindi volendo calcolare il margine di rumore

basso sarà

V

NL

VIL (max) VOL (max)

0,8 0, 4 400 mV

Allo stesso modo possiamo determinare il margine di

rumore alto

P

D

( med ) ICC ( med ) VCC 8 5 40 mW

A-14

questo valore è relativo al consumo di tutto

il circuito integrato, che nel caso in esame

trattasi di quattro porte, pertando il

consumo medio di ogni porta sarà di 10 mW.

I due ritardi di propagazione sono

propagazione "basso-alto" =11 nsec

propagazione "alto-basso" = 7 nsec

propagazione medio = 9 nsec

Gli integrati TTL della serie standard

comprendono numerosi tipi di porte, flipflop, one-shot, registri a scorrimento,

contatori ecc.

serie 74L, che pur avendo lo stesso circuito

fondamentale della serie standard 1 mW

contro i 10 della serie standard presenta un

ritardo di propagazione medio di 33 nsec

invece dei 9 nsec della serie standard.

La serie 74S per ridurre i tempi di

commutazione è realizzata evitando che i

transistori si portino in una zona di

saturazione spinta. Per ottenere questo

viene utilizzato un diodo Schottky

A-15

collegato fra la base ed il collettore di

ciascun transistor, come si vede in figura

8.

Fig. 8

Questo diodo ha una tensione diretta di

soli 0,25 Volt.

Allorchè

la

giunzione

base-collettore viene ad essere polarizzata

in modo diretto, il diodo posto in parallelo

viene anch'esso polarizzato in modo diretto

e quindi entra in conduzione deviando parte

della corrente di base; questa riduzione

della corrente di base impedisce l'entrata

del transistor in saturazione profonda e

quindi fa diminuire il ritardo dovuto al

tempo di immagazzinamento per passare dallo

stato ON a quello OFF.

Sempre per migliorare la velocità di

commutazione queste porte impiegano dei

valori

resistivi

più

piccoli

portando

inevitabilmente

ad

un

aumento

della

dissipazione di potenza, infatti avremo un

valore di 20 mW di dissipazione per porta.

A-16

TAB.

X

Parametri

74

ritardo

prop.

(nsec)

dissip

pot.

(mW)

prod.vel-pot

(pJ)

freq.

clock

(Mhz)

fan-out

Voh(min)

Vol(max)

Vih(min)

Vil(max)

9

74L 74H 74S 74L 74A 74A

S

S

LS

33 6

3

9,5 1,7 4

10

1

23

90

33

138 60

35

3

50

10

2,4

0,4

2

0,8

20

2,4

0,4

2

0,7

10

2,4

0,4

2

0,8

20

2

8

19

125 45

13, 4,8

6

200 70

20

2,7

0,5

2

0,8

40

2,5

0,5

2

0,8

20

2,7

0,5

2

0,8

1,2

20

2,5

0,4

2

0,8

In un circuito o sistema digitale di

notevole complessità ci possono essere molte

uscite

che

commutano

contemporaneamente

determinando un assorbimento impulsivo di

corrente. La somma di questi impulsi di

corrente determina una caduta impulsiva di

tensione sulla linea di alimentazione

condensatori ceramici a disco di capacità

compresa da 0,01 mF o 0,1 mF di bassa

induttanza

vicino

ad

ogni

circuito

integrato. Occorre sempre ridurre a valori

piccoli la lunghezza dei terminali di tali

condensatori.

"collettore aperto" ed a "drain aperto"

rispettivamente.

Nel caso dei circuiti logici c'è anche la

possibilità di avere un terzo stato logico.

Avremo allora "ALTO" , "BASSO" , "ALTA

IMPEDENZA" (Hi-Z).

Quest'ultima

condizione

si

ottiene

portando

i

due

transistori

della

configurazione totem nello stato OFF

A-17

In figura 14 è indicato un esempio di

circuito invertitore con l'aggiunta della

circuiteria per ottenere il funzionamento

anche three-state. Si aggiunge perciò il

comando "E" detto “enable” che serve a

produrre lo stato Hi-Z.

A-18

FAMIGLIA

ECL

Fig. 1

I due livelli

sono dati da

di

tensione

di

V 1log ico 0,76 Volt

O

, Volt

V 0 log ico 158

O

A-19

uscita

Fig. 2

FAMIGLIA CMOS

E' realizzato utilizzando un transistor

NMOS

come

driver

ed

un

dispositivo

utilizzato come carico, che può essere

generico.

Il circuito risulta molto semplice, la

complessità

dell'analisi

deriva

dalle

caratteristiche

del

carico

adoperato.

L'importanza dell'analisi dell'inverter è

legata al fatto che questo è la base di ogni

circuito digitale comunque complesso.

A-20

Fig. 1

Il

nodo

di

uscita

è

collegato

all'ingresso

di

un

altro

driver

che

rappresenta la porta posta in cascata; per

approssimare il comportamento dell'uscita

inseriamo un condensatore che sintetizza

genericamente il carico

Il

circuito

fondamentale

di

un

invertitore CMOS è indicato in figura 10

Vdd

Vi

Vu

Gnd

Fig. 10

Nella famiglia CMOS ci sono diverse

serie.

Le prima serie di cmos sono state

introdotte dalla RCA e dalla Motorola con la

famiglia 4000A e MC14000, più tardi è stata

introdotta la serie 4000B che con l'uso di

un buffer consentiva una maggiore corrente

A-21

di uscita. Questa serie continua ad essere

molto utilizzata e molte funzioni si trovano

realizzate solo in questa serie.

Una serie successiva è stata la 74C, che

era del tutto compatibile, a livello di pin

e di funzioni, con la serie TTL (con sigla

equivalente).

Più recente è invece la serie 74HC (cmos

ad alta velocità).

Per quel che riguarda la tensione di

alimentazione le due serie 4000 e 74C

richiedono un valore di tensione compreso

fra 3 e 15 Volt. La serie 74HC e 74HCT

invece richiede una tensione compresa fra 2

e 6 Volt.

I livelli delle tensioni di uscita

coincidono

quasi

con

i

livelli

delle

tensioni di alimentazione, cioè "0" a valore

molto vicino a zero volt, e "1" di valore

molto

prossimo

alla

tensione

di

alimentazione.

Nelle porte CMOS anche il margine di

rumore si mantiene ad un livello alto, in

particolare

raggiunge

un

valore

corrispondente al 30% della tensione di

alimentazione, sia per il valore alto che

per

quello

basso.

questo

valore

è

sostanzialmente più alto di quello relativo

alle porte TTL. Ovviamente questo margine

aumenta con l'aumento della tensione di

alimentazione, tuttavia questo aumento si

otterrebbe

a

danno

di

una

maggiore

dissipazione di potenza.

Il valore di questa dissipazione nel caso

statico si aggira attorno ai 2,5 nW nel caso

di una tensione di alimentazione di 5 Volt.

A-22

Con una tensione di alimentazione doppia di

10 Volt avremo una dissipazione quattro

volte maggiore, cioè 10 nW

(questo consumo

si riferisce ad ogni singola porta logica).

Purtroppo un aumento della frequenza di funzionamento della

porta, causa un aumento della potenza dissipata.

Questo aumento è proporzionale alla frequenza con cui avvengono

le commutazioni. Indicativamente possiamo dire che per una

frequenza di funzionamento di 100 KHz si ha una dissipazione di

0,1 mW che si porta a 1 mW per una frequenza di lavoro di 1 Mhz.

La causa di questo comportamento è legata a due fattori:

a) la non contemporanea commutazione dei due mosfet ( i due

transistor durante una commutazione passano uno dallo stato ON ad

OFF e l'altro dallo stato OFF a quello ON.

b) la presenza di capacità collegate in uscita dovute al carico

costituito dalle capacità di ingresso delle altre porte collegate

in uscita e dalla capacità di uscita propria del dispositivo.

Queste vanno caricate durante la commutazione dal livello basso a

quello alto.

.

Si ha infatti un consumo praticamente

coincidente con una porta 74LS già con una

frequenza di circa 2-3 Mhz.

Tuttavia per circuiti complessi occorre

valutare bene questa situazione.

Anche la dimensione del substrato è

diminuita di un terzo (da 120 micron a 45

micron per la RCA). Considerando le capacità

di un inverter CMOS si avrà il circuito di

figura 16 rappresentante tutte le capacità

che interessano l'eventuale utilizzazione

del componente; nella tabella successiva è

invece indicato il valore di tutte queste

capacità

confrontate

con

quelle

di

un

dispositivo CMOS non HC.

Come si vede le capacità sono ridotte.

La

combinazione

di

due

effetti,

miglioramento

medio

di

2

volte

delle

capacità associate al dispositivo ed un

aumento

di

5

volte

nel

guadagno

dei

transistor ha permesso un miglioramento

A-23

totale di 10

dispositivo.

volte

nella

C1

C2

C3

C4

C5

velocità

CMOS

pF

0,25

0,12

0,37

0,66

0,54

del

HC

pF

0,1

0,05

0,15

0,31

0,22

Fig. 16

In un 74LS00 ci sono 4 porte NAND a due

ingressi ed in DC assorbono corrente tutte e

quattro; in un HC00 se utilizziamo una sola

porta soltantc questa assorbirà potenza, le

altre teoricamente no.

Dal grafico vediamo che confrontando il

consumo di corrente relativo ai due tipi di

porta il punto di incrocio si ha attorno ad

una frequenza di circa 3Mhz, a 4 Mhz

sembrerebbe migliore la porta LS. Se però

consideriamo la reale situazione ( cioè che

le 3 porte LS non utilizzate consumano

potenza) il punto di incrocio sale a 10 Mhz

A questo punto si è tentati di dire che

se nei due circuiti integrati funzionano

tutte e 4 le porte allora il vantaggio

diminuisce

(

e

come

dire

che

se

la

complessità del circuito aumenta il punto di

incrocio si abbassa ). Il fenomeno è già

palese

se

consideriamo

non

una

porta

semplice ma un circuito più complesso ad es.

un FLIP-FLOP il punto di incontro si ha

verso i 9 Mhz.

A-24

Per un circuito complesso la situazione

migliora a vantaggio dell'HC.

Un esempio che chiarisce quanto detto può

essere un CONTATORE che divide in ogni

stadio per due un segnale di clock, presente

in ingresso.

La resistenza di ingresso di una porta

Cmos ha un valore elevato che praticamente

porta a dire che la corrente assorbita è

praticamente nulla, si potrebbe dire che il

fan-out potrebbe essere altissimo. Occorre

però tenere presente che l'ingresso di una

porta presenta una capacità dell'ordine di 5

pF verso massa. Questa capacità limita il

numero degli ingressi

che può pilotare

l'uscita di una porta.

In pratica l'uscita della porta deve

caricare e scaricare la capacità costituita

dal parallelo di tutte le capacità

Ogni porta posta come carico provoca un

aumento del tempo di circa 3 nsec. Il fanout quindi infine è determinato dal massimo

tempo di ritardo di propagazione che si

vuole avere. Valore tipico,come già visto,

è di 50 porte.

Gli ingressi di una porta CMOS non vanno

mai

lasciati

sconnessi.

Bisogna

cioè

collegarli ad un livello ben definito, alto

o basso

Un valore elevato di resistenza di

ingresso consente l'acquisizione di cariche

statiche che possono produrre delle tensioni

elevate in grado di perforare l'isolamento

del dielettrico tra la porta e il canale.

A-25

Occorre adottare delle precauzioni nel

maneggiarli.

Le ultime serie di questi dispositivi

Cmos vengono realizzati con delle protezioni

contro

il

pericolo

di

queste

cariche

elettrostatiche; vengono inseriti dei diodi.

La potenza dissipata da un circuito CMOS

nel caso di staticità del livello di uscita

è quella che normalmente viene indicata come

potenza dissipata a riposo; questo tipo di

potenza

nel

caso

delle

porte

CMOS

è

veramente molto piccola.

Il circuito CMOS consuma della potenza

soltanto durante la commutazione Una formula

indicativa è la seguente

PT CPD VDD f

2

dove il valore della potenza sarà quello

dissipato

all'interno

e

dovuto

alla

transiszione dell'uscita.

V è la tensione di alimentazione

f è la frequenza con cui si ripetono le

transizioni di livello

C è un valore capacitivo che rappresenta una

costante fornita dal costruttore che non

rappresenta la capacità di uscita. Per un

circuito CMOS della serie HC ha un valore di

circa 24 pF.

A-26