INTEGRAZIONE conseguenze e vantaggi:

Meno peso ,meno ingombro dei dispositivi ,minor costo vantaggi fisici

Minori R,C,L parassite ,miglior matching (soprattutto per le tecnologie planari)

Meno potenza dissipata e meno capacità parassite che danno dissipazioni di potenze dinamiche ,che così

sono limitate

Maggior affidabilità e qualità dei prodotti, tali valori vanno di pari passo con l’omogeneità dei materiali

nelle strutture, la presenza di piste , di interfacce tra materiali rendono più eterogenei componenti ,nella

miniaturizzazione ho saldature limitate (wire-bonding), e assenza di piste,e quindi è migliore.

Più difficile la copiatura dei circuiti miniaturizzati

Schrinking: tecnica che consiste nel miniaturizzare il dispositivo fino alle dimensioni oltre le quali esso non

funziona più , quindi fino alla dimensione limite. Diminuendo le dimensioni del chip ,aumenta il loro numero

a parità del costo della fetta e aumenta la resa perchè più piccolo è e meno probabile è la presenza di difetti.

Scaling Down:Modifica più drastica, non si limita a una diminuzione proporzionale delle dimensioni del

chip, ma a dimensioni qualsiasi ,a drogaggi , a profondità , e altri particolari

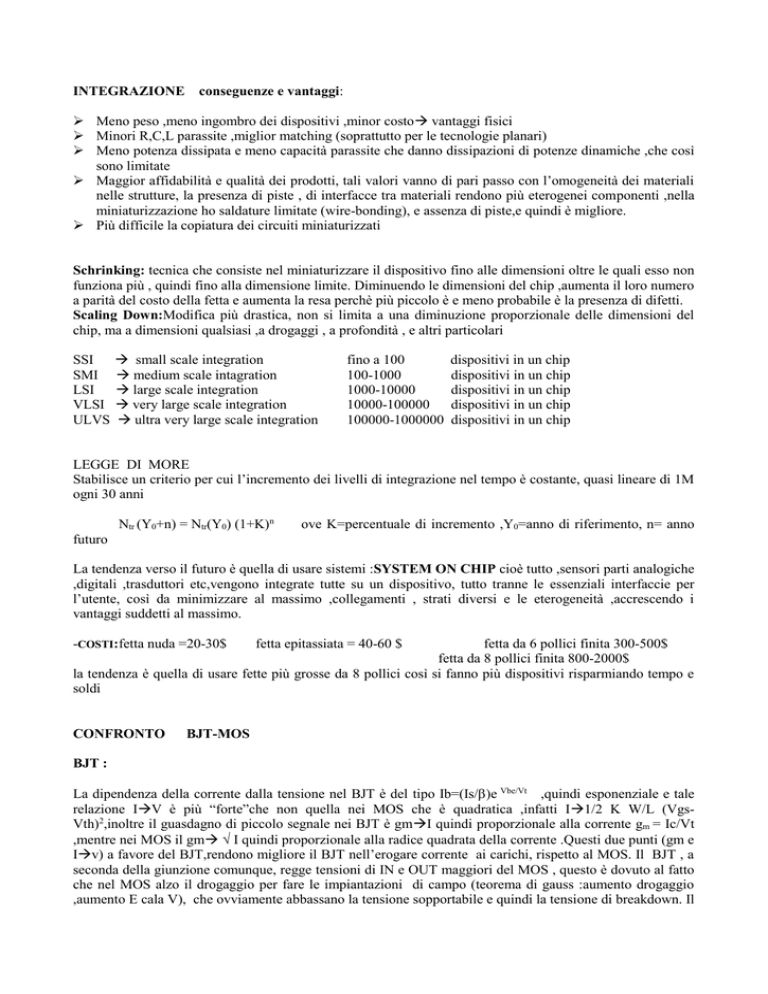

SSI

SMI

LSI

VLSI

ULVS

small scale integration

medium scale intagration

large scale integration

very large scale integration

ultra very large scale integration

fino a 100

100-1000

1000-10000

10000-100000

100000-1000000

dispositivi in un chip

dispositivi in un chip

dispositivi in un chip

dispositivi in un chip

dispositivi in un chip

LEGGE DI MORE

Stabilisce un criterio per cui l’incremento dei livelli di integrazione nel tempo è costante, quasi lineare di 1M

ogni 30 anni

Ntr (Y0+n) = Ntr(Y0) (1+K)n

ove K=percentuale di incremento ,Y0=anno di riferimento, n= anno

futuro

La tendenza verso il futuro è quella di usare sistemi :SYSTEM ON CHIP cioè tutto ,sensori parti analogiche

,digitali ,trasduttori etc,vengono integrate tutte su un dispositivo, tutto tranne le essenziali interfaccie per

l’utente, così da minimizzare al massimo ,collegamenti , strati diversi e le eterogeneità ,accrescendo i

vantaggi suddetti al massimo.

-COSTI:fetta nuda =20-30$

fetta da 6 pollici finita 300-500$

fetta da 8 pollici finita 800-2000$

la tendenza è quella di usare fette più grosse da 8 pollici così si fanno più dispositivi risparmiando tempo e

soldi

CONFRONTO

fetta epitassiata = 40-60 $

BJT-MOS

BJT :

La dipendenza della corrente dalla tensione nel BJT è del tipo Ib=(Is/)e Vbe/Vt ,quindi esponenziale e tale

relazione IV è più “forte”che non quella nei MOS che è quadratica ,infatti I1/2 K W/L (VgsVth)2,inoltre il guasdagno di piccolo segnale nei BJT è gmI quindi proporzionale alla corrente gm = Ic/Vt

,mentre nei MOS il gm I quindi proporzionale alla radice quadrata della corrente .Questi due punti (gm e

Iv) a favore del BJT,rendono migliore il BJT nell’erogare corrente ai carichi, rispetto al MOS. Il BJT , a

seconda della giunzione comunque, regge tensioni di IN e OUT maggiori del MOS , questo è dovuto al fatto

che nel MOS alzo il drogaggio per fare le impiantazioni di campo (teorema di gauss :aumento drogaggio

,aumento E cala V), che ovviamente abbassano la tensione sopportabile e quindi la tensione di breakdown. Il

BJT quindi , eroga correnti più alte e sopporta in ingresso e uscita tensioni più alte. Tali caratteristiche lo

rendono ottimale per lavorare in alta potenza (W=I V).

Il BJT lavora in genere a struttura verticale ,in BULK, zona della fetta che non presentale imperfezioni , le

trappole , gli stati energetici parassiti ,che invece sono in superficie , e quindi , quando lavora in segnale, da

meno rumore, al contrario del MOS che lavorando in tecnologia planare, subisce queste imperfezioni della

fetta e risulta più rumoroso.

La dipendenza esponenziale della corrente rispetto alla tensione fa sì che la Vbe possa essere presa come

riferimento di potenziale per tutto il circuito. Infatti la relazione esponenziale fa si che per variazioni in alti

valori di I , la Vbe resti sempre costante a 0.6 0.7 V. La Vgs nei MOS non può essere un riferimento perchè

varia per qualsiasi variazione di Id ,infatti si ha :

Vg=Vth (I/(K/2 W/L)) che è una relazione quadratica ,senza asintoti per la tensione , e quindi varia molto

al variare di Id

Infine poichè i BJT hanno gm più elevato e consumano potenza statica , lavorano a banda più larga e quindi

sono più veloci dei MOS.

MOS :

Il vantaggio più vincente dei MOS è la loro altissima impedenza di ingresso (tra gate e source).Questo vuole

dire che il MOS-fet non assorbe corrente (e quindi potenza) finchè non viene attivato o commutato ,in pratica

non dissipa potenza statica (ma solo dinamica alle commutazioni). Nelle memorie ,il dato è immagazzinato

come carica sulle piastre di un condensatore ,il MOS è ottimo per leggere il dato in gate ,perchè avendo

impedenza bassa non scarica il condensatore e non distrugge il dato. Il BJT assorbe corrente di base secondo

la legge esponenziale precedentemente vista, quindi non può essere adibito a tale scopo. Il mos nei C-MOS

usati in digitale sono ottimi, perchè non dissipano potenza statica , non consumano corrente quando le porte

sono inattive (fatta eccezione per la Is ,corrente di saturazione inversa), e dissipano una potenza dinamica

,solo in commutazione di stato ,minimizzabile (Pd=CfV2dd).

Benchè gli N-MOS hanno una struttura più compatta (non hanno WELL dei MOS e le strutture cilindriche di

isolamento dei BJT), benchè i BJT abbiano tutti i vantaggi suddetti (velocità ,erogazioni etc) i MOS danno

vantaggi in potenza ineguagliabili ,che li rendono decisamente i più usati e i migliori , soprattutto negli

utilizzi in digitale .

-DIGITALE :in tale applicazione la tecnologia più usata è senz’altro la MOS in quanto sono richiesti bassi

consumi di potenza. Per applicazioni in digitale dove è importante la velocità e non la potenza , si usa la ECL

(emitter coupled logic), fatta di BJT che sono più rapidi in commutazione ( a scapito della potenza dissipata)

infatti . V/ t = I / C= costante ,per cui a parità di I/C abbassando la V il t cala ed è più veloce.

-ANALOGICO: a meno di necessità particolari per compattezza e velocità uso di norma i MOS C-MOS

per rumori ridotti uso BJT.

-il MOS da anche ottimi INTERRUTTURI ,cioè da R basse quando è acceso e R alte quando spento, con i

BJT si hanno problemi di offset fastidiosi per il funzionamento di switch.

-i MOS nelle commutazioni o nei segnali danno step molto secchi e precisi.

Tecnologie miste Bi-CMOS uso BJT e C-MOS sulla stessa piastrina.

In generale si usano 15 20 maschere, con le tecnologie miste sono molte di più.