Transistore a effetto di campo (Field Effect Transistor, FET)

I FET sono dispositivi a semiconduttore a tre terminali che vengono usati

estensivamente nei circuiti analogici e digitali. Tali dispositivi

appartengono a due categorie principali: i MOSFET (Metal Oxide

Semiconductor FET, cioè FET a gate isolato) e i JFET (Junction FET,

cioè FET a giunzione).

Un’importante caratteristica del FET consiste nel fatto che questo è spesso

più facile da fabbricare e occupa meno spazio su un circuito integrato

rispetto ad un BJT. La densità di componenti che si ottiene in tal modo può

essere estremamente elevata. Inoltre, i MOSFET possono essere collegati

in modo da svolgere le funzioni di una resistenza o di un condensatore. E’

così possibile progettare interi sistemi elettronici composti esclusivamente

da questi transistori, senza che sia necessario ricorrere ad altri componenti.

Queste proprietà fanno del MOSFET il dispositivo dominante nei sistemi a

larghissima scala d’integrazione (VLSI).

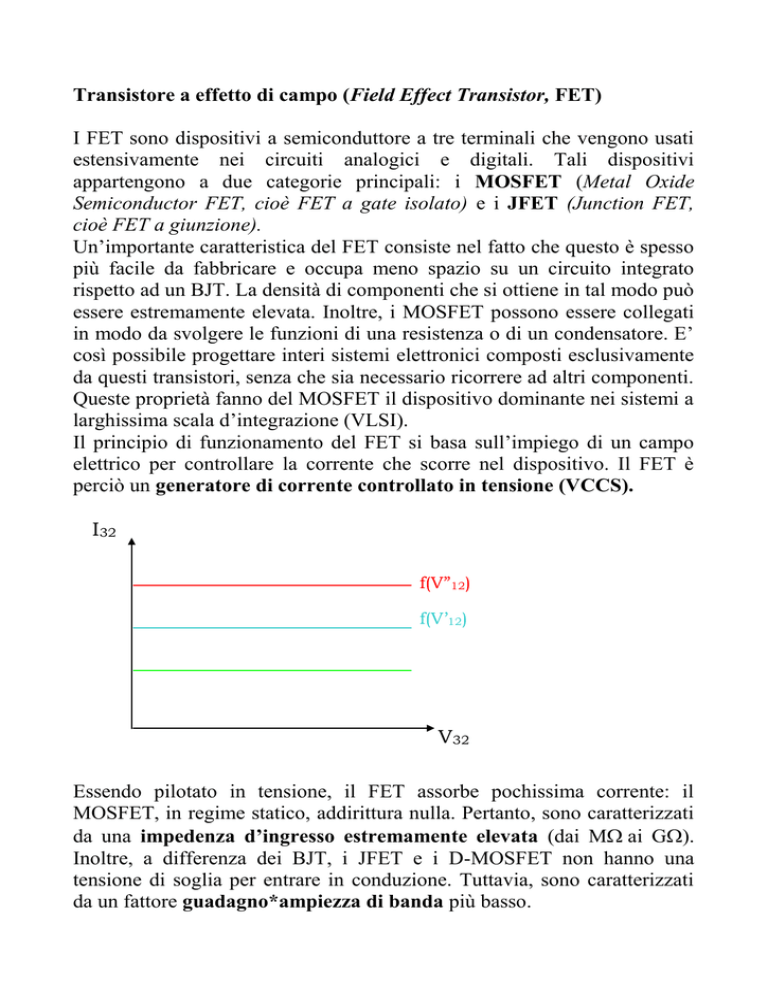

Il principio di funzionamento del FET si basa sull’impiego di un campo

elettrico per controllare la corrente che scorre nel dispositivo. Il FET è

perciò un generatore di corrente controllato in tensione (VCCS).

I32

f(V”12)

f(V’12)

V32

Essendo pilotato in tensione, il FET assorbe pochissima corrente: il

MOSFET, in regime statico, addirittura nulla. Pertanto, sono caratterizzati

da una impedenza d’ingresso estremamente elevata (dai Mai G).

Inoltre, a differenza dei BJT, i JFET e i D-MOSFET non hanno una

tensione di soglia per entrare in conduzione. Tuttavia, sono caratterizzati

da un fattore guadagno*ampiezza di banda più basso.

I FET possono essere a canale n o a canale p. La polarità delle tensioni da

applicare e il verso delle correnti dipenderanno dal tipo di componente. Per

le nostre applicazioni si utilizzeranno sempre FET a canale n.

I tre terminali di accesso al dispositivo sono denominati GATE (porta),

SOURCE (sorgente), DRAIN (pozzo). Nel JFET, l’elettrodo di gate

pilota una giunzione di tipo p-n che costituisce l’elemento di controllo,

mentre gli elettrodi di source e drain servono per applicare la tensione

necessaria per lo scorrimento (drift) delle cariche nel canale di

semiconduttore.

La tensione di controllo viene quindi applicata al gate e per il regolare

funzionamento di un JFET a canale n deve assumere valori negativi

compresi fra VPO e 0 V (deve essere una giunzione polarizzata

inversamente). Questo valore negativo definito tensione di strozzamento

o di pinch-off VPO è quello in corrispondenza al quale non può scorrere

alcuna corrente attraverso i terminali di uscita, ossia dal source al drain.

Il source è usualmente considerato il terminale di riferimento e talvolta

collegato a massa, mentre il drain si pone a un livello positivo di tensione

rispetto al source. Pertanto, riassumendo, si ha:

Tensione applicata al gate rispetto al source

VGS < 0

Tensione applicata al drain rispetto al source

VDS > 0

Dato che in ingresso non circola corrente di livello apprezzabile, si

prendono in considerazione le caratteristiche di uscita e la caratteristica di

trasferimento per un’analisi completa del funzionamento del JFET.

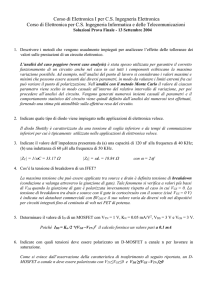

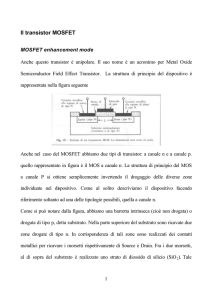

La tensione VPO è molto importante poiché da essa dipende il luogo dei

punti individuato sulle caratteristiche di uscita in cui il funzionamento del

JFET passa dal regime lineare al regime di saturazione. Infatti, per tensioni

applicate fra source e drain tali che |VGS |+|VDS |<|VPO |, il JFET si

comporta come una resistenza il cui valore è determinato dalla

tensione VGS (VCR, Voltage Controlled Resistor). Tale resistenza è

indicata con rDS(ON) , ovvero definita resistenza di canale in zona lineare, ed

è pari a VDS/IDS. Ciò avviene tipicamente per valori di VDS abbastanza

ridotti, mentre la corrente IDS può essere apprezzabile e questa situazione

corrisponde a quella di un interruttore chiuso. Il parametro rDS(ON) è quindi

importante nelle applicazioni per commutazione perché fornisce una

misura di quanto il FET si discosta da un interruttore ideale che ha

resistenza nulla nello stato ON.

Invece, per tensioni applicate fra source e drain tali che |VGS |+|VDS | ≥

|VPO |, la corrente IDS non dipende più da VDS ma darà controllata

esclusivamente da VGS (zona “piatta” delle caratteristiche, ovvero

regione di saturazione).

2.20e-4

VGS= 0 V

Linear

Region

2.00e-4

1.80e-4

I DSS

Pinch-off Locus

Drain-Source Current (A)

1.60e-4

Pinch-off Region

(Saturation)

1.40e-4

V = -1 V

1.20e-4

GS

1.00e-4

8.00e-5

V GS

= -2 V

6.00e-5

4.00e-5

VGSŠ V P

VGS= -3 V

2.00e-5

0.00e+0

0

2

4

6

8

10

12

Drain-Source Voltage (V)

Output characteristics for a JFET with IDSS = 200 A and VP = -4 V.

Si definisce corrente di saturazione del canale quella massima che si

ottiene per VGS = 0 e si indica con IDSS.

Si evidenzia che le caratteristiche drain-source di un FET reale presentano

anche una leggera inclinazione in zona di saturazione, cioè una piccola

dipendenza dalla tensione VDS = 0, visualizzabile quindi con una resistenza

in parallelo al generatore pilotato, il cui valore dipende dal punto di riposo.

La massima tensione che può essere applicata tra source e drain è definita

tensione di breakdown (conduzione a valanga attraverso la giunzione di

gate). Tale fenomeno si verifica a valori più bassi di VDS quando la

giunzione di gate è polarizzata inversamente rispetto al caso in cui VGS = 0.

La tensione di breakdown tra drain e source con il gate in cortocircuito con

il source (cioè VGS = 0 V) è indicata nei datasheet commerciali con BVDSS

e il suo valore varia da diversi volt nei dispositivi per circuiti integrati fino

al centinaio di volt nei FET di potenza.

Quando il FET si trova in interdizione, cioè per |VGS | > |VPO |, esiste una

piccola fuga di corrente sia attraverso il gate (IGSS , corrente inversa di gate

misurata a VDS = 0 V) sia tra source e drain (IDS(OFF) ) di cui il costruttore

fornisce i valori massimi che sono tuttavia suscettibili di forti incrementi

con la temperatura visto che alla temperatura di 150 °C aumentano di un

fattore 1000 rispetto al valore che hanno a temperatura ambiente.

Ovviamente il JFET utilizzato in zona di interdizione costituisce un

interruttore in stato OFF (corrente nulla, tensione apprezzabile).

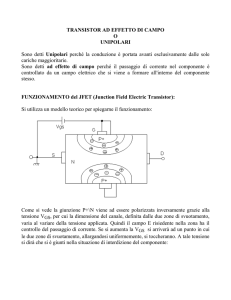

Drain-Source Current (A)

1.50e-3

I DSS

1.00e-3

5.00e-4

0.00e+0

V

P

-5.00e-4

-6

-5

-4

-3

-2

-1

0

1

2

3

Gate-Source Voltage (V)

Transfer characteristic for a saturated JFET with IDSS = 1 mA and VP = -3.5 V.

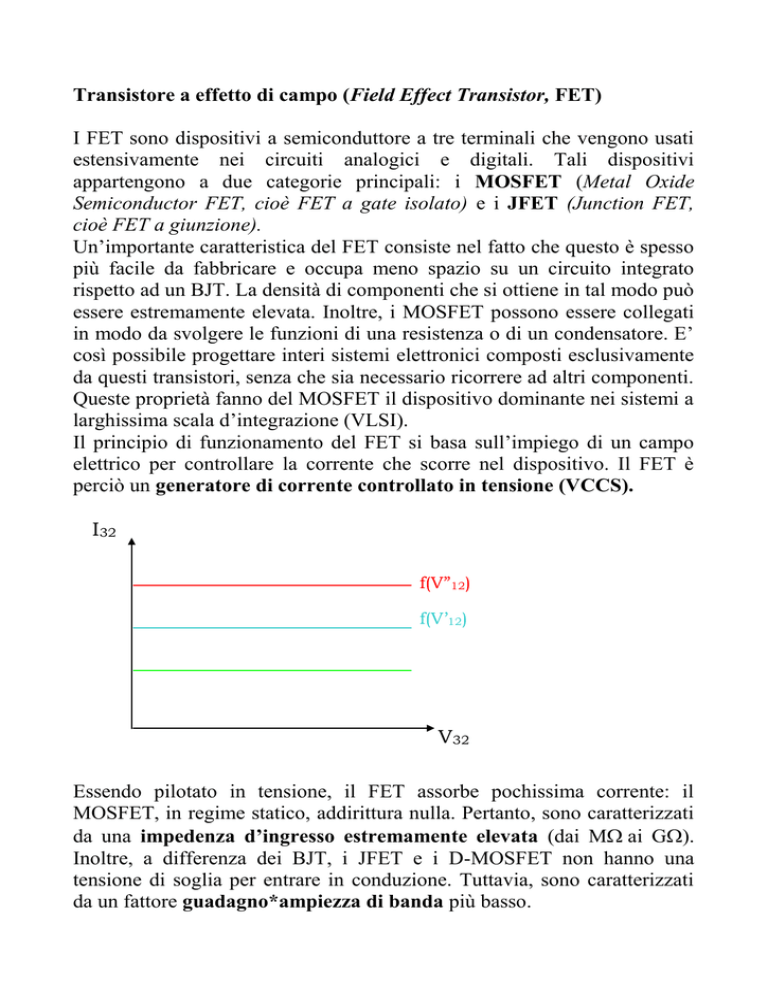

La caratteristica di trasferimento è il luogo dei punti IDS = f(VGS ) rilevati

in zona di saturazione, ossia dove la dipendenza della corrente dalla VDS

è trascurabile. La caratteristica di trasferimento può essere espressa in

forma analitica nella maniera seguente:

IDS = IDSS (1 - VGS / VPO )2

Per un JFET a canale n sia VGS sia VPO sono negative, mentre per un JFET

a canale p sono positive, pertanto l’espressione è valida per entrambi i tipi

di dispositivi.

La pendenza della caratteristica di trasferimento in ogni suo punto fornisce

il parametro di controllo del FET, cioè la transconduttanza g m che è quindi

definita come:

gm = ∂IDS/∂VGS |VDS cost

(1)

Più elevato è il valore della transconduttanza di un JFET, più sensibile sarà

la variazione di corrente di drain in corrispondenza ad una variazione di

tensione di gate e quindi il suo potere di amplificazione.

Dalla (1) si ricava che:

gm = gm0 (1 - VGS / VPO )

(2)

dove gm0 = 2 IDSS / VPO è il valore della transconduttanza ricavato nel

punto a VGS = 0.

D

+

v SG

i DS

G

S

+

+

-

v

v

DS

G

+

-

vGS

-

S

SD

i SD

D

n-channel JFET

p-channel JFET

N-channel and P-channel JFET circuit symbols