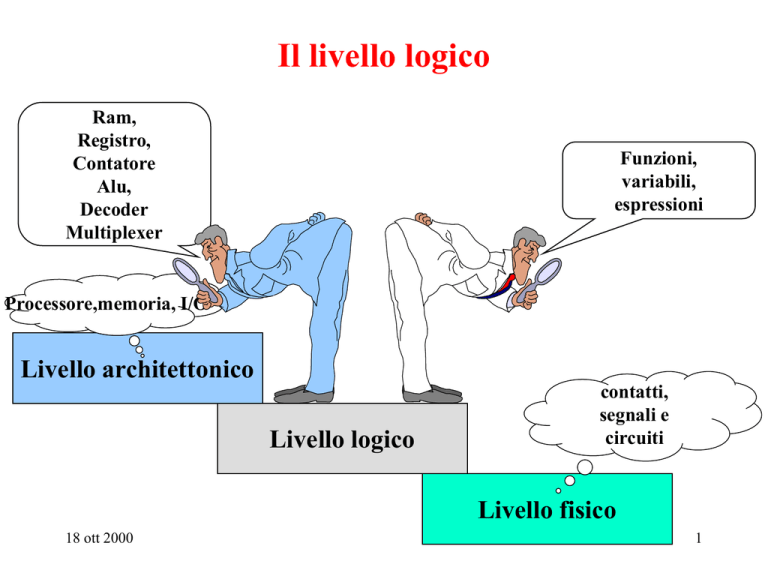

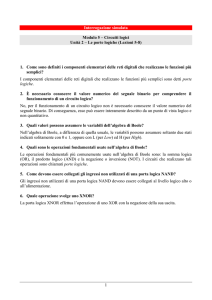

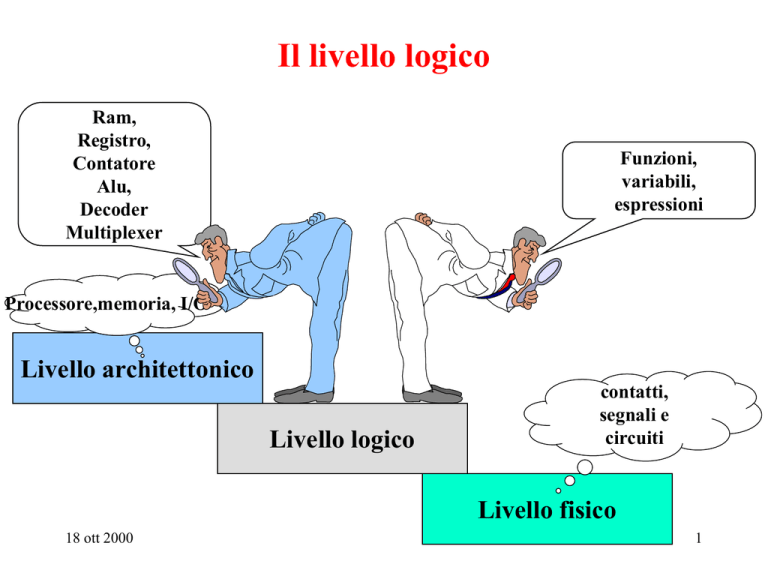

Il livello logico

Ram,

Registro,

Contatore

Alu,

Decoder

Multiplexer

Funzioni,

variabili,

espressioni

Processore,memoria, I/O

Livello architettonico

Livello logico

contatti,

segnali e

circuiti

Livello fisico

18 ott 2000

1

Analisi e sintesi di

reti combinatorie

introduzione:

porte logiche e

operatori logici

18 ott 2000

2

Introduzione

•

•

Analisi

Sintesi

•

•

Nella prima settimana del corso abbiamo introdotto il modello di comportamento e di struttura delle

reti sequenziali (ad esempio il semaforo), e ne abbiamo descritto il funzionamento con il diagramma

degli stati e la tabella di flusso

Quindi ci siamo posti l’obiettivo di progettare una rete logica (cioè un sistema di elaborazione binario)

che realizzasse il funzionamento descritto dalla t.d.f.

A tal fine abbiamo codificato in binario gli stati interni, gli ingressi e le uscite della rete e abbiamo

così potuto tradurre la tabella di flusso in tabella delle transizioni. La t.d.t. non è altro che un insieme

di tabelle della verità che descrivono le funzioni combinatorie F e G (rispettivamente variabili di

uscita e di stato futuro)

Non resta ora che imparare a “fare la sintesi” cioè disegnare lo schema logico delle reti logiche

combinatorie F e G assegnate con la tabella delle transizioni, dopodichè potremo completare il

progetto della rete sequenziale disegnando i rami di retroazione sulla funzione G. A quel punto

potremo verificare con il simulatore l’effettiva correttezza del nostro progetto

•

Inoltre siamo in generale interessati a scoprire qual è il funzionamento di un rete sequenziale di cui

conosciamo lo schema logico. Per prima cosa dobbiamo allora imparare “a fare l’analisi” cioè a

scoprire la tabella della verità delle reti combinatorie F e G; solo a quel punto potremo puntare a

disegnare il d.d.s. della rete e quindi a capirne il funzionamento

•

Nei prossimi lucidi possiamo studieremo uno strumento matematico (l’algebra di commutazione) che

ci consente di eseguire l’analisi e la sintesi di reti logiche combinatorie composte dagli operatori logici

elementari AND, OR e NOT. Questi tre operatori costuituiscono un insieme di operatori

funzionalmente completo: con essi cioè è possibile realizzare qualunque rete logica combinatoria.

18 ott 2000

3

Premessa fondamentale allo studio delle reti

combinatorie: l’approssimazione del modello

•

Il modello di comportamento delle reti logiche combinatorie mette in

relazione le uscite con il valore degli ingressi nello stesso istante (F: I U)

•

Nel modello quindi si ipotizza implicitamente che il ritardo introdotto dalle

reti combinatorie sia nullo.

•

Questa è un’approssimazione del vero comportamento dei circuiti elettronici

che realizzano reti combinatorie; infatti tutti i circuiti reali introducono un

ritardo, per quanto piccolo.

•

Estinto il ritardo, però, il comportamento del circuito elettronico è

esattamente quello “modellato” dalla definizione della macchina

combinatoria (F: I U).

•

Si può quindi affermare che il ritardo rappresenta un fenomeno transitorio,

estinto il quale il modello della macchina combinatoria riflette il

funzionamento del circuito elettronico

•

Il funzionamento dopo il transitorio iniziale si chiama anche “funzionamento

a regime”

18 ott 2000

4

Comportamento a regime e in transitorio

dei circuiti combinatori

I nuovi valori dei segnali di ingresso di una rete combinatoria

devono propagarsi all’interno della struttura prima di

riuscire ad imporre al segnale d’uscita il valore che ad essi

deve corrispondere. Ciò determina un comportamento in

transitorio, che in generale sarà diverso da quello a regime.

Il comportamento a regime è quello previsto dal modello.

ingresso i

uscita u

18 ott 2000

comportamento

in

transitorio

comportamento

a

regime

5

Altra premessa allo studio delle reti combinatorie:

le porte logiche e gli operatori elementari

Gate o porta logica - Struttura formata da alcuni interruttori

singolarmente azionabili dall’esterno e caratterizzata da un segnale

di uscita il cui valore a regime dipende unicamente dai valori

contemporanei dei segnali di azionamento degli interruttori.

•

Operatore logico elementare: rete logica combinatoria “primitiva” cioè considerata

non decomponibile (vedi principio di decomposizione delle reti logiche)

•

Gli operatori logici elementari vengono assegnati mediante la relazione

ingresso/uscita e vengono rappresentati con simboli che li identificano.

Esempio: ecco i tre operatori logici elementari definiti nell’algebra di commutazione

Ciascuno di essi viene realizzato con porte logiche chiamate con lo stesso nome

18 ott 2000

L’operatore

“not”

L’operatore

“and”

L’operatore

“or”

6

Esempio: il gate “not” elettronico e

l’operatore logico “not”

Questo è l’operatore logico che

useremo nei nostri progetti

I

U

0 volt V

i

oppure

+E volt

18 ott 2000

U

0

1

1

0

Con la codifica di Vi e Vu

si ottiene la tabella della

verità dell’operatore

logico il quale agirà su

variabili binarie

+E

Vu

I

+E volt

oppure

0 volt

Questo è il gate

Se Vi= E allora

l’interruttore è chiuso

Vi

Vu

0

+E

+E

0

7

Velocità di commutazione:

il ritardo del Not elettronico

+E

causa: Vi

Vu

alta

bassa

tempo

Vi

effetto: Vu

alta

18 ott 2000

DT1

DT2

bassa

tempo

8

Il ritardo sui fronti

• Il ritardo sui fronti di salita (tLH) e di discesa (tHL) è

presente in ogni tipo di gate e varia in modo notevole

da dispositivo a dispositivo.

• A causa della marcata differenza dei due valori, la

durata di una situazione H o L in ingresso ad un gate

è diversa dalla corrispondente situazione in uscita.

• A causa della “inerzia” del gate, un segnale di

ingresso “impulsivo” e “troppo stretto” può non

essere avvertito in uscita.

18 ott 2000

9

Il ritardo di propagazione

ritardo di propagazione: tp = max (tLH, tHL)

• Ritardo puro

tp

Dt < tp

• Ritardo inerziale

nessun

effetto

tp

Il modello del ritardo inerziale è il più vicino alla realtà

Il ritardo puro (o matematico) è però più facile da simulare

18 ott 2000

10

Un modello più realistico per il gate

x1

x2

Simbolo grafico

dell’operatore logico

o gate “ideale”

Z

ritardo di

propagazione

z

xn

gate “reale” (o quasi)

Z = F(x1, x2, .., xn)

z(t) = Z(t-tp)

N.B. - I Costruttori di famiglie logiche forniscono i valori minimo, nominale e massimo di t p

•

L’operatore logico è una astrazione: esso descrive il funzionamento del gate

ideale, a ritardo nullo; descrive cioè il funzionamento del gate a regime

•

Il gate ha dunque un comportamento sequenziale: l’uscita all’istante t dipende dal

valore degli ingressi all’istante t-tp!

18 ott 2000

11

La relazione ingresso/uscita e il simbolo grafico

degli operatori logici AND e OR

Operatore logico AND

Operatore logico OR

18 ott 2000

I1

I2

U

0

0

0

0

1

0

1

0

0

1

1

1

I1

I2

U

0

0

0

0

1

1

1

0

1

1

1

1

Tabella della verità

Simbolo grafico

Tabella della verità

Simbolo grafico

12

La relazione ingresso/uscita e il simbolo grafico

dell’operatore NOT

I

Operatore logico NOT

•

•

•

•

U

0

1

1

0

Tabella della verità

Simbolo grafico

In una diapositiva precedente abbiamo visto come può essere fatto un gate che realizza

la funzione dell’operatore logico NOT con un interruttore elettronico

Nei corsi di elettronica digitale si studieranno altre realizzazioni dello stesso gate,

nonché diverse realizzazioni di gate che realizzano le funzioni degli operatori logici

AND e OR

Noi studieremo un metodo di analisi e sintesi di reti combinatorie composte da operatori

logici AND OR e NOT perché questi operatori possono essere realizzati con porte

logiche o gate elettronici, e perché, come vedremo, con questi operatori è possibile

realizzare qualunque rete combinatoria (si dice che i tre operatori AND OR e NOT

costituiscono un insieme di operatori logici funzionalmente completo)

Nel prossimo lucido viene mostrato concettualmente come un AND e un OR possono

essere realizzati utilizzando interruttori

18 ott 2000

13

I gate “and” e “or” realizzati con interruttori in serie

I1

0

1

0

1

I2

0

0

1

1

Il gate “and”

I2

0

0

1

1

AB

0

1

1

1

Il gate “or”

Due differenti

astrazioni!

{aperto = 0, chiuso = 1}

Contatti in serie

A

B

18 ott 2000

I1

I1

0

1

0

1

AB

0

0

0

1

I2

I1

aperto

aperto

chiuso

chiuso

{aperto = 1, chiuso = 0}

I2

aperto

chiuso

aperto

chiuso

AB

aperto

aperto

aperto

chiuso

14

I gate “and” e “or” realizzati con interruttori in parallelo

I1

0

1

0

1

I2

0

0

1

1

Il gate “or”

{aperto = 0, chiuso = 1}

Contatti in parallelo

18 ott 2000

I1

0

1

0

1

I2

0

0

1

1

AB

0

0

0

1

Il gate “and”

Due differenti

astrazioni!

A

AB

0

1

1

1

I1

I2

B

I1

aperto

aperto

chiuso

chiuso

{aperto = 1, chiuso = 0}

I2

aperto

chiuso

aperto

chiuso

AB

aperto

chiuso

chiuso

chiuso

15

Considerazioni sui due lucidi precedenti

• Nelle due precedenti diapositive abbiamo mostrato

concettualmente come un AND e un OR possono essere

realizzati utilizzando interruttori

• Si noti che la funzione logica realizzata dipende dalla

codifica: un AND in logica positiva è un OR in logica

negativa e viceversa

• questo fatto è una conseguenza di un principio detto di

“dualità” che vedremo successivamente

18 ott 2000

16

Analisi e sintesi di

reti combinatorie

algebra

della commutazione

18 ott 2000

17

Introduzione

•

•

•

•

Nelle prossime diapositive studieremo uno strumento matematico

(l’algebra di commutazione) che ci consente di eseguire l’analisi e la

sintesi di reti logiche combinatorie composte dagli operatori logici

elementari AND, OR e NOT.

Questi tre operatori costuituiscono un insieme di operatori

funzionalmente completo: con essi cioè è possibile realizzare qualunque

rete logica combinatoria

Trattandosi di operatori logici combinatori essi verranno considerati

operatori con ritardo nullo

Quando vorremo tener conto del ritardo introdotto da un operatore

utilizzeremo il modello della diapositiva n. 11:

disegneremo il ritardo t con un blocco specifico sull’uscita

dell’operatore (oppure indicheremo il ritardo nell’operatore stesso)

tp

Operatore logico

combinatorio AND

18 ott 2000

tp

AND con ritardo t p

18

Comportamento & Struttura

di una rete logica combinatoria

?

Rete logica combinatoria

Tabella della verità

x1x2x3 … xn

z = F(x1,.., xn)

0 0 0 ……..0

1 0 0 ……..0

0 1 0 ……..0

1 1 0 ……..0

0 0 1 ……..0

0 oppure 1

0 oppure 1

0 oppure 1

0 oppure 1

0 oppure 1

Nell’algebra di

comutazione i blocchi Gi

sono AND OR e NOT

x1

x2

sintesi

x3

0 oppure 1

0 oppure 1

G2

G1

Gk

analisi

0 1 1 ……..1

ott 2000

1 1 118……..1

G3

xn

19

z

Algebra della commutazione

È un sistema matematico che consente di eseguire l’analisi e la

sintesi di reti logiche combinatorie. L’algebra della commutazione

consente infatti di passare dallo schema logico alla tabella della

verità e viceversa

L’algebra viene definita assegnando:

• gli operatori dell’algebra

• i simboli su cui gli operatori agiscono

• i postulati che definiscono il comportamento degli operatori

Studiare l’algebra di commutazione significa studiare le proprietà dei

suoi operatori al fine di imparare a manipolare, costruire e analizzare

espressioni

C’è una corrispondenza biunivoca tra gli operatori dell’algebra di

commutazione e gli operatori logici elementari AND OR e NOT

18 ott 2000

20

Definizione dei simboli e delle operazioni

dell’algebra della commutazione

L’algebra della commutazione è:

• un’insieme di 3 operazioni

• un insieme di 2 simboli (0 e 1): questo insieme è l’alfabeto binario su cui

le operazioni dell’algebra agiscono

1) Operazioni:

somma logica (+) (4 postulati, diap. 22)

prodotto logico (.) (4 postulati, diap. 23)

complementazione (’) (2 postulati, diap.22)

Le operazioni dell’algebra agiscono su costanti e variabili

2) Costanti: 0, 1

3) Variabili: simboli sostituibili o con 0 o con 1

18 ott 2000

(segue)

21

Definizione delle tre operazioni dell’algebra di

commutazione e dei corrispondenti operatori logici

Complementazione : z = x’ , z =x , z = x

Postulati:

0’ = 1

1’ = 0

Funzione: x

0

1

z

1

0

Realizzazione:

z

x

Operatore NOT

Somma logica: z = x + y , z = x y

Postulati:

0+0=0

0+1=1

1+0=1

1+1=1

18 ott 2000

Funzione: x

0

0

1

1

y

0

1

0

1

z

0

1

1

1

Realizzazione:

Operatore OR

x

z

y

(segue)22

Prodotto logico: z = x . y , z = xy , z = x y

Postulati:

0.0=0

0.1=0

1.0=0

1.1=1

Funzione: x

0

0

1

1

y

0

1

0

1

z

0

0

0

1

Realizzazione:

x

z

y

Operatore logico AND

C’è una corrispondenza biunivoca tra gli operatori logici NOT, OR, AND

e le tre operazioni dell’algebra complementazione, somma logica e

prodotto logico (rispettivamente rappresentate con i caratteri ‘ + . )

C’è una corrispondenza biunivoca tra ingressi dell’operatore logico e

operandi dell’operazione algebrica

C’è una corrispondenza biunivoca tra l’uscita dell’operatore logico e il

risultato dell’operazione algebrica

18 ott 2000

(segue)

23

Giustificazione delle prossime diapositive

•

Sintesi Analisi

•

•

•

•

•

•

L’algebra della commutazione è il ponte tra la struttura della rete combinatoria e la

descrizione del suo comportamento (cioè della relazione tra ingressi e uscita)

rappresenteremo la struttura con il suo schema logico

rappresenteremo la relazione ingressi/uscita (cioè il comportamento) sotto forma di

funzione binaria di variabili binarie

Per fare l’analisi assoceremo a ogni schema logico una espressione dell’algebra e di lì

passeremo alla funzione con un procedimento detto “valutazione dell’espressione”

Per fare la sintesi impareremo a determinare una espressione dell’algebra che “descriva

la funzione” da sintetizzare e quindi impareremo a disegnare lo schema logico

corrispondente all’espressione trovata

Dobbiamo quindi definire i seguenti oggetti e le relative proprietà:

– l’espressione dell’algebra

– la funzione binaria di variabili binarie

– lo schema logico

dobbiamo inoltre:

–

–

–

18 ott 2000

imparare a passare dallo schema logico all’espressione e viceversa

studiare il procedimento di valutazione delle espressioni

imparare a descrivere le funzioni (ad esempio con la tabella della verità)

24

Definizione di espressione

dell’algebra di commutazione

Espressione: - Stringa finita di costanti, variabili, operatori e parentesi,

formata in accordo con le seguenti regole:

1) 0 e 1 sono espressioni

2) una variabile è una espressione

3) se A è un’espressione, lo sono anche (A’) e A’

4) se A, B sono espressioni, lo sono anche (A+B), (A.B)

Esempi:

a+(b.c)

a’.b

a + bc

(a+b)’

a’b + 0 + ab’

• L’operazione di prodotto è prioritaria rispetto alla somma e non è obbligatorio

racchiuderla tra parentesi.

• La notazione AB indica A.B

• Le parentesi sono obbligatorie solo se omettendole cambia l’ordine in cui le

operazioni sono applicate agli operandi

18 ott 2000

25

Definizione di

Funzione completamente specificata

Una Funzione completamente specificata di n variabili binarie z=F(x1, x2, …, xn)

è l’insieme di tutte le 2n coppie ordinate x,z x Bn, z B formate da

una configurazione di valori delle n variabili indipendenti xi e

dal corrispondente valore della variabile dipendente z.

Una funzione può essere descritta in diversi modi, come, ad esempio:

Con la tabella della verità

con le mappe di Karnaugh

X2

X1

X0

Z

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

0

1

1

x1 x0

x2

00

0 0

1 0

01 11 10

1

1 0

0

1

z

1

Due rappresentazioni equivalenti della stessa funzione z = F(x2, x1, x0)

18 ott 2000

26

Descrizione di una funzione mediante

Tabella della verità

La Tabella della verità è una

- Descrizione tabellare di una funzione di variabili binarie

n+1 colonne

2n righe

x1, x2, …, xn F(x1, x2, …, xn)

0 0 0 ……..0 0 oppure 1

1 0 0 ……..0 0 oppure 1 Quante colonne ha la

0 1 0 ……..0 0 oppure 1 t.d.v. di una funzione

1 1 0 ……..0 0 oppure 1 di 4variabili?

righe ha la

0 0 1 ……..0 0 oppure 1 Quante

t.d.v. di una funzione

di 8 variabili?

18 ott 2000

0 1 1 ……..1

1 1 1 ……..1

0 oppure 1

0 oppure 1

27

Descrizione di una funzione mediante

Mappe di Karnaugh

Mappa di Karnaugh - Rappresentazione bidimensionale della

tabella della verità di una funzione di 2,3,4 variabili, i cui valori

sono stati elencati sui bordi in maniera che due configurazioni

consecutive siano a distanza 1, differiscano cioè per il valore

di un solo bit.

ab

Esempi:

a

b

0

0 0

1 1

1

1

1

Somma

logica

18 ott 2000

cd

00

01

11

10

00 01 11 10

0 1 0 1

1 0 1 0

0 1 0 1

1 0 1 0

Parità pari su

4 variabili

28

Importante proprietà delle mappe di Karnaugh:

Adiacenza tra celle

Coppia di celle adiacenti su mappe di Karnaugh - Due celle le

cui coordinate differiscono per un solo bit.

In una mappa che descrive una funzione di n variabili ogni cella

ha n celle adiacenti.

Regola grafica per l’adiacenza Sono adiacenti celle aventi un lato

in comune o poste all’estremità di una stessa riga o colonna.

cella scelta come esempio

celle adiacenti

b

a

0 1

0

1

2 variabili

18 ott 2000

ab

a

bc

00 01 11 10

0

1

3 variabili

cd

00 01 11 10

00

01

11

10

4 variabili

29

Estensione delle mappe a 5 e a 6 variabili

ef

00

cd

de

de

00 01 11 10 bc

bc

00

00

00

01

11

01

11

10

10

a=0

01 11 10

ef

01 11 10 cd

00

00

01

11

01

11

10

10

ab=00

ef

a=1

00

00

cd

00

00

00

5 variabili

01

11

Ulteriore regola di adiacenza Sono adiacenti celle che occupano

la stessa posizione in sotto-mappe

adiacenti.

10

01

11

10

18 ott 2000

ab =01

ef

01 11 10 cd

01 11 10

ab =10

01 11 10

ab=11

6 variabili

30

Check point

• Cosa è una funzione completamente specificata e come possiamo

rappresentarla?

• Cosa è una espressione dell’algebra di commutazione e quali

operatori può includere?

• Si risponda alle due domande precedenti con alcuni esempi.

• Cosa è la sintesi di una rete combinatoria?

• Cosa è l’analisi di una rete combinatoria?

• Come si passa da un’espressione alla funzione? Col procedimento

di valutazione che vediamo nelle prossime diapositive

• Come si passa dalla funzione all’espressione? Con i procedimenti

di sintesi che vedremo più avanti

18 ott 2000

31

Valutazione di una espressione in un punto

Sia data una espressione E in cui compaiono n variabili e sia data una

configurazione binaria di queste n variabili

Valutare l’espressione E nella configurazione binaria data (cioè in un particolare

punto del suo dominio di definizione) significa eseguire i seguenti passi:

1 - sostituire ad ogni variabile il valore che ha nella configurazione data

2 - partendo dalle parentesi più interne sostituire ogni

operazione con il corrispondente risultato calcolato applicando i postulati

dell’algebra, fino ad ottenere o la costante 0 o la costante 1.

Esempio:

Valutiamo E(a,b,c) = a+(b.c) con a=0, b=1, c=0

0+(1.0)

= 0+0

=0

N° di valutazioni - Una espressione di n variabili può

essere valutata su 2n configurazioni binarie diverse

18 ott 2000

32

Regole di priorità nella valutazione

• Si ricordi che, in assenza di parentesi valgono le seguenti

regole:

– L’operazione di complementazione è prioritaria

rispetto a prodotto e somma

– L’operazione di prodotto è prioritaria rispetto alla

somma e non è obbligatorio racchiuderla tra

parentesi.

18 ott 2000

33

Passaggio dalla espressione alla funzione

•

•

•

•

•

Il passaggio dalla espressione alla funzione si chiama anche “valutazione della

espressione nel suo dominio”

Valutare una espressione di n variabili nel suo dominio Bn significa costruire

una tabella della verità di 2n righe (una per ogni configurazione delle n

variabili) e n+1 colonne.

Ogni riga conterrà nelle n colonne più a sinistra la configurazione binaria

associata alla riga stessa

Nella colonna più a destra di ogni riga si deve invece riportare la costante

determinata valutando l’espressione nel punto individuato dalla configurazione

binaria indicata nelle n colonne più a sinistra della riga stessa

Con la valutazione di una espressione è possibile ottenere la funzione associata

all’espressione data

18 ott 2000

34

Dall’espressione alla funzione: esempio

La valutazione di una espressione E(x0, x2, …, xn-1) nei 2n punti del

suo dominio dà origine a 2n coppie x,z x,z x Bn, z B

Esempio: E(a,b,c) = a+(b.c)

abc|E

E(0,0,0) = 0+(0.0) = 0

000|0

E(0,0,1) = 0+(0.1) = 0

001|0

E(0,1,0) = 0+(1.0) = 0

010|0

E(0,1,1) = 0+(1.1) = 1

011|1

E(1,0,0) = 1+(0.0) = 1

100|1

E(1,0,1) = 1+(0.1) = 1

101|1

E(1,1,0) = 1+(1.0) = 1

110|1

E(1,1,1) = 1+(1.1) = 1

111|1

Tabella della verità

della

funzione associata

all’espressione data

T1) Ogni espressione descrive una e una sola funzione

18 ott 2000

35

Dall’espressione alla funzione: altri esempi

T2) Una funzione può essere descritta da infinite espressioni

Esercizio

Verificare che le valutazioni di

E1=(a.b’) + (b.c) + (a.b)

E2=(a+b).(a+c)

sono identiche a quelle di

E = a+(b.c)

18 ott 2000

abc

000

001

010

011

100

101

110

111

E E1 E2

0

0

0

1

1

1

1

1

36

Analisi di una rete logica combinatoria:

dalla Struttura al Comportamento

Espressione

Valutazione

Tabella della verità

x1x2x3 … xn

z = F(x1,.., xn)

0 0 0 ……..0

1 0 0 ……..0

0 1 0 ……..0

1 1 0 ……..0

0 0 1 ……..0

0 oppure 1

0 oppure 1

0 oppure 1

0 oppure 1

0 oppure 1

Avendo studiato

come si passa

dall’espressione

alla funzione,

dobbiamo ora

esaminare il

passaggio dallo

schema logico

della rete

combinatoria

all’espressione

18 ott 2000

0 oppure 1

0 oppure 1

x1

x2

G3

x3

G2

G1

Gk

analisi

0 1 1 ……..1

1 1 1 ……..1

Rete logica combinatoria

xn

Schema logico:

insieme di operatori AND,

OR, NOT

interconnessi in serie e

parallelo

37

z

Dallo schema logico all’espressione

Per individuare l’espressione corrispondente ad un dato schema

si parte dai gate che elaborano solo segnali di ingresso, si assegna

un simbolo alla loro uscita e si annota a parte l’espressione.

Si procede in modo analogo con i gate i cui ingressi sono già stati

denominati. Una volta individuata l’espressione del gate di uscita,

vi si sostituiscono tutti i simboli con le corrispondenti espressioni.

c = a’

a

e = (c . b)

Questa rete realizza un importante

operatore logico detto

OR ESCLUSIVO o XOR (Exclusive Or)

z=e+f

= (c.b) + (a.d)

= a’b + a.b’

b

d = b’

18 ott 2000

f = (a . d)

Qual è la tdv di questa rete?

Se ne descriva a parole il comportamento

38

Check point

•

Come si esegue l’analisi di uno schema logico composto da AND, OR e NOT

interconnessi?

•

Qual è il risultato dell’analisi?

•

Esistono altre tecniche di analisi oltre a quella basata sulla valutazione delle

espressioni? Sì, le vedremo in alcune diapositive successive

•

Quante espressioni sono associate a uno schema logico?

•

Quante funzioni sono associate a una espressione?

•

Quante espressioni sono associate a una funzione?

18 ott 2000

39

Esercizi

•Si disegni lo schema logico dell’espressione: ac + bc’

•La rete così ottenuta si chiama multiplexer a due vie

•Si analizzi questa rete (se ne tracci la mappa) e se ne descriva a parole il

funzionamento

•Si verifichi con il simulatore la correttezza della soluzione trovata

Si tracci la tabella della verità e lo schema logico corrispondenti

all’espressione:

E(D, C,B,A) = D.(C + B)

Si descriva a parole la funzione nel caso in cui i bit D, C, B, A

rappresentino i coefficienti del numero D.23+ C.22+ B.21+ A.20

18 ott 2000

40

Check point sull’analisi delle reti combinatorie

•

Abbiamo visto un metodo di analisi basato sulla valutazione delle espressioni

associate allo schema logico assegnato.

•

Questo metodo può diventa impraticabile quando l’espressione è complessa

•

In questo caso si possono utilizzare in generale due metodi alternativi:

– la semplificazione dell’espressione mediante applicazione di alcune

proprietà dell’algebra della commutazione

– la semplificazione sistematica dell’espressione mediante applicazione del

teorema di espansione

•

Nelle prossime diapositive illustreremo alcune proprietà (o teoremi)

dell’algebra di commutazione e mostreremo qualche esempio del primio

metodo

•

Il secondo metodo verrà presentato successivamente

18 ott 2000

41

Equivalenza tra espressioni

Espressioni equivalenti - Due espressioni E1, E2 sono equivalenti,

e si scrive

E1 = E2 , se e solo se descrivono la stessa funzione.

Funzioni

di

n variabili

Espressioni

di

n variabili

Espressioni

di F

F

•Se si vuole analizzare una espressione conviene cercare tra le espressioni equivalenti

alla espressione data, quelle più facili da analizzare! Questa ricerca può essere effettuta

applicando le equivalenze indicate nelle prossime due diapositive

18 ott 2000

42

Equivalenze notevoli

dell’algebra di commutazione

Proprietà della somma e del prodotto logico:

T4) commutativa

T5) associativa

T6) distributiva

T7) idempotenza

T8) identità

T9) limite

18 ott 2000

x+y

x.y

(x + y) + z

(x . y) . z

(x . y) + (x . z)

(x + y) . (x + z)

x+x

x.x

x+0

x.1

x+1

x.0

=

=

=

=

=

=

=

=

=

=

=

=

y+x

y.x

x+y+z

x . y. z

x . (y + z)

x + (y . z)

x

x

x

x

1

0

43

Altre equivalenze notevoli

dell’algebra di commutazione

Proprietà della complementazione:

T10) involuzione

(x ’) ’

=x

T11) limitazione

x+x’

x.x’

xy + xy’

(x+y).(x+y’)

=1

=0

=x

=x

T12) combinazione

T13) Ia legge di De Morgan (x + y) ’

Iia legge di De Morgan (x . y) ’

T14) consenso

18 ott 2000

= x ’.y’

= x ’+y’

xy + x’z + yz

(x+y).(x’+z).(y+z)

= xy + x’z

= (x+y).(x’+z)

44

Dualità

Espressioni duali - Data l’espressione E(x, y, z, .., 1, 0, +, ., ’)

è detta duale di E e denotata con Ed l’espressione che si ottiene

scambiando tra loro 0,1 e .,+

Ed = E(x, y, z, .., 0, 1, .,+, ’).

Esempio: A+B e A.B (nell’esempio si scambiano solo gli operatori . e +)

Proprietà della dualità:

(Ed)d = E

Ed = E’(x’, y’, z’, ...)

Se E1 = E2 allora (E1 )d = (E2 )d

•La terza proprietà dice che se due espressioni sono equivalenti, lo sono anche le

rispettive duali. Si verifichi questa proprietà nelle equivalenze notevoli dei lucidi

precedenti

N.B. - A causa delle due possibili codifiche dei valori di un segnale binario, il comportamento di ogni struttura di

interruttori azionabili indipendentemente uno dall’altro ha due descrizioni algebriche, una duale dell’altra.

18 ott 2000

45

Qualche commento sui

teoremi dell’algebra di commutazione

•

•

•

•

•

•

•

•

•

La proprietà associativa per l’OR si può anche scrivere come segue:

(x + y) + z = x + (y + z) = (z + x) + y = x + y + z

Questa proprietà ci dice che combinando in qualunque modo tre ingressi con due OR in

cascata si ottengono sempre espressioni equivalenti; la funzione che si ottiene vale 1 se

e solo se almeno un ingresso vale 1. Possiamo chiamare questa funzione “OR a tre

ingressi”; è possibile nello stesso modo definire l’OR a n ingressi

si verifichi la proprietà associativa con il simulatore

chiamiamo NOR l’operatore composto da un OR e un NOT in cascata; si disegni la tdv

di questo operatore composto e si dimostri che per questo operatore non vale la proprietà

associativa

Per la terza proprietà sulla dualità quello che abbiamo detto per l’OR vale anche per

l’AND e quello che non vale per il NOR non vale nemmeno per l’operatore composto

dalla serie AND-NOT (il NAND)

I teoremi di De Morgan indicano l’equivalenza tra NOR e AND degli ingressi

complementati e l’equivalenza tra NAND e OR degli ingressi complementati

Il teorema del consenso indica due diversi modi per realizzare la funzione “multiplexer a

due vie” già vista in un esempio precedente

18 ott 2000

46

Qualche esercizio di analisi da svolgere utilizzando

i teoremi dell’algebra della commutazione

• Si esegua l’analisi delle seguenti espressioni:

• xy + x’z + xyz + yz

• (((x+y)’+(z+w)’)’+1)’

• ((x+y)’+(z+y)’)’

• per l’ultimo esercizio si consiglia di eseguire le semplificazioni a

partire dallo schema logico

• Per il primo si suggerisce di provare sia con i teoremi, sia tracciando

direttamente la mappa di Karnaugh

18 ott 2000

47

Check point

•

Ora siamo in grado di eseguire l’analisi delle reti combinatorie realizzate con

gli operatori dell’algebra di commutazione. Il procedimento si basa sulla

semplificazione delle espressioni (ottenuta applicando intuitivamente i

teoremi dell’algebra) e sulla relativa valutazione.

•

Resta ancora da vedere una tecnica di semplificazione sistematica

dell’espressione basata sull’applicazione del teorema di espansione già

annunciato e che dobbiamo ancora studiare

•

Prima vogliamo affrontare il problema della sintesi e vogliamo inoltre

dimostrare che gli operatori dell’algebra sono un insieme funzionalmente

completo (il che significa che con AND, OR e NOT è possibile realizzare

qualunque tabella della verità)

18 ott 2000

48

Il problema della sintesi

Funzione

assegnata

Espressioni equivalenti

Schemi logici

Individuazione dell’espressione che fornisce lo schema

“migliore” per la realizzazione della funzione assegnata.

Massima velocità

Massima flessibilità

18 ott 2000

Minima complessità

49

Funzioni non completamente specificate

•Alcune configurazionidi ingresso possono essere impossibili, oppure per certe configurazioni di

ingresso può non interessare il valore dell’uscita. In questi casi la funzione è incompleta o “non

completamente specificata”

6) Funzioni incomplete - Funzioni di n variabili il cui dominio è un sottoinsieme di Bn

Le configurazioni di valori delle variabili al di fuori del dominio sono dette

condizioni di indifferenza e sono indicate nella tdv con il simbolo “-” nella colonna

ove va indicato il valore della funzione.

ENCODER a 3 ingressi

x2

x1

x0

z1

0

0

0

0

1

0

0

1

0

1

0

1

0

0

1

0

N.B. le altre configurazioni

sono per ipotesi impossibili

18 ott 2000

z0

0

1

0

1

x2

x1

x0

z1

z0

0

1

0

0

0

0

1

0

0

0

0

1

0

1

1

0

0

1

0

1

1

1

0

1

1

0

1

1

0

1

1

1

-

50

Espressioni di funzioni incomplete

Espressioni equivalenti di funzioni incomplete - Espressioni che

forniscono eguale valutazione limitatamente al dominio di una

funzione incompleta data sono dette equivalenti rispetto ad essa

Espressioni per l’ENCODER:

Come funziona un encoder?

z1 = x2 x1’x0’+ x2’ x1 x0’

z0 = x2 x1’x0’+ x2’ x1’x0

u1 = x2 + x1

u0 = x2 + x0

18 ott 2000

x2

x1

x0

z1 u1 z0 u0

0

1

0

0

1

1

0

1

0

0

1

0

1

0

1

1

0

0

0

1

0

1

1

1

0

1

1

0

0

0

0

0

0

1

1

0

1

1

1

1

0

1

0

1

0

0

0

0

0

1

0

1

1

1

1

1

51

Espressioni normali

Espressione normale - Espressione del tipo “somma di prodotti

logici” (SP) o “prodotto di somme logiche” (PS).

Lo schema logico corrispondente ad una espressione normale

contiene al più due gate in cascata (tre, se non sono disponibili

anche i complementi dei segnali di ingresso).

Quando l’interesse preminente è la velocità di risposta,

l’espressione “migliore” è quella normale !

Nell’ambito delle espressioni normali hanno particolare rilievo:

le espressioni canoniche e le espressioni generali, che individuano

circuiti utili nella sintesi di qualsiasi funzione;

le espressioni minime, che consentono di realizzare una funzione

con il minimo numero di gate e di collegamenti.

18 ott 2000

52

Velocità e lunghezza dei percorsi

(a’.b’+a.b).c’+(a’.b+a.b’).c

c’

a’

b’

a

b

a’

b

a

b’

c

tp

tp

=

tp

tp

18 ott 2000

a’.b’.c’ +a.b.c’+a’.b. c +a.b’.c

a’

b’

c’

a

b

c’

a’

b

c

a

b’

c

tp

tp

Questa rete

è più veloce

53

Stima della durata del transitorio

(metodo del caso peggiore)

I1

U

I0

I1

A

t

t

I0

A

U

t

t

I1

3t U

I0

18 ott 2000

54

A

Sintesi di reti combinatorie

mediante AND, OR, NOT

• Come si esegue la sintesi di una rete combinatoria di cui è data la

tabella della verità? Si può utilizzare l’algebra di commutazione

• In tal caso si passa dalla tdv alla espressione e, successivamente, dalla

espressione allo schema logico

• Nelle prossime diapositive verrà illustrato il passaggio dall’espressione

allo schema logico. Il problema della determinazione di una

espressione associata alla tdv verrà esaminato successivamente

18 ott 2000

55

Dall’espressione allo schema logico

T3) Ogni espressione descrive una struttura formata da gate

AND, OR, NOT connessi in serie e/o in parallelo (schema logico)

Per individuare lo schema logico corrispondente ad una data

espressione si parte dalle parentesi più interne e si traccia il

simbolo del gate corrispondente all’operazione, collegandone

gli ingressi ai segnali esterni. Si procede in modo analogo con

le altre parentesi, considerando via via come ingressi dei nuovi

gate anche le uscite di quelli già tracciati.

a+(b.c)

18 ott 2000

b

c

a

56

Dall’espressione allo schema logico:

altro esempio

(((a)’ + b) . c)’

c

b

a

N.B. - Lo schema logico di una espressione non può avere segnali

in retroazione (l’uscita di ogni gate dipende da segnali d’ingresso

e/o da uscite di gate disposti “a monte”).

18 ott 2000

57

• Sintesi con

espressioni

canoniche

• Sintesi con

DECODER

e OR

18 ott 2000

58

Espressioni canoniche

T16) Espressione canonica SP (Somma di Prodotti)

Ia forma canonica - Ogni funzione può essere descritta da una

somma di tanti prodotti logici quante sono le configurazioni

per cui vale 1. In ciascun prodotto, o mintermine, appaiono tutte

le variabili, in forma o vera o complementata a seconda che nella

configurazione corrispondente presentino valore 1 o valore 0.

T17) Espressione canonica PS (Prodotto di Somme)

IIa forma canonica - Ogni funzione può essere descritta da un

prodotto di tante somme logiche quante sono le configurazioni

per cui vale 0. In ciascuna somma, o maxtermine, appaiono tutte

le variabili, in forma o vera o complementata a seconda che nella

configurazione corrispondente presentino valore 0 o valore 1.

18 ott 2000

59

Espressioni canoniche della funzione

“a implica b”

a b ab

00 1

01 1

10 0

11 1

IIa forma canonica:

F(a,b) = a’ + b

Ia forma canonica:

F(a,b) = a’ . b’ + a’ . b + a . b

Verifica della equivalenza per manipolazione algebrica:

F(a,b) = a’ . b’ + a’ . b + a . b

= a’ . (b’ + b) + a . b

= a’.1 + a . b

= a’ + a . b

= a’ + a . b + a’ . b

= a’ + b

18 ott 2000

60

Sintesi canonica dell’operatore EX-OR 1 se

1 se e solo se

x0=0 e x1=1

x0

x1

x0=0 e x1=1

oppure se

x0=1 e x1=0

0 negli altri

due casi

x1 x0 x0x1

0

0

1

1

0

1

0

1

0

1

1

0

18 ott 2000

1 se e solo se

x0=1 e x1=0

x0

x1

61

Sintesi di un ENCODER a tre ingressi

x2

x1

x0

z1

z0

0

1

0

0

0

0

1

0

0

0

0

1

0

1

1

0

0

1

0

1

z1

N.B. le altre configurazioni

sono per ipotesi impossibili

z1 = x2 x1’x0’+ x2’ x1 x0’

z0 = x2 x1’x0’+ x2’ x1’x0

18 ott 2000

z0

x2 x1 x0

62

Addizione “colonna per colonna” ...

(S)2 = (A)2 + (B)2

rn rn-1

ri

r1 0

an-1

ai

a1 a0

bn-1

bi

b1 b0

sn sn-1

si

s1 s0

18 ott 2000

+

r a b R

S

000

001

010

011

100

101

110

111

0

1

1

0

1

0

0

1

0

0

0

1

0

1

1

1

63

… e sintesi canonica del Full Adder

S = r’. a’. b + r’. a . b’ + r . a’. b’ + r. a . b

R = r’. a . b + r . a’. b + r . a . b’ + r . a . b

S

R

r’ r a’ a b’ b

18 ott 2000

64

Sintesi della trascodifica da binario a 1 su N

Esempio: Trascodifica 2:4

U0 = B’. A’

B A U0 U1 U2 U3

0

0

1

1

0

1

0

1

1

0

0

0

0

1

0

0

0

0

1

0

U1 = B’. A

0

0

0

1

U2 = B . A’

U3 = B . A

A

B

18 ott 2000

65

Il circuito integrato DECODER

Decoder o Rete di decodifica - Rete logica combinatoria che

realizza i 2n distinti prodotti di n variabili (n = 2,3,4)

U0

U1

U2

EN

U3

A

B

Quando EN=1, vale 1 l’uscita

il cui pedice, in decimale,

corrisponde al numero binario

in ingresso (A bit di minor peso)

18 ott 2000

N.B. - In realtà

le uscite sono

attive “basse”

SN74139 U0

(MSI)

U1

EN

U2

A

U3

B

SN74138 U0

(MSI)

U1

U2

U3

EN

U4

A

U5

B

U6

C

U7

SN74154 U0

(MSI)

U1

U2

U3

U4

U5

U6

U7

U8

U9

U10

EN

U11

A

U12

B

U13

C

U14

66

D

U15

Composizione modulare di Decoder

N.B. il prodotto

è associativo

1

C

D

U0

U

DEC 1

U2

2:4

U3

U0

U1

DEC

U2

2:4

U3

U0

U1

U2

U3

U0

U1

U2

U3

U0

U1

U2

U3

U4

U5

U6

U7

DEC

2:4

DEC

2:4

18 ott 2000

A

B

U0

U

DEC 1

U2

2:4

U3

U8

U9

U10

U11

U12

U13

U14

U15

67

Notazioni simboliche per le espressioni canoniche

i

rab

R

S

0

1

2

3

4

5

6

7

000

001

010

011

100

101

110

111

0

0

0

1

0

1

1

1

0

1

1

0

1

0

0

1

S (r,a,b) = S3 m (1,2,4,7)

S (r,a,b) = P3 M (0,3,5,6)

R (r,a,b) = S3 m (3,5,6,7)

R (r,a,b) = P3 M (0,1,2,4)

• m(i) : mintermine di n bit che assume il valore 1 solo per la n-pla di

valori delle variabili corrispondente all’indice i.

• M(i) : maxtermine di n bit che assume il valore 0 solo per la n-pla

di valori delle variabili corrispondente all’indice i.

18 ott 2000

68

Sintesi del Full Adder con Decoder e Or

S = S3 m (1,2,4,7)

R = S3 m (3,5,6,7)

’138

b

a

r

A

B

C

U0

U1

U2

U3

U4

U5

U6

U7

N.B - Le uscite di un decoder

TTL hanno fan-out >10.

Come si modifica lo schema se

si prende atto che le uscite sono

attive basse?

18 ott 2000

R

S

69