UNIVERSITÀ DEGLI STUDI DI PAVIA

DIPARTIMENTO DI ELETTRONICA

via Ferrata, 1 27100 Pavia

Tel.: 0382 - 985.200

Fax: 0382 - 422.583

Corso di Laurea in Ingegneria Elettronica

Elettronica per Telecomunicazioni

28/6/2005

ESERCIZIO 1

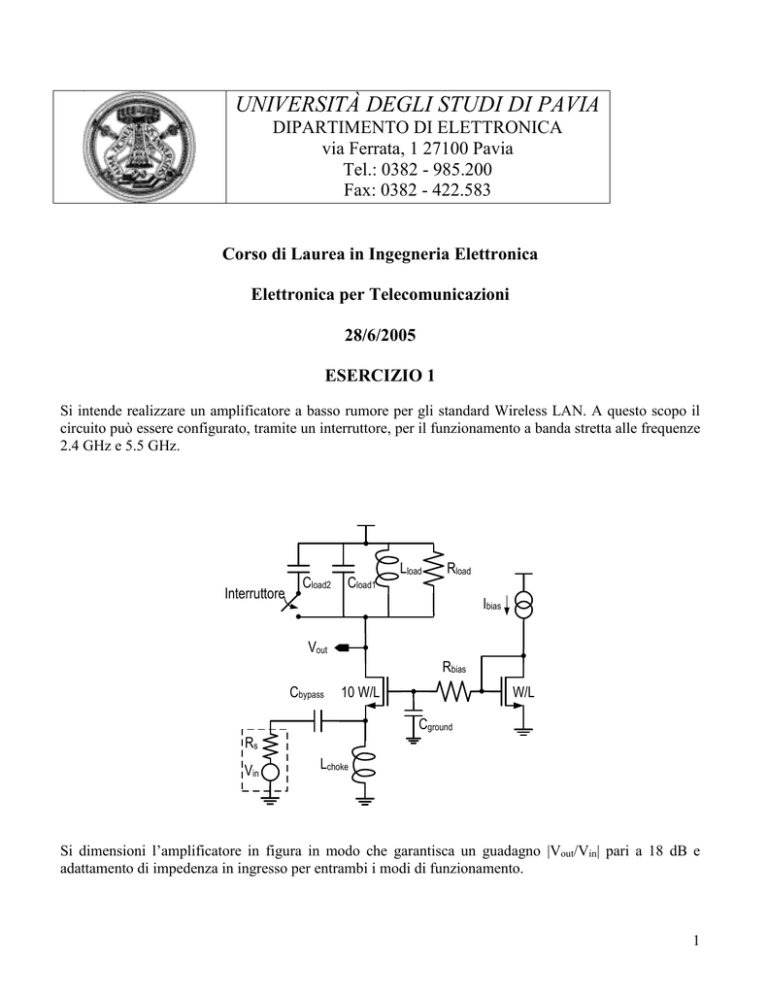

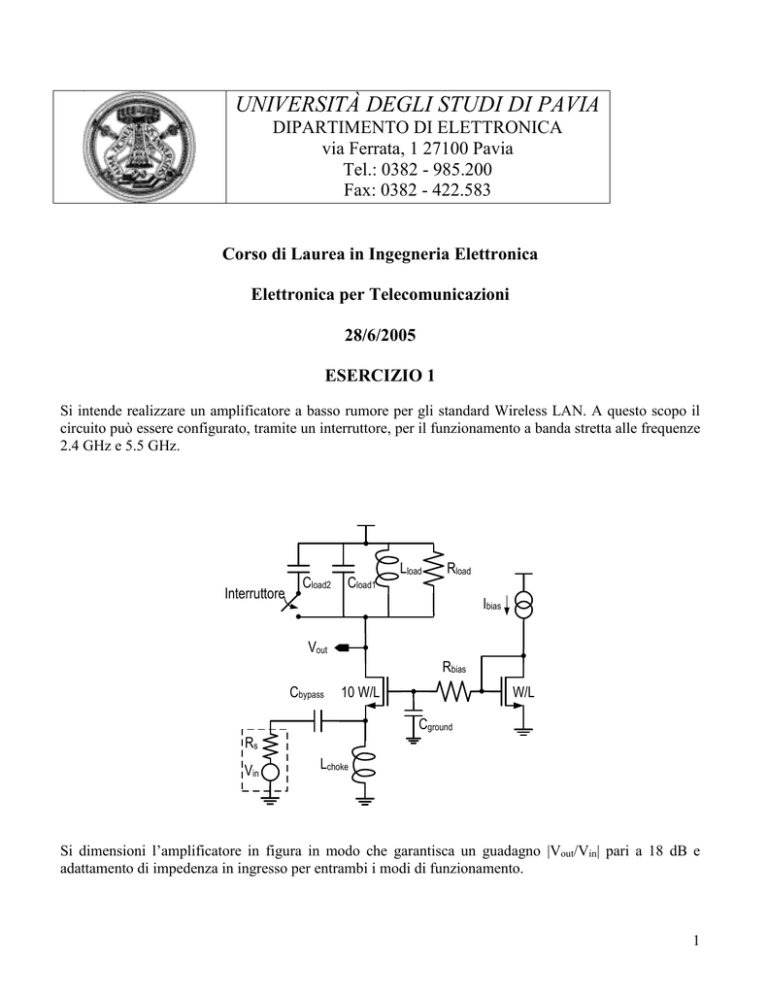

Si intende realizzare un amplificatore a basso rumore per gli standard Wireless LAN. A questo scopo il

circuito può essere configurato, tramite un interruttore, per il funzionamento a banda stretta alle frequenze

2.4 GHz e 5.5 GHz.

Interruttore

Cload2

Cload1

Lload

Rload

Ibias

Vout

Rbias

Cbypass

10 W/L

W/L

Cground

Rs

Vin

Lchoke

Si dimensioni l’amplificatore in figura in modo che garantisca un guadagno |Vout/Vin| pari a 18 dB e

adattamento di impedenza in ingresso per entrambi i modi di funzionamento.

1

Dati i valori in tabella, trovare i valori di Cload1, Cload2, Rload, Ibias , specificando per quale posizione dello

switch (aperto/chiuso) l’amplificatore funziona nell’una o nell’altra banda.

Resistenza di sorgente

Tensione di alimentazione

Induttanza di choke

Capacità di bypass

Rapporto di dimensione

Transconduttanza di processo

Induttanza di carico

Capacità di signal-ground

Resistenza di polarizzazione

RS

Vdd

Lchoke

Cbypass

(W / L)

nCox

Lload

Cground

Rbias

50

1.8 V

20

120 A/V2

6 nH

Si discuta inoltre l’impatto di un induttore di choke reale (induttanza di valore finito) sull’adattamento di

impedenza di ingresso e sul guadagno dell’amplificatore. Trattare anche con esempi numerici.

ESERCIZIO 2

Si consideri il seguente segnale, modulato FM:

SFM (t ) V0 cos 2 fC t K FM m( )d

0

dove fC è la frequenza portante, KFM è il guadagno del modulatore, ed m(t) il segnale modulante.

La frequenza portante (fc) può variare tra 10 e 12 MHz, con passi di 200 KHz, per un totale di 11 canali.

Il guadagno del modulatore è 20KHz/V, l’ampiezza massima del segnale modulante (m(t)) è 1V, mentre

la banda del segnale modulante è 5kHz.

Si vuole progettare un demodulatore di frequenza per rivelare il segnale m(t) utilizzando un PLL con

filtro RC passivo:

1) rappresentare e commentare lo schema a blocchi del demodulatore

2) Scegliere la frequenza libera del VCO, e il guadagno statico dell’anello,affinché l’errore di fase

massimo, in assenza del segnale modulante (m(t)=0) sia 10°.

3) scegliere la banda minima del filtro d’anello.

4) Determinare l’errore di fase se m(t) è un segnale a rampa

2