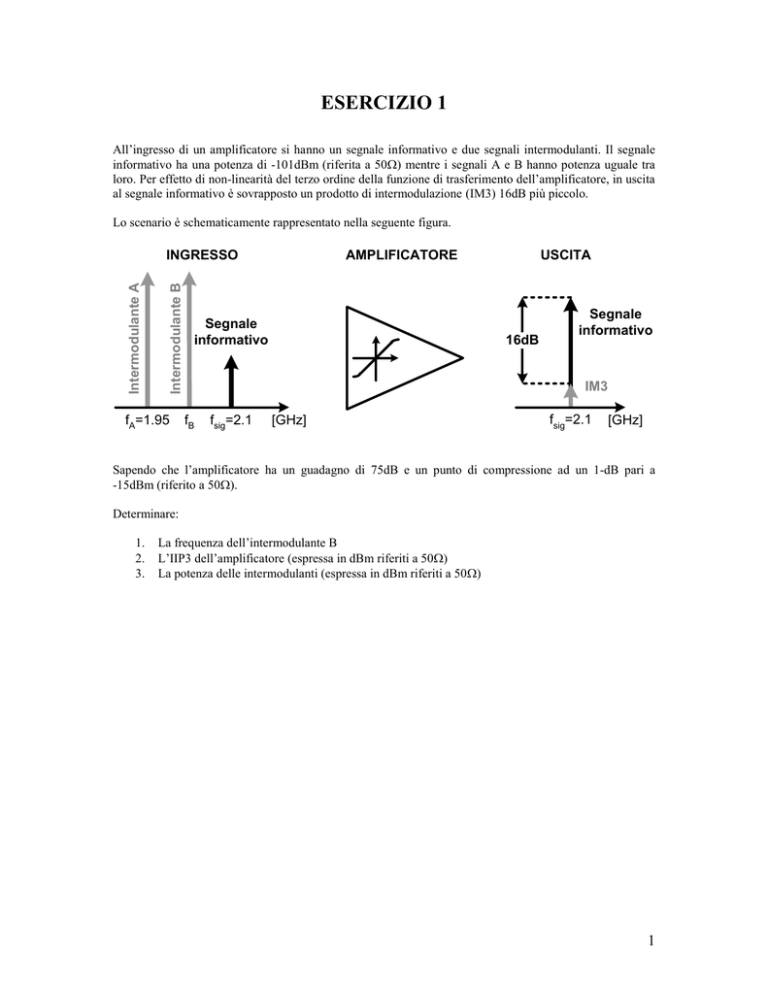

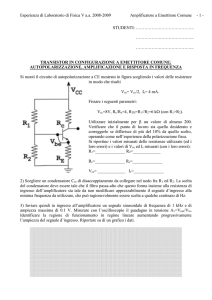

ESERCIZIO 1

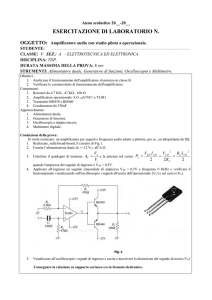

All’ingresso di un amplificatore si hanno un segnale informativo e due segnali intermodulanti. Il segnale

informativo ha una potenza di -101dBm (riferita a 50) mentre i segnali A e B hanno potenza uguale tra

loro. Per effetto di non-linearità del terzo ordine della funzione di trasferimento dell’amplificatore, in uscita

al segnale informativo è sovrapposto un prodotto di intermodulazione (IM3) 16dB più piccolo.

Lo scenario è schematicamente rappresentato nella seguente figura.

Intermodulante B

Intermodulante A

INGRESSO

fA=1.95

AMPLIFICATORE

Segnale

informativo

USCITA

16dB

Segnale

informativo

IM3

fB

fsig=2.1

[GHz]

fsig=2.1

[GHz]

Sapendo che l’amplificatore ha un guadagno di 75dB e un punto di compressione ad un 1-dB pari a

-15dBm (riferito a 50).

Determinare:

1.

2.

3.

La frequenza dell’intermodulante B

L’IIP3 dell’amplificatore (espressa in dBm riferiti a 50)

La potenza delle intermodulanti (espressa in dBm riferiti a 50)

1

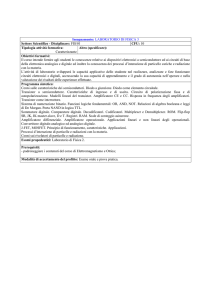

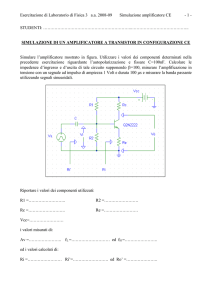

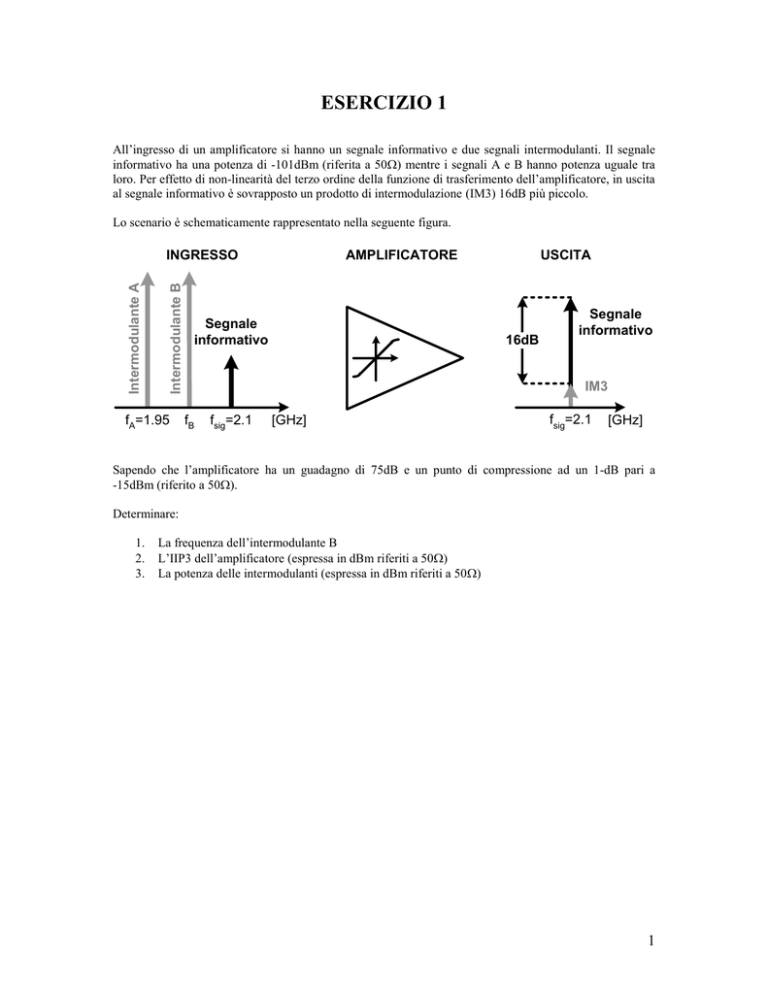

ESERCIZIO 2

Vdd

Ibias

Cload

Rload

Ibias

Cload

Vout

M3

M4

Vlo

Vbias2

M2

Cbypass

M1

Rs

Vin

LG

Rbias

CGS

Vbias1

LS

Con riferimento al circuito in figura, sapendo che:

i transistor M3 e M4 agiscono da mixer a commutazione per effetto della tensione sinusoidale Vlo

trascurando le capacità Cload, il guadagno Vout/Vin, in condizioni di adattamento d’impedenza

d’ingresso è uguale a 30dB

deve essere soddisfatta la condizione di adattamento d’impedenza d’ingresso alla frequenza di

3.5GHz

la capacità tra gate e source del transistor M1 è data dalla relazione CGS

sono noti i valori elencati nella seguente tabella:

Resistenza di sorgente

Resistenza di carico

Resistenza di polarizzazione M1

Tensione di alimentazione

Potenza totale dissipata in DC

Capacità di bypass

Lunghezza di canale di M1 e M2

Transconduttanza di processo

Tensione di soglia

Capacità dell’ossidi per unità di area

RS

Rload

Rbias

Vdd

Pdiss

Cbypass

L

nCox

Vth

Cox

2

W L Cox

3

50

1.2 k

100 k

5V

10 mW

0.25 m

120 A/V2

600 mV

7 fF/m2

2

Determinare:

1.

2.

3.

4.

5.

la larghezza del transistor M1

il valore della tensione di polarizzazione Vbias1

i valori delle induttanze LS e LG

Sapendo che la larghezza del transistor M2 è 6 volte quella del transistor M1, stabilire il valore di

Vbias2 al fine di avere la tensione di source di M2 a 1.2V

Dimensionare la capacità d’uscita per avere un taglio in frequenza a 20MHz

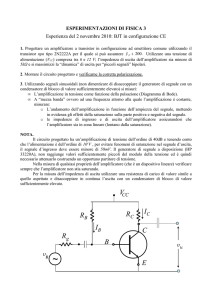

ESERCIZIO 3

Un ricevitore deve coprire 100 canali, spaziati di 200kHz, a partire da 87.5MHz. L’architettura di ricevitore

scelta prevede la conversione ad una frequenza intermedia di 10.7MHz. Si dispone di un riferimento di

frequenza ad 8MHz.

1.

2.

3.

4.

Con riferimento al sintetizzatore riportato in figura, determinare P, M, D in modo che venano

generate correttamente le frequenze di oscillatore locale richieste.

Dimensionare la frequenza di taglio del filtro d’anello, e stimare il tempo di assestamento,

richiesto per commutare da un canale all’altro.

Determinare la massima differenza di frequenza fra gli ingressi del comparatore di fase, nel caso

in cui si passi bruscamente da canale minimo a canale massimo e viceversa.

Ricavare una espressione approssimata per il campo di cattura del PLL con divisore di frequenza,

rappresentato in figura in funzione dei parametri R, C, Km, Kvco,Vi,Vo, M, D.

Kvco

Km

8 MHz

/P

R

fref

fout/M

fout

C

/(M+D)

3