Caratteristiche delle porte logiche CMOS e TTL

16. Caratteristiche delle porte logiche CMOS e TTL

Scopo della prova

Confrontare gli assorbimenti di corrente di porte logiche CMOS e TTL.

Materiali e strumentazione

1 Generatore di funzioni o d’impulsi

1 Oscilloscopio

1 Alimentatore in d.c. da + 5 V a + 15 V

1 Microamperometro per a.c. e per d.c.

1 Circuito integrato CMOS CD 4011

1 Circuito integrato TTL 74LS00

4 Condensatori da 15 pF

1 Condensatore da 2,2 µF

1 Resistore da 50 Ω.

2 Cavi coassiali di circa 50 cm di lunghezza ciascuno

1 Basetta sperimentale

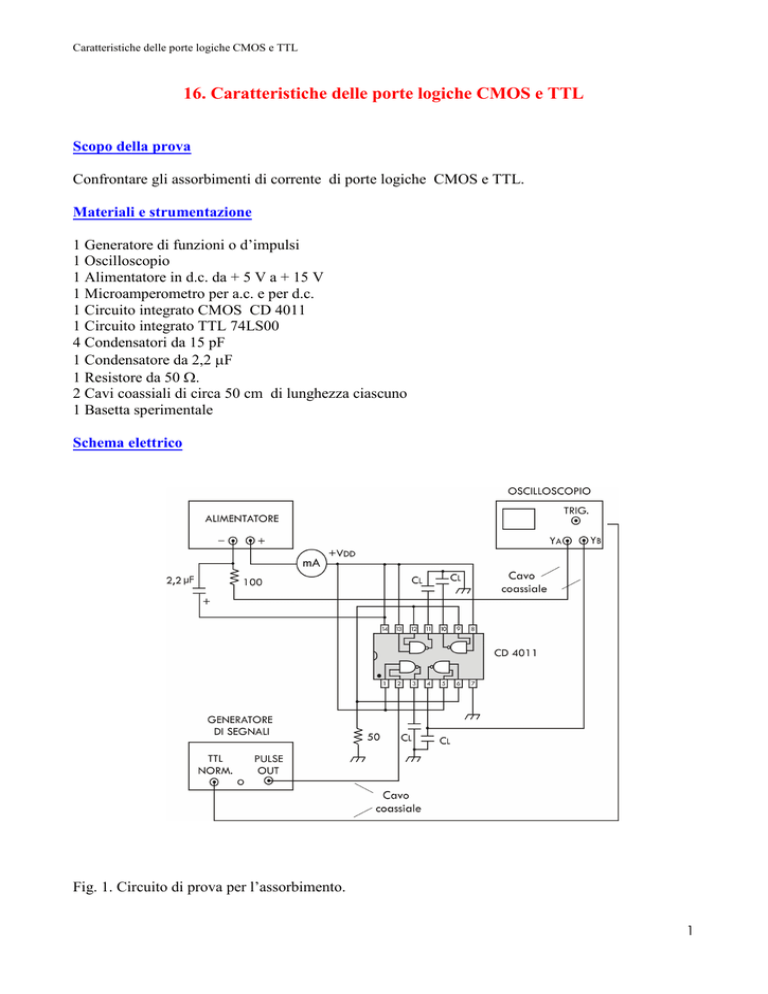

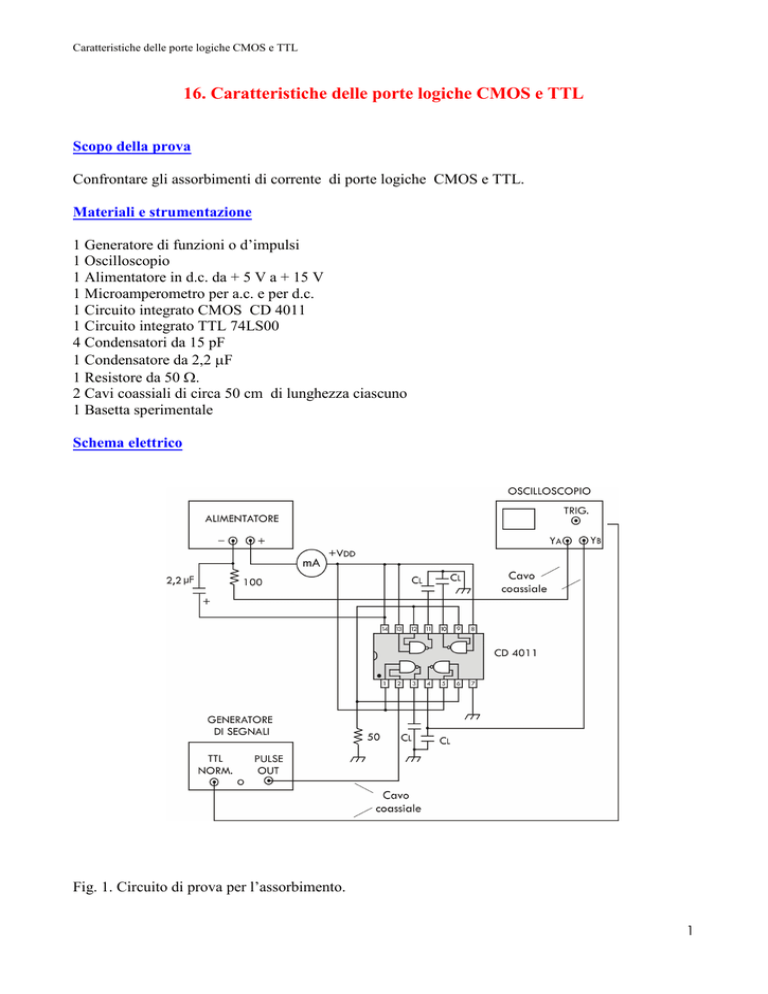

Schema elettrico

Fig. 1. Circuito di prova per l’assorbimento.

1

Caratteristiche delle porte logiche CMOS e TTL

Nozioni fondamentali

I circuiti integrati in tecnologia CMOS hanno un assorbimento di corrente molto più basso di quelli

della famiglia standard TTL ma sono più lenti a rispondere alle rapide variazioni dei segnali. Questa

marcata differenza è andata, però, diminuendo con l’introduzione sul mercato di famiglie CMOS

veloci (74HC) e di TTL a basso assorbimento (74LS e 74ALS). L’assorbimento di un circuito

integrato viene individuato misurando la corrente ricevuta dal piedino al quale è connesso il

positivo dell’alimentazione. Per la CMOS il pin è quello comunemente indicato con VDD, mentre

per la TTL è indicato con VCC. Ad essi corrispondono, rispettivamente, le correnti IDD ed ICC.

L’entità delle correnti assorbite da ciascun integrato dipende, oltre che dalla sua tecnologia, anche

dai livelli logici delle uscite delle porte logiche che lo compongono, dai carichi che queste pilotano

e dalla frequenza di lavoro (soprattutto per la CMOS). Quando gli ingressi delle porte NAND del

4011 o del 7400 sono tali che tutte e 4 le uscite si portano al livello logico alto (H), la corrente

assorbita viene indicata come ICCH. Viene indicata, invece, con ICCL se tutte le 4 uscite sono al

livello basso (L).

La velocità di risposta viene confrontata misurando i tempi di salita e di discesa delle porte logiche

realizzate nelle due diverse tecnologie. Per la CMOS (serie 4000), che ammette una tensione di

alimentazione tra +5 V e +15 V, gli assorbimenti e le velocità di risposta vengono misurati a tre

diversi valori (+5 V, +10V, +15V), mentre per la TTL tali operazioni vengono effettuate alla sola

tensione di +5 V.

Prima della prova

1. La tensione minima da applicare all’ingresso di una porta logica al di sopra della quale deve

essere riconosciuta sicuramente come livello logico alto (H) viene indicata con ……………. .

2. La tensione massima applicabile ad un ingresso che viene considerata ancora come livello logico

basso (L) è indicata con __________ .

3. La tensione _________

nominale IOH .

è la tensione all’uscita corrispondente ad una erogazione di corrente

4. La tensione minima all’uscita corrispondente ad uno stato logico alto è _________ .

5. La tensione massima di uscita corrispondente allo stato logico basso è __________ .

6. L’intensità di corrente che assorbe un ingresso quando ad esso è applicata una tensione VIH e

indicata con __________ .

7. Con IIL si indica l’intensità di corrente (di un ingresso/di un’uscita) quando vi è applicata la

tensione (VIH / VIL).

8. L’intensità di corrente che l’uscita di una porta logica assorbe, quando è al livello logico basso, è

indicata con __________ .

9. La corrente che esce da una porta logica è indicata con il segno (più / meno), mentre quella che

entra è indicata con il segno (più / meno).

10. Il valore della corrente ICC di un chip TTL di tipo 7400 standard è dell’ordine dei 2 (mA / µA).

2

Caratteristiche delle porte logiche CMOS e TTL

11. Il valore della corrente IDD di un chip CMOS di tipo 4011 è dell’ordine di 1 (mA / µA)

12. La caratteristica di trasferimento di una porta logica mette in relazione la tensione _________

con la tensione _________ .

13. La caratteristica d’uscita al livello alto di una porta logica correla la __________

__________ .

con la

14. Il tempo di salita tr di un segnale è quello che impiega per andare dal ______ % del valore

finale al ________ % del valore finale.

15. Il tempo di discesa tf di un segnale è quello che impiega per andare dal ______ % del valore

finale al ______ % del valore finale.

16. Il tempo di ritardo di propagazione di una porta logica è indicato con ________ .

17. La tensione di alimentazione dei circuiti logici TTL è fissa e vale +______V ± 5%.

18. La tensione di alimentazione dei circuiti CMOS (serie 4000) può variare tra +_____ V e

+_______ V.

Esecuzione della prova

1. Il confronto dell’assorbimento dei circuiti CMOS con quelli TTL può effettuarsi misurando

rispettivamente le correnti IDD ed ICC di due chip con identica configurazione.

2. L’assorbimento dei circuiti CMOS è molto basso ma dipende dalla tensione di alimentazione,

dall’entità del carico capacitivo posto all’uscita delle porte logiche e dalla frequenza degli impulsi.

3. Il circuito di prova per la misura dell’assorbimento del CMOS 4011 è mostrato nella figura 1.

La corrente IDD assorbita dall’integrato viene misurata mediante il microamperometro posto in serie

all’alimentazione. La sua è una indicazione del valore medio tra IDDH ed IDDL dato che all’ingresso

delle porte logiche, tramite il generatore d’impulsi, è inviato un segnale ad onda quadra che le fa

commutare tra i livelli L ed H.

4. Come indicato nel punto 2 di questa sezione, occorre effettuare le misure della corrente a varie

tensioni di alimentazione ed a varie frequenze. Per semplicità, le capacità di carico vengono

realizzate con 4 condensatori da 15 pF e vengono tenute costanti. La tabella 1 seguente è quella che

abbiamo ottenuto noi effettuando le misure.

VDD

5V

10 V

15 V

Ampiezza

Ingresso

4V

9V

14 V

Frequenza

1 kHz

3 µA

5 µA

10 µA

Frequenza

10 kHz

9 µA

10 µA

20 µA

Frequenza

100 kHz

71 µA

105 µA

130 µA

Frequenza

1 MHz

720 µA

1150 µA

2400 µA

Tabella 1

3

Caratteristiche delle porte logiche CMOS e TTL

5. Monta il circuito mostrato nella figura 1 e riempi la tabella 2 (analoga alla 1) man mano che

effettui le misure.

VDD

Ampiezza

Ingresso

Frequenza Frequenza Frequenza Frequenza

1 kHz

10 kHz

100 kHz

1 MHz

5V

10 V

15 V

Tabella 2

L’andamento dei picchi di corrente assorbita dalle porte CMOS, soprattutto durante i transitori tra i

livelli logici, può essere osservata collegando una resistenza da circa 100 Ω in serie al filo di massa

(quello che esce dal piedino 7) ed osservando, mediante un oscilloscopio, gli impulsi di tensione

che vi si producono.

6. Per la misura dell’assorbimento della corrente media ICC del circuito integrato TTL 7400, si usa

un montaggio uguale a quello mostrato nella figura 1. In questo caso la tensione di alimentazione

deve essere tenuta fissa a +5 V. Inoltre, il valore della resistenza per rilevare le forme d’onda della

corrente, mediante l’oscilloscopio, deve essere ridotto a 10 Ω perché nella TTL le correnti sono più

elevate che nella CMOS.

7. Riempi la tabella 3, analoga alla 1, man mano che rilevi gli assorbimenti per il chip TTL.

VCC

Ampiezza

Ingresso

Frequenza Frequenza Frequenza Frequenza

1 kHz

10 kHz

100 kHz

1 MHz

5V

Tabella 3

Considerazioni sulla prova effettuata

1. La corrente IDD assorbita da un circuito integrato CMOS 4011 è dell’ordine dei _______ A.

2. La corrente ICC assorbita da un circuito integrato TTL 7400 è dell’ordine dei _________ A.

3. L’assorbimento di una porta CMOS è di molto (superiore / inferiore) a quello di una

equivalente porta TTL.

4. L’assorbimento di corrente di una porta CMOS (aumenta / diminuisce) all’aumentare della

frequenza del segnale.

5. L’assorbimento di una porta TTL (varia / non varia) significativamente al variare della

frequenza del segnale.

6. L’assorbimento di una porta CMOS (aumenta / diminuisce) all’aumentare della tensione di

alimentazione VDD.

4