Elettronica Digitale

Interamente compilato in LATEXda Francesco Cerioli - www.ceccocom.it

Versione 0.1 - Aggiornata al 19 maggio 2007

1

Famiglie Bipolari

RTL - Resistor Transistor Logic

• Quando l’uscita é a ”0” non c’é Iout l’uscita é forte!

• L’uscita a ”1” é piú debole, varia a seconda dei carichi. Se piloto

tanti carichi c’é alta corrente quindi una caduta di tensione e Vout si

abbassa

• La Tfall veloce e Trise lento

• Integrazione complicata per la presenza delle resistenze

DCTL - Direct Coupled Transistor Logic

Senza Rb, purtroppo c’é uno sbilanciamento di correnti che porta ad uno

sbilanciamento di consumi.

DTL - Diode Transistor Logic

Introduce il concetto di ”carico attivo”, resistenza variabile a seconda dello

stato. In questa famiglia entrambi i livelli sono forti.

HTL - High Treshold Logic

L’immunitá al rumore é la capacitá di rigenerare un livello logico ”bello”

ricevendone uno ”brutto”. Gli HTL alzano Vcc e usano diodi Zener per

essere meno sensibili al rumore.

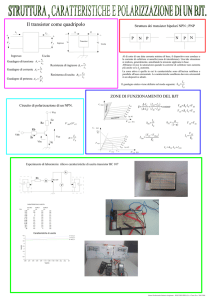

TTL - Transistor Transistor Logic

Grazie a due transistor in ”totem pole” (cioé che conducono alternativamente) risolvono il problema di scarica della base

• HTTL: Resistenze piú piccole, maggiori prestazioni ma maggiori consumi

• LTTL: Resistenze piú grosse, minori prestazioni ma minori consumi

• STTL: Molto veloce ma il consumo non é indifferente

• LSTTL: Buon compromesso tra prestazioni e consumi

1

• FTTL: Buone prestazioni e bassi consumi

• ASTTL e ALSTTL: scarso successo perché subito soppiantate dai

CMOS

ECL - Emitter Coupled Logic

Ottime prestazioni e capacitá di lavorare al alte frequenze (microonde), ma

altá sensibilità al rumore

IIL - Integrated Iniection Logic

Tentativo di realizzazione VLSI in bipolare. Soppiantata in partenza dai

CMOS.

2

CMOS

• Piú lenti dei bipolari ma ottima integrazione

• Simmetrici tra massa e Vcc, buona immunitá al rumore

• Senza resistenze perché il MOS ha giá un comportamento ohmico

• Elevata tolleranza per la Vcc

• Consumo di potenza SOLO in commutazione

Problemi principali:

• Sensibilitá a scariche ESD - si usano dispostivi esterni che evitino o

limitino il fenomeno

• Latch-up - in alcune configurazioni, quando i MOS sono molto vicini,

si creano transistor ”parassiti” che si innescano in maniera imprevista:

si effettua quindi un drogaggio che abbassi la soglia di innesco

Famiglie CMOS:

• 4000/4000B: Battono i TTL, consumi ridotti e buone prestazioni.

Ampio range di Vcc e elevata affidabilitá

• 74C: pin-to-pin compatibili con i TTL (scarso successo)

• 74HC: Molto competitiva rispetto alla TTL

• 74HCT: Possono essere direttamente interfacciati ai TTL

• 74AC: Strafaiga, rinuncia alla compatibilitá TTL ma ha elevati tempi di commutazione e dissipazione uguale ai CMOS (inoltre risolve il

problema del latch-up)

2

• 74ACT: TTL-compatibili, consumi diversi in base alla frequenza

FCMOS: é una logica di progetto che rispetta la complementarietá degli

CMOS. Funzione come una logica ad interruttori: AND in serie e OR in

parallelo. Switch: cella di memoria di base. In alcuni casi (es. nel multiplexer) puó semplificare e ridurre il numero di porte logiche necessarie per

l’implementazione.

Famiglie logiche piú recenti

• AC, ACT, FCT, sensibili a disturbi e diafonia

• ACQ, ACTQ, FCT-T, controllo slew-rate; sensibili ai livelli TTL

• LVQ, LVC, ottimizzati per tensione a 3.3 V

NB: Uno slew-rate troppo elevato porta un elevato contenuto armonico, con

conseguenti disturbi.

NB: i livelli TTL sono preferiti perché hanno meno diafonia, meno dissipazione e meno disturbi sulla massa.

BiCMOS: Stadio di ingresso e funzionale in CMOS e stadio d’uscita in

TTL (ottimo pilotaggio).

3

Parametri caratteristici

• Alimentazione e dissipazione di potenza

• Caratteristiche statiche (livelli)

• Caratteristiche dinamiche (tempi)

• Caratteristiche operative (temperatura, umiditá)

• Altre caratteristiche (package, affidabilitá)

3