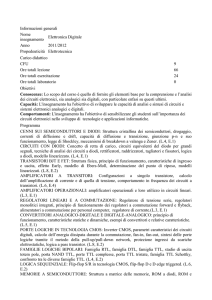

Reti logiche II

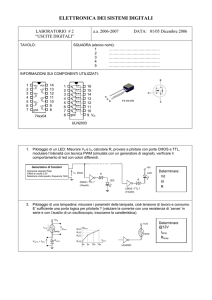

Dispositivi elettronici in commutazione. Condizioni operative statiche.

Interruttori ideali e reali. Condizioni operative statiche del transistore a giunzione. Condizioni

operative all'interdizione. La fuga termica.

Condizioni operative in saturazione. Dissipazione negli stati di riposo.

Condizioni operative statiche dei transistori a effetto di campo. Il JFET. Il MOSFET.

I dispositivi elettronici. Condizioni operative dinamiche.

Introduzione. Il transistore a giunzione. Le regioni di operazione. Capacita’ di transizione e

capacita’ media integrale. I tempi di commutazione.

Il modello a controllo di carica. Il calcolo dei tempi di commutazione con il modello a controllo di

carica. Il tempo di ritardo iniziale. Il tempo di salita. Il tempo di restituzione. Il tempo di discesa.

Guadagno transitorio di corrente in saturazione. Effetto delle capacita' esterne sui tempi di

commutazione. Pilotaggio di corrente e pilotaggio di tensione.

I parametri del transistore nel modello a controllo di carica. Comportamento dinamico dei

dispositivi MOS.

I diodi a giunzione. I tempi di ripristino. Tempo di ripristino diretto. Tempo di ripristino inverso.

Calcolo dei tempi di ripristino.

I diodi Schottky.

I circuiti logici.

Introduzione. Caratteristica di trasferimento e valori garantiti per le tensioni. Il margine di rumore. I

valori garantiti per le correnti.

Le famiglie logiche e i dispositivi logici integrati. Considerazioni generali. Caratteristiche di

temporizzazione di flip-flop e registri. Tempo di propagazione. Specifiche di temporizzazione degli

ingressi.

Le famiglie logiche. Cenni sulle famiglie bipolari “storiche”. La famiglia RTL . La famiglia DTL.

La famiglia HTL

La famiglia TTL. La sottofamiglia TTL standard. Caratteristica di trasferimento. Tensioni e correnti

di ingresso e di uscita. Impedenze di ingresso e di uscita.

Le sottofamiglie TTL.

Conclusioni sulla famiglia TTL.

La famiglia ECL. Caratteristica di ingresso. Caratteristica di trasferimento e immunita’ al rumore.

Attitudine al pilotaggio di linee. Comportamento dinamico. Conclusioni sulla famiglia ECL.

I dispositivi MOS. Logica MOS statica. Logica MOS dinamica. MOS dinamici a rapporto minimo.

La famiglia CMOS. Caratteristica di trasferimento. Comportamento al variare della tensione di

alimentazione. Immunita’ al rumore. Struttura delle porte logiche. Considerazioni generali sull’uso

della famiglia CMOS. Cenni sulla logica CMOS domino. La classificazione dei componenti

integrati.

Classificazione delle memorie. Struttura base di una memoria. Struttura della cella di memoria

RAM. Struttura di una cella RAM statica. Struttura di una cella RAM dinamica. Struttura di una

memoria RAM dinamica.

I

Le ROM a maschera. La cella di memoria EPROM ed EEPROM. Le ROM programmabili

(PROM). I dispositivi logici programmabili. La logica a matrice programmabile (PAL). Le matrici

logiche programmabili (PLA). I gate array programmabili (PGA) e i dispositivi ad elevata

complessita’.

I sistemi di interconnessione.

Introduzione. Il modello a strati. Il livello elettrico. Effetto delle linee nelle comunicazioni a lunga

distanza. Scelta dei trasmettitori e dei ricevitori di linea. I protocolli. Il protocollo di ciclo. Il

protocollo a livello transazione. Caratteristiche principali di alcuni bus reali.

II