DISPOSITIVI E CIRCUITI

INTEGRATI

Corso di recupero in Fondamenti di Elettronica – Università di Palermo

A.A. 2014-2015

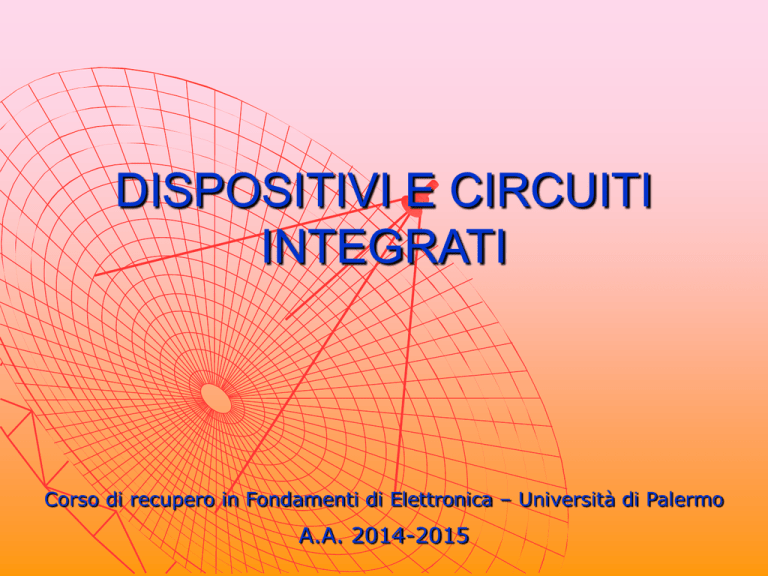

Preparazione del monocristallo:

Metodo di Czocralsky

Tecnologia planare

1) formazione dello strato

epitassiale

2) formazione dello strato di

biossido di silicio

3) rimozione selettiva del biossido

tramite fotolitografia

4) diffusione o impiantazione ionica

delle impurità droganti

5) metallizzazione

SiO2

Si

fotoresist

SiO2

Si

- Ossidazione

Fotolitografia

- Preparazione per la fotolitografia

luce U.V.

lastra di vetro con

zone opache

- Esposizione attraverso la maschera

- Rimozione del resist esposto (sviluppo)

- Attacco del SiO2 con acido fluoridrico

- Rimozione del resist non esposto

- Introduzione delle impurità (drogaggio)

Esempio di dispositivo integrato

(CMOS)

Carico attivo

vgs2 = 0

vGS = 0

i

v = RDdii carico

retta

1/ RD

v

VDD

A

vo

g m1 ro1 // ro 2

vi

(ro2 » RD)

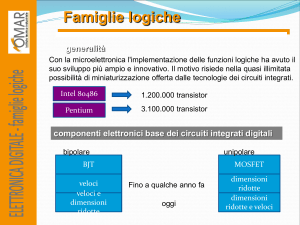

Evoluzione famiglie logiche

SSI (Small Scale Integration), massimo di dieci porte logiche

VLSI

MSI (Medium Scale Integration), da dieci a cento porte logiche

LSI (Large Scale Integration), da cento a mille porte logiche

SSI, MSI, LSI

VLSI (Very Large Scale Integration), numero di porte logiche > mille

4 pJ

1,5 ns

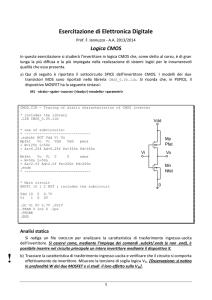

Caratteristiche famiglie logiche

TTL

CMOS

• Tensione di alimentazione VCC

4,5-5,5 V

• Corrente di alimentazione ICC

10 mA

≈0

• Potenza dissipata Pd

10 mW

10 nW

0,8 V

2V

0,4 V

2,4 V

VCC /3

2·VCC /3

≈0

≈ VCC

• Livelli di tensione di ingresso e di uscita:

VILmax

VCC

VCC

VIHmin

VOHmin

VIHmin

circuito

VOLmax

integrato

VOHmin

V

ILmax

0

VOLmax

0

3-18 V

Caratteristiche famiglie logiche

TTL

• Livelli di corrente di ingresso e di uscita:

IILmax

IIHmax

IOLmax

IOHmax

1,6 mA

40 mA

16 mA

400 mA

CMOS

1 pA

1 pA

1 mA

1 mA

Caratteristiche famiglie logiche

• Fan-out sul livello alto FOH

• Fan-out sul livello basso FOL

I OH max

I IH max

I OL max

I IL max

• Corrente di cortocircuito Ios

• Tempi di commutazione

tp =

TTL

CMOS

10

50

10

50

30 mA

5 mA

10 ns

100 ns

MOSFET in commutazione

Vo = VDD

DS(ON)

VGS >

< Vt

VDS(ON)

RD » rON

Famiglia CMOS

-VDD0==

Conduzione: VGS < Vt (negativa)

PMOS

VDD

VDD

Conduzione: VGS > Vt (positiva)

NMOS

VDD0 =

inverter

Famiglia CMOS

CMOS: protezione ingressi

CMOS: dissipazione di potenza

Caratteristiche CMOS

Open collector/open drain

Si può alimentare la resistenza di pull-up RC con una

tensione diversa da quella propria della porta logica

Buffer (Driver)

• Pilotaggio di lampade, relè, linee, ecc.

• Uscita (tipica) in open drain

01

VOH(max) = 30 V

IOL(max) = 40 mA

RL = 1,3 kW

Va VOL

= 18 mA (< 40 mA)

IL

RL

Porte three-state

A

0

1

G

1

1

Y

0

1

×

0

Z

A

G

Y

= 01

0

0

0

1

0

1

×

1

Z

L’ingresso d’abilitazione deve rendere interdetti entrambi i

MOSFET

Trigger di Schmitt

jitter

Porte di trasmissione

=1

=0

Se C = 1 i transistor sono accesi e i punti 1 e 2 sono connessi

dalla bassa rON dei due MOSFET in parallelo

Se C = 0 i transistor sono entrambi interdetti e 1 e 2 sono scollegati

Pilotaggio TTL-LED

Con ACMOS-ACTMOS:

Pilotaggio CMOS (4000B)-LED

oppure per aumentare la corrente d’uscita…

max 0,44 mA

… e in tutti quei casi in cui non si è sicuri se l’integrato è in grado

di erogare corrente sufficiente a fare accendere i LED