Breve monografia sullo

SCHMITT-TRIGGER a CMOS

sussidio didattico per l'insegnamento di ELETTRONICA (N.O.)

(Corso di laurea in Ingegneria Informatica)

Docente: Prof. Enrico CALANDRA

Come discusso più ampiamente nel libro di testo adottato, i circuiti "comparatori di soglia

con isteresi" (colloquialmente denominati "Schmitt-Trigger" – ST, dall’ideatore della prima loro

implementazione hardware – ormai lontana nel tempo – basata sull’uso tubi a vuoto, o "valvole")

sono dei blocchi costitutivi elementari di notevole importanza applicativa, sia per la

"rigenerazione" dei segnali digitali corrotti da distorsioni o interferenze, sia come macrocomponenti attivi per la realizzazione di circuiti generatori d’onda (quale il semplice circuito

astabile riportato, a titolo d’esempio, a conclusione di questa breve monografia).

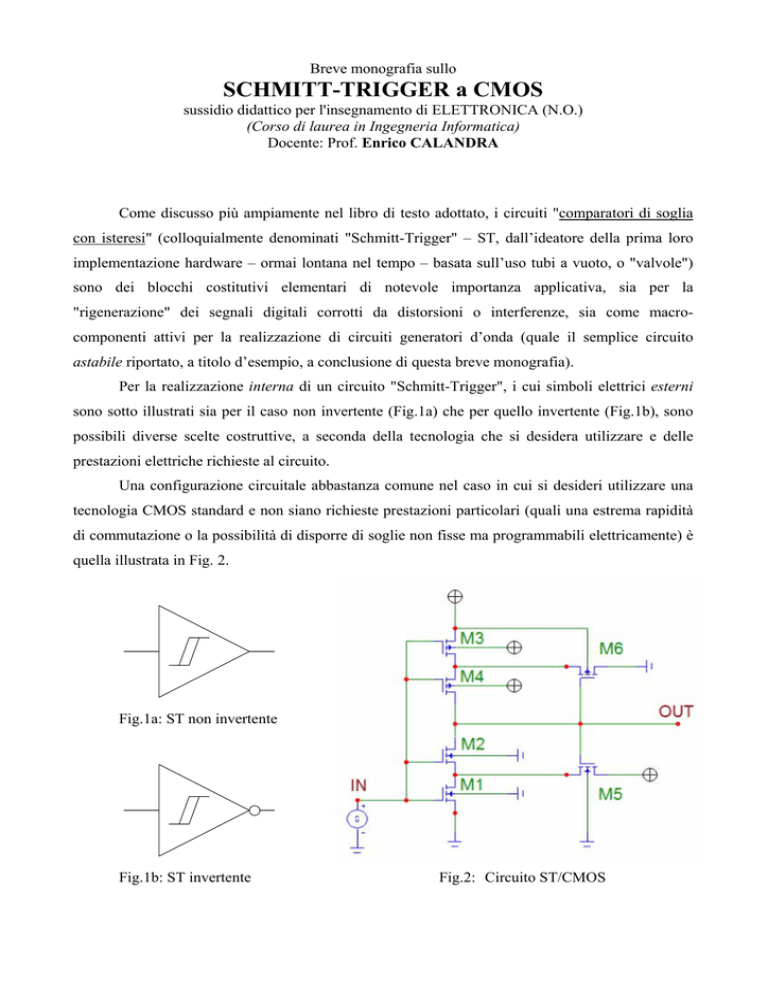

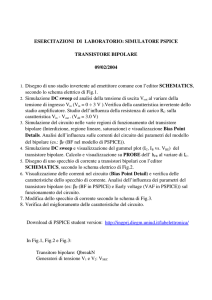

Per la realizzazione interna di un circuito "Schmitt-Trigger", i cui simboli elettrici esterni

sono sotto illustrati sia per il caso non invertente (Fig.1a) che per quello invertente (Fig.1b), sono

possibili diverse scelte costruttive, a seconda della tecnologia che si desidera utilizzare e delle

prestazioni elettriche richieste al circuito.

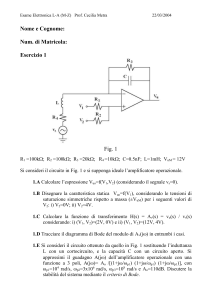

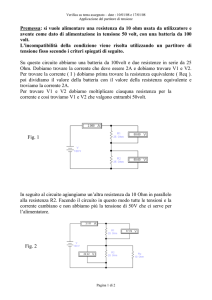

Una configurazione circuitale abbastanza comune nel caso in cui si desideri utilizzare una

tecnologia CMOS standard e non siano richieste prestazioni particolari (quali una estrema rapidità

di commutazione o la possibilità di disporre di soglie non fisse ma programmabili elettricamente) è

quella illustrata in Fig. 2.

Fig.1a: ST non invertente

Fig.1b: ST invertente

Fig.2: Circuito ST/CMOS

Per comprendere il funzionamento di base di tale dispositivo è possibile innanzitutto partire

dallo studio dell’inverter CMOS a quattro transistori (due NMOS e due PMOS) illustrato in Fig. 3.

Fig.3: Circuito inverter CMOS a quattro transistori

In tale inverter, i due transitori NMOS (PMOS), connessi in serie ma con i gate uniti,

formano una transistore "equivalente" di tipo NMOS (PMOS) ed il principio di funzionamento di

tale porta è sostanzialmente analogo a quello di una porta standard con una sola coppia di

transistori NMOS/PMOS. In ipotesi di perfetta complementarietà, quindi, la "soglia di

commutazione" (ossia la tensione di ingresso alla quale si attraversa la regione attiva e la tensione

di uscita cambia "valore logico") si troverà – come usuale – centrata intorno a VDD/2. Se però,

come anche in un inverter standard, la tensione di soglia del transistore “equivalente” NMOS

(PMOS) dovesse aumentare (diminuire) la soglia di commutazione si sposterebbe verso tensioni

superiori (inferiori) a VDD/2.

Ciò posto, è evidente che se è possibile dimostrare che i due transistori addizionali M5 ed

M6 presenti nel circuito di Fig.2, svolgano un ruolo tale da causare – rispettivamente – un aumento

della tensione di soglia del transistore equivalente NMOS (M1+M2) quando la tensione di uscita è

alta, ed una diminuzione della tensione di soglia del transistore equivalente PMOS (M3+M4)

quando la tensione di uscita è bassa, ecco dimostrata la differenza esistente fra la soglia di

commutazione del circuito di Fig.2 quando "si proviene da tensioni basse" rispetto a quando "si

proviene da tensioni alte", ossia la sua natura di "comparatore di soglia con isteresi" (o "SchmittTrigger") CMOS.

Dimostrare a livello qualitativo l’affermazione di cui sopra è abbastanza immediato.

Supponendo, infatti, di partire da una tensione di ingresso inferiore alla tensione di soglia VTH1 del

transistore M1 (qui ipotizzata per semplicità eguale a quella del transistore M2 ed opposta rispetto

a quelle dei transistori M3 ed M4: VTH1=VTH2=-VTH3=-VTH4=VTH) i due transistori M1 ed M2

saranno OFF, l’uscita sarà HIGH ed il transistore M5 sarà quindi con gate e drain entrambi HIGH. I

transistori M1 ed M5 si comporteranno come device ed active load di un inverter NMOS/ENH con

carico NMOS/ENH e la tensione VDS1 sarà quindi pari a VDD-VTH5. Sebbene al crescere della

tensione di ingresso al di sopra di VTH1 il transistore M1 inizi a condurre e la tensione VDS1 cominci

a diminuire rispetto al suddetto valore, tale valore resterà comunque maggiore di zero e quindi

occorrerà che VIN raggiunga valori maggiori di VTH2 perché anche M2 cominci a condurre. Quindi

il transistore NMOS equivalente "M1+M2" possiederà una soglia equivalente maggiore di VTH2,

mentre, essendo VOUT ancora HIGH, il transistore M6 sarà OFF e non modificherà

apprezzabilmente la tensione di soglia del transistore PMOS equivalente "M3+M4", creando

l’asimmetria (in questo caso desiderata) fra NMOS e PMOS e lo spostamento al di sopra di VDD/2

della soglia di commutazione per tensioni di ingresso "crescenti". Naturalmente, una volta che la

tensione di uscita comincia a scendere, l’effetto di M6 comincerà a farsi sentire sul transistore

PMOS equivalente, complicando il calcolo esatto, ma non l’aspetto qualitativo del ragionamento

fatto.

Un ragionamento duale può essere condotto partendo da VIN HIGH (e quindi VOUT LOW)

ed andando verso LOW, per dimostrare che la soglia di commutazione del circuito si sposterà al di

sotto di VDD/2 per tensioni di ingresso "decrescenti".

A titolo d’esempio viene riportato, in Fig. 4, l’andamento (simulato al calcolatore) del ciclo

di isteresi di un ST/CMOS, in cui VDD=5 e {|K|=1.5E-4, |λ|=0.01, |VTH|=1.5, γ=0} per tutti i MOST.

Fig. 4: Transcaratteristica IN/OUT dello ST/CMOS di Fig. 2.

Per fornire un esempio d’uso del circuito ST/CMOS presentato differente da quello classico di

"rigeneratore" di forme d’onda, si propone di seguito il suo impiego nella realizzazione di un

oscillatore ad onda quadra per basse frequenze, secondo lo schema illustrato in Fig.5, analogo a

quello illustrato a lezione, ma da intendersi particolarizzato per la configurazione circuitale dello

ST (ed i relativi valori dei parametri) qui considerata. In tale circuito, il regime periodico stabile

verrà raggiunto pressoché subito (ossia, dopo il primo

(1)

(2)

transitorio di carica del condensatore) e le forme d’onda

saranno quelle riportate nelle Figg. 6a e 6b, relative alle

tensioni ai nodi (1) e (2), rispettivamente. Al grafico della

tensione al nodo (1) è stato sovrapposto l’andamento

1 MΩ

dell’esponenziale di prima carica del condensatore (supposto

100 pF

scarico per t=0), per mostrare come il metodo approssimato

utilizzato a lezione per la determinazione delle forme d’onde

in tale circuito risulti, a bassa frequenza, più che adeguato

Fig.5: Circuito astabile con ST.

per

il calcolo del periodo (e dell’ampiezza) dell’onda

quadra generata. L’unica difficoltà rimane, quindi, quella del

calcolo esatto delle due tensioni di soglia dello Schmitt-Trigger CMOS (qui ricavate dal grafico di

Fig.4 e pari a 1.72V e 3.28V, vedi anche grafico di Fig. 6a), argomento - qui - non ulteriormente

approfondito, poiché al di fuori del programma del Corso.

Fig.6a: Forma d’onda al nodo (1), in blu, con, in rosso, l’esponenziale generatrice.

Fig.6b: Forma d’onda al nodo (2).