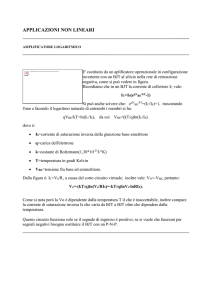

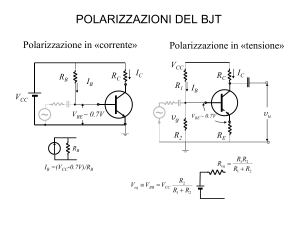

Amplificatore a BJT in

configurazione CE e CC

Traccia per lo svolgimento

dell’esercitazione del 27 maggio 2008

1

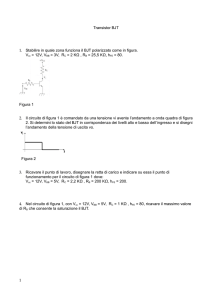

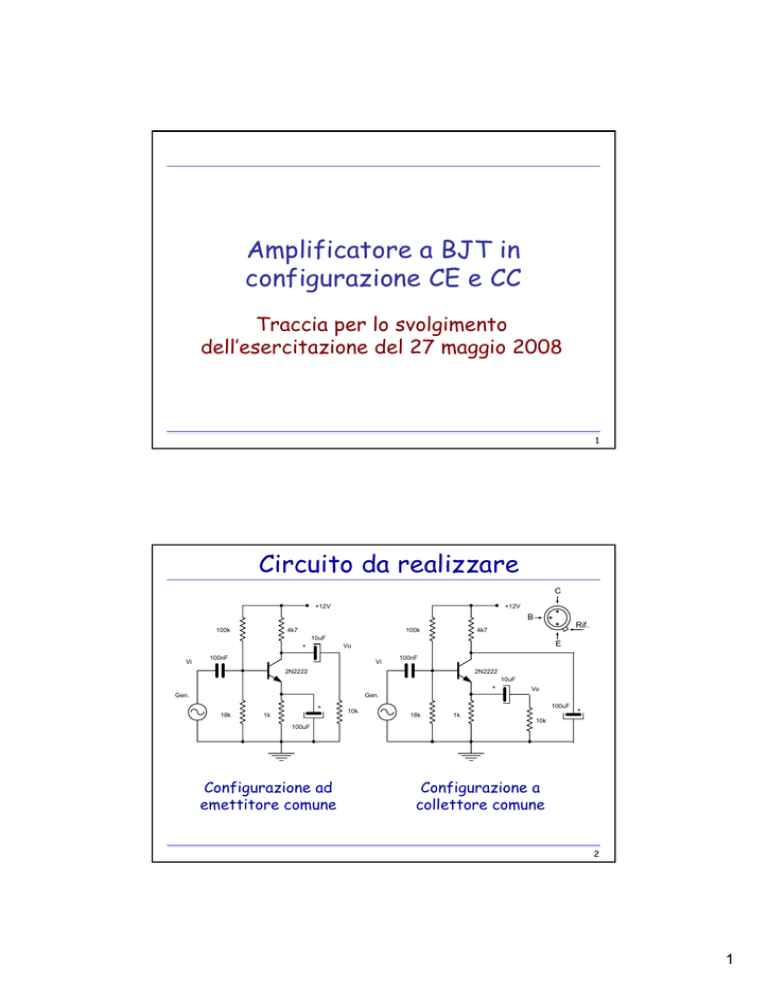

Circuito da realizzare

C

+12V

+12V

B

100k

4k7

100k

Rif.

4k7

10uF

+

Vi

E

Vo

100nF

Vi

100nF

2N2222

2N2222

10uF

+

Gen.

Vo

Gen.

+

18k

1k

10k

100uF

18k

1k

+

10k

100uF

Configurazione ad

emettitore comune

Configurazione a

collettore comune

2

1

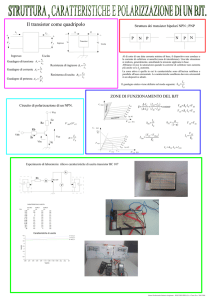

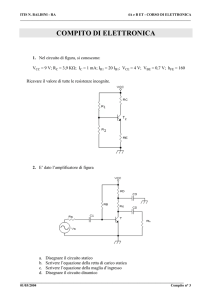

Analisi teorica preliminare

• Analisi in DC – Studio della polarizzazione

– In DC i vari condensatori sono considerati dei circuiti

aperti, si studia dunque il circuito:

VCC

Si calcola

l’equivalente

Thevenin tra i VCC

due punti

contrassegnati con x

RC

R1

x

R2

RE

VBB

x

x

x

R2

x

VBB = VCC

RB

R1

x

R2

R1 + R2

RB = R1 // R2 =

Con:

R1 = 100 kΩ,

R2= 18 kΩ,

R1 R2

R1 + R2

Vcc=12 V

3

Analisi teorica preliminare

• Possiamo quindi studiare il circuito equivalente:

Ipotizzando il funzionamento del

transistor in zona attiva si ha:

RC = 4.7 kΩ

RE = 1 kΩ

RC

RB

x

VBB

IB

B

IC = β F I B

IC

C

VCC

E

RE

IE

IB =

VBB = RB I B + VBE + RE I E

= RB I B + VBE + RE ( β F + 1) I B

x

Da ciò:

I E = ( β F + 1) I B

Dalla legge di Kirkhhoff di

tensione:

VBB − VBE

RB + RE ( β F + 1)

IC = β F I B =

Per il calcolo si possono ipotizzare

VBE= 0.65 V e β0 = 150

β F (VBB − VBE ) I = ( β + 1) I = ( β F + 1)(VBB − VBE )

E

F

B

RB + RE ( β F + 1)

RB + RE ( β F + 1)

4

2

Analisi teorica preliminare

• E si possono ricavare anche le tensioni nei vari

punti del circuito:

V E = RE I E

RC = 4.7 kΩ

RE = 1 kΩ

RC

RB

x

VBB

IB

B

VB = VBB − RB I B

IC

C

VCC

E

RE

IE

x

Si può così ricavare il punto di

lavoro del BJT, caratterizzato

dalla coppia di valori:

VCE e IC

VC = VCC − RC I C

da cui si può ricavare:

VCE = VC − VE

VCB = VC − VB

La verifica che VCE sia maggiore di

VCEsat garantisce che sia verificata

l’ipotesi iniziale e cioè che il

transistor lavori in zona attiva

5

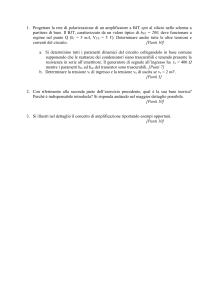

Verifica della polarizzazione con PSpice

Il transistor 2N2222 usato

per l’esercitazione è

presente nella libreria di

PSpice

Per la determinazione del

punto di lavoro è

sufficiente l’analisi “Bias

Point Detail” che risulta

abilitata di default nel

menù Setup

Cliccando sulla V e la I

presenti nella barra superiore

è possibile visualizzare tensioni

e correnti nei vari punti del

circuito, determinando così il

punto di lavoro del transistor

6

3

Verifica della polarizzazione con PSpice

Dalla simulazione il punto di lavoro risulta dunque:

Ic=1.074 mA, VCE= 5,87 V

7

Considerazioni sulla presenza dei

condensatori

• Con riferimento alla configurazione CE

I condensatori Cs e CL sono detti

condensatori di blocco o di accoppiamento

RL=10 kΩ

+ VCC

R1

Cs

RC

Vs

CL

CE

R2

CS=100nF

CE=100uF

CL=10uF

RE

La loro funzione è quella di isolare la

polarizzazione in continua dal generatore

di segnale e dal carico.

Il loro valore è scelto in modo tale che la

RL loro impedenza risulti trascurabile

(cortocircuito) alla minima frequenza del

segnale Vs.

Il condensatore CE, detto condensatore

di bypass, ha anch’esso impedenza

trascurabile alla freq. di Vs e fa sì che

per il segnale, l’emettitore risulti a

massa, pur essendo, in continua, il punto

di lavoro stabilizzato dalla RE

8

4

Analisi teorica preliminare

• Analisi in AC – Studio (semplificato) della

configurazione ad emettitore comune

Nel circuito si sostituisce al BJT il suo modello ai piccoli segnali,

considerando le capacità come cortocircuiti.

(Il modello ai piccoli segnali utilizzato è semplificato e trascura la resistenza di

dispersione di base e la ro che tiene conto dell’effetto Early)

R1// R2

Vs

Dal punto di lavoro è possibile

ricavare gm:

V è l’equivalente in

C

B

+

rπ

+

vπ

-

RC

E ic=gmvπ

Da cui il guadagno di tensione:

gm =

IC

VT

T

volt della temperatura,

pari a circa 25 mV a

temp. ambiente

RL

vο

- vo = −( RC // RL )ic = −( RC // RL ) g m v s

essendo in questo caso vπ = vs

AvCE =

vo

R R

= − C L gm

vs

RC + RL

9

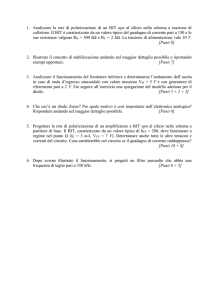

Analisi simulativa della config. CE

Disegnata la rete completa, si imposta un’analisi di tipo AC sweep, per

determinare i diagrammi di Bode della FdT Vo/Vs

10

5

Analisi simulativa della config. CE

Nelle regioni di media frequenza il guadagno è di circa 42 dB, pari ad un

AVCE= -126

Come si spiega la diminuzione del guadagno nelle zone di bassa e alta

frequenza?

11

Analisi simulativa della config. CE

La diminuzione del guadagno nella

zone di bassa frequenza è dovuta

prevalentemente all’effetto della

capacità Cs, la cui impedenza, a freq

basse non è più trascurabile.

Una stima del suo effetto si può

fare, considerando nell’analisi in

AC, il seguente circuito

Cs

C

B

+

rπ

Vs

vπ

RC

RL

i =g v

- E c m π

vo = −( RC // RL ) g m vπ

R1// R2

Posto:

R x = R1 // R2 // rπ

Con: rπ = β 0 g m

vπ =

Rx

1

R +

(Assunto β0 = βF) x sC s

vs

vo

sC s R x

= − g m ( RL // RC )

vs

sC s R x + 1

12

6

Analisi simulativa della config. CE

vo

sC s R x

= − g m ( RL // RC )

vs

sC s R x + 1

Struttura tipica di una funzione

passa alto

vo

sτ

= AVo

vs

sτ + 1

A determinare l’andamento del guadagno a frequenze ancora più basse

interviene l’effetto delle capacità CE e CL, che sono di due o tre ordini

di grandezza maggiori della CS

Cμ

B

C

rπ + C

π

vπ

-

E ic=gmvπ

Diversamente, l’andamento del guadagno in alta

frequenza è dovuto al fatto che lì si fanno sentire gli

effetti delle capacità interne del BJT, Cπ (capacità di

diffusione B-E) e Cμ (capacità di svuotamento della zona

B-C) presenti nel BJT

13

Analisi simulativa nel dominio del tempo

•

•

Utilizzando lo stesso schematico del test precedente, ma sostituendo al

generatore VAC un generatore VSIN si può impostare un’analisi nel

dominio del tempo di tipo “transient”.

Aumentando l’ampiezza del segnale d’ingresso è possibile osservare la

saturazione del BJT

VCE

La VCE ha il valore minimo

tipico della saturazione

Vs*100

Tensione d’uscita Vo, con tratti che mostrano la

saturazione del BJT

14

7

Cenni all’analisi della configurazione CC

+ VCC

R1

Cs

RC

R2

RE

CL

Vs

CE

RL

• Analisi in DC – Polarizzazione

Per quanto riguarda la polarizzazione e quindi il punto di lavoro

del BJT, esso è ovviamente il medesimo rispetto a quanto

calcolato per la configurazione a emettitore comune.

15

Analisi teorica preliminare

• Analisi in AC – Studio (semplificato) della

configurazione a collettore comune

Anche in questo caso si sostituisce al BJT il suo modello ai piccoli

segnali, considerando le capacità come cortocircuiti.

(Il modello ai piccoli segnali utilizzato è semplificato e trascura la resistenza di

dispersione di base e la ro che tiene conto dell’effetto Early)

Il procedimento di calcolo per la determinazione del guadagno di tensione è

analogo a quello visto per la configurazione CE. E’ sufficiente disegnare

correttamente il circuito ai piccoli segnali

rπ

E

B

Si deriva:

R1// R2

+

+ v Vs

vo

( RE // RL )( β 0 + 1)

π

RE

RL AvCC = v = r + ( R // R )( β + 1)

s

π

E

L

0

vο

C ic=gmvπ

Essendo: rπ << ( RE // RL )( β 0 + 1)

Schema ai piccoli segnali

A

≈1

vCC

16

8

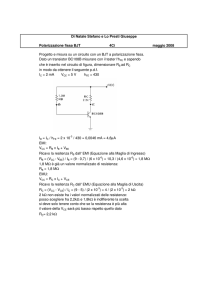

Analisi simulativa della config. CC

Disegnata la rete completa, si imposta un’analisi di tipo AC sweep, per

determinare i diagrammi di Bode della FdT Vo/Vs

17

Analisi simulativa della config. CC

Nelle regioni di media frequenza il guadagno è di circa 0 dB, cioè circa unitario

In bassa frequenza incide ancora il condensatore d’accoppiamento Cs

18

9

Accorgimenti operativi

• Per lo svolgimento dell’esercitazione:

- Fare attenzione all’impiego di

condensatori elettrolitici, dei quali è

necessario rispettare la polarità!

- +

19

Accorgimenti operativi

• Se dovesse essere necessario per ridurre

l’ampiezza del segnale in ingresso ed evitare

distorsione del segnale d’uscita, introdurre,

prima del condensatore Cs un partitore resistivo,

impiegando le resistenze da 10 Ω e 1 kΩ:

1 kΩ

Vs

Cs

Vi

10 Ω

20

10