ISTITUTO TECNICO INDUSTRIALE STATALE “OTHOCA”

A.S. 2011-2012

Classe: IIID - Programma di elettronica

Docenti: Franco Sardu e Lorenzo Bruno

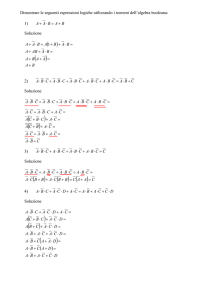

ELETTRONICA DIGITALE : elementi di algebra booleana, funzioni logiche AND OR

NOT NAND NOR XOR, i teoremi dell'algebra booleana (annullamento,dei complementi,

dell'idempotenza, d'identità, dell'assorbimento, dell'involuzione, di De Morgan), proprietà

delle operazioni booleane, forme canoniche del prodotto e della somma, gruppi di porte

logiche universali, il metodo dei mintermini per pervenire all'espressioni booleane, le

mappe di Karnaug, la decomposizione funzionale, gli stati di indifferenza;

I CIRCUITI IN LOGICA COMBINATORIA: decorder, encoder con priorità, multiplexer e

demultiplexer, half-adder e full-adder, sommatori a 4 bit, ALU;

I CIRCUITI IN LOGICA SEQUENZIALEi: multivibratori bistabili, latch S-R, flip-flop

temporizzati, f-f tipo S-R e J-K, (p.e.t.-n.e.t.); f-f in configurazione D e T, contatori

asincroni e sincroni; sequenziatori sincroni con o senza ingressi, memorie a

semiconduttore .

ESERCITAZIONI DI LABORATORIO:

1. Verifica della tabella di verità per porte logiche TTL e CMOS;

2. Verifica dei teoremi booleani e del metodo dei min-max termini mediante circuiti

logici implementati con porte logiche TTL e CMOS ;

3. Verifica sperimentale sull’universalità delle porte logiche NAND e NOR e delle

rispettive decomposizioni funzionali;

4. Realizzazione, previa progettazione, di decoders con successiva verifica

sperimentale della tabella di verità per il tipo commerciale 7442 e del decoder

driver 7447 pilotante un display a sette segmenti;

5. Verifica sperimentale della tabella di verità per encoders tipo SN74LS148;

6. Realizzazione, mediante porte logiche, di mux a 4 ingressi;

A

7. Verifica sperimentale di funzionamento di MUX/DEMUX 74150-74151, con

connessione tra i due componenti;

8. Verifica sperimentale del funzionamento di un sommatore a 4 bit ottenuto

mediante IC 4008;

9. Verifica sperimentale di funzionamento di una ALU 74181;

10. Verifica sperimentale di funzionamento di f-f JK NET 74107 (NET) e 74109 (PET);

11. Realizzazione e simulazione al computer di contatori asincroni/sincroni, in avanti e

all’indietro, a modulo binario e non binario;

12. Realizzazione di sequenziatori sincroni con ciclo condizionato da un ingresso.

Costituiscono parte integrante del presente programma anche tutte le esercitazioni

numeriche svolte in classe.

Oristano, 9 giugno 2012

Gli Insegnanti

Gli Alunni

B