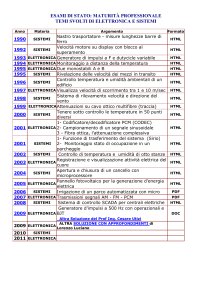

Elettronica I –16/1/2017

Nome e Cognome (stampatello):______________________________Matricola:________________

Tipo e Numero di documento:________________________________Firma:___________________

note: firmare e indicare su ogni foglio consegnato nome, cognome e matricola; il presente foglio va consegnato unitamente

all’elaborato; è consentito solo l’uso della calcolatrice; il risultato della prova sarà pubblicato sul sito personale del docente.

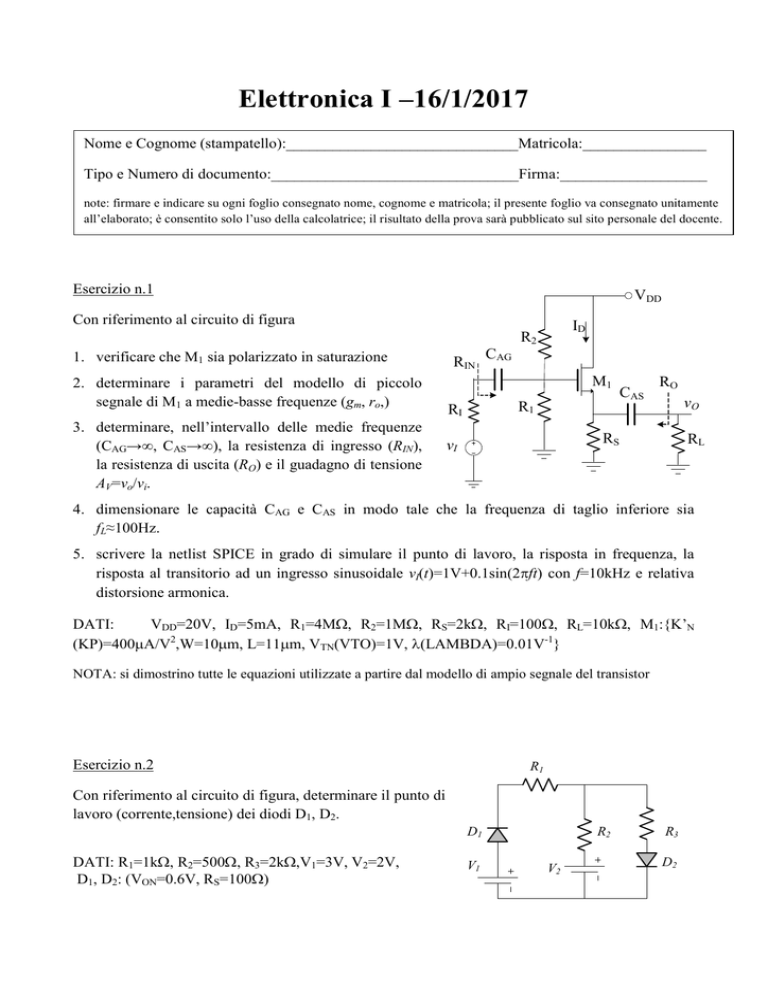

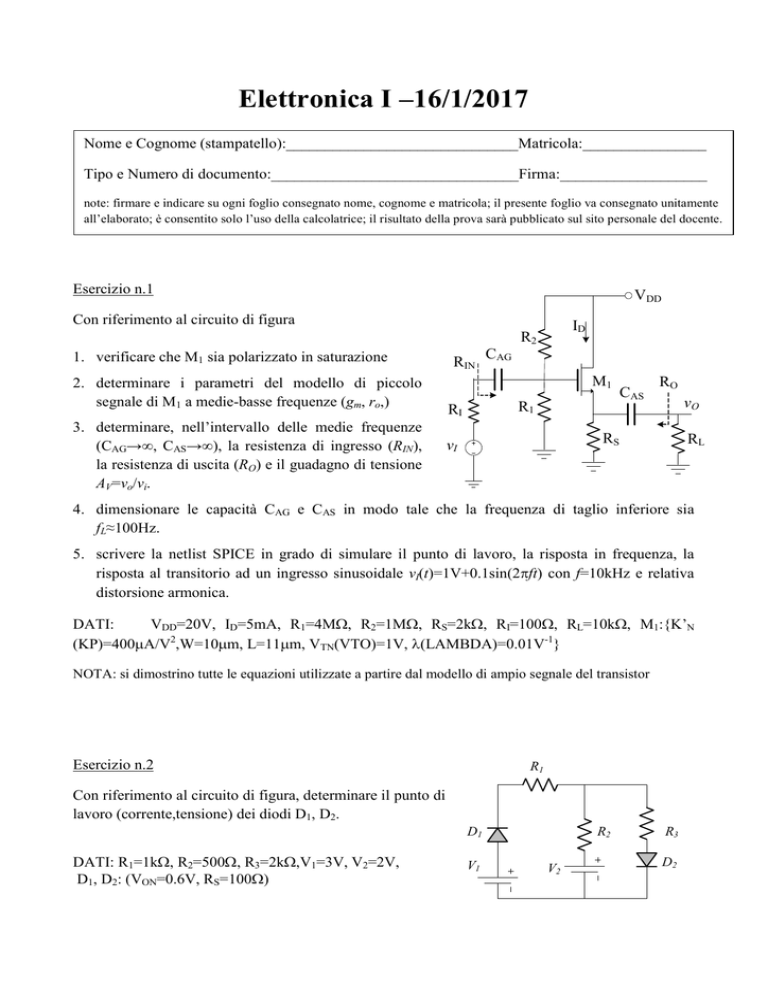

Esercizio n.1

VDD

Con riferimento al circuito di figura

1. verificare che M1 sia polarizzato in saturazione

2. determinare i parametri del modello di piccolo

segnale di M1 a medie-basse frequenze (gm, ro,)

3. determinare, nell’intervallo delle medie frequenze

(CAG→∞, CAS→∞), la resistenza di ingresso (RIN),

la resistenza di uscita (RO) e il guadagno di tensione

AV=vo/vi.

RIN

CAG

ID

R2

M1

R1

RI

CAS

RO

vO

RS

vI

RL

4. dimensionare le capacità CAG e CAS in modo tale che la frequenza di taglio inferiore sia

fL≈100Hz.

5. scrivere la netlist SPICE in grado di simulare il punto di lavoro, la risposta in frequenza, la

risposta al transitorio ad un ingresso sinusoidale vI(t)=1V+0.1sin(2ft) con f=10kHz e relativa

distorsione armonica.

DATI:

VDD=20V, ID=5mA, R1=4M, R2=1M, RS=2k, RI=100, RL=10k, M1:{K’N

(KP)=400A/V2,W=10m, L=11m, VTN(VTO)=1V, LAMBDA=0.01V-1}

NOTA: si dimostrino tutte le equazioni utilizzate a partire dal modello di ampio segnale del transistor

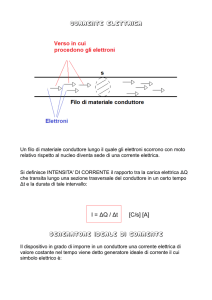

Esercizio n.2

R1

Con riferimento al circuito di figura, determinare il punto di

lavoro (corrente,tensione) dei diodi D1, D2.

D1

DATI: R1=1k, R2=500, R3=2k,V1=3V, V2=2V,

D1, D2: (VON=0.6V, RS=100)

V1

R2

V2

R3

D2

Componenti passivi ideali

R<name> <n+> <n-> <value>

C<Nome> <n+> <n-> <value> [IC=<V0>]

L<Nome> <n+> <n-> <value> [IC=<I0>]

Parametri Sintassi: .PARAM <name> <var> | <expression>

Esempi:

.PARAM R1val=1M

.PARAM R2val= {10*R1val }

R2 2 0 {R2val}

Generatori indipendenti

V<name> <(+) node> <(-) node> [ [DC] <value> ] [ AC <magnitude value> [phase value] ]

+ [STIMULUS=<stimulus name>] [transient specification]

Stimoli transitori

PULSE (<V1> <V2> <Td> <Tr> <Tf> <PW> <PER>)

SIN (<Voffset> <Vamp> <FREQ> <Td> <DF> <FASE>)

PWL (t0,V0) (t1,V1) (t2,V2) … (tn,Vn)

Diodi

D<name> <N+> <N-> <MNAME> [AREA]

. MODEL <MNAME> D [IS=<val>] [RS=<val>] [BV=<val>] [IBV=<val>] [N=<val>] ……..

BJT

Q<name> < collector node> <base node> <emitter node> [substrate node] <model name> [area]

.MODEL <model name> NPN [model parameters]

.MODEL <model name> PNP [model parameters]

MOSFET

M<name> <drain node> <gate node> <source node> <bulk/substrate node> <model name>

+ [L=<value>] [W=<value>] [AD=<value>] [AS=<value>] [PD=<value>] [PS=<value>]

+ [NRD=<value>] [NRS=<value>] [NRG=<value>] [NRB=<value>] [M=<value>] [N=<value>]

.MODEL <model name> NMOS [model parameters]

.MODEL <model name> PMOS [model parameters]

JFET

J<name> <ND> <NG> <NS> <model name> [area value]

.MODEL <model name> NJF [model parameters]

.MODEL <model name> PJF [model parameters]

Comandi di simulazione

.OP

.DC [<sweep type>] <sweep variable> <start val> <end val > <step val> [nested sweep]

Esempi:

.DC LIN I2 5mA 12mA 0.1mA

.DC PARAM RLval 50 1000 10

.DC TEMP LIST 0 20 27 50 80 100

DC LIN VIN -0.5 0.5 0.1mV TEMP LIST 300 325 350

.TRAN <T step> <T stop> [<T start> [<T max>]]

Esempi: .TRAN 0.01m 2m

.AC <sweep type> <points value> <start frequency> <end frequency >

Esempi:

.AC LIN 101 100Hz 200kHz

.AC OCT 10 1kHz 16kHz

.AC DEC 20 1MEG 100MEG

.STEP <sweep type> <sweep variable name> <start value><end value> <increment value>

Esempi:

.STEP LIN I2 5mA -2mA 0.1mA

.STEP TEMP LIST 0 20 27 50 80 100

.STEP PARAM Rval LIST 1e3 2e3 5e3

.STEP PARAM CenterFreq 9.5kHz 10.5kHz 50Hz

.FOUR <fundamental freq.> <var1> <var2> …. Es: .FOUR 1kHz V(5),V(6)

Comandi di output

.PRINT <analysis type> [<var1> <var2> …..]

.PROBE [<var1> <var2> …..]

Esempi: .PROBE V(3) V(2,3) V(R1) I(VIN) I(R2) ID(M1) IC(Q1)

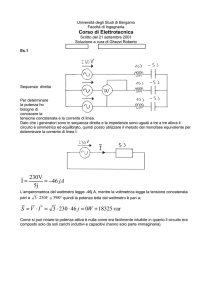

Soluzione p.1.1

VDD

In DC le capacità sono circuiti aperti e la rete si riduce come in figura.

Poichè è già nota la corrente ID, la tensione VDS può essere calcolata

dall’equazione alla maglia di uscita:

R2

D

VDS VDD I D RS 10 V

G

La tensione VGS può essere calcolata dall’equazione alla maglia di

ingresso:

VGS VG V S V DD

R1

M1

ID

S

RS

R1

I D RS 6V

R1 R2

Il punto di lavoro completo risulta

ID

I D 5mA

VGS 6 V

V 10 V

DS

Poichè risulta VDS=10V ≥ VGS-VTN=5V≥0, M1 si trova effettivamente in saturazione.

Soluzione p.1.2

G

Il modello di piccolo segnale a medie-basse

frequenze completo è riportato in figura. I

parametri del modello sono funzione del punto di

lavoro trovato al punto precedente; poichè M1 è

polarizzato in saturazione il modello di ampio

segnale a medie-basse frequenze è

iD

KN

vGS VTN 2 1 v DS

2

K N K N' W / L 363 .6 μA/V 2

I parametri del modello sono

gm

i D

vGS

i

ro D

v DS

2 K N I D 1 VDS 2mA/V

Q po int

1

1 VDS 22kΩ

I D

Q po int

D

gmvgs

S

ro

Soluzione p.1.3

A medie frequenze le capacità CAG, CAS possono essere considerate corto-circuiti. Il modello di

piccolo segnale della rete è riportato in figura a sinistra (RG=R1//R2=800k).

Il circuito può essere semplificato (figura a destra) osservando che ro si trova sempre in parallelo a

RS.

Per il calcolo della resistenza di ingresso colleghiamo un generatore di prova vx ai terminali di

ingresso (circuito a sinistra) e calcoliamo il rapporto tra vx e la corrente ix che il generatore deve

erogare

RIN

G

D

gmvgs

RG

ix

S

oib

RO

vo

vx

RS //ro

RL

R IN

vx

RG 800 kΩ

ix

Per il calcolo della resistenza di uscita passiviamo l’ingresso (vi=0) e colleghiamo un generatore di

prova vx ai terminali di uscita (circuito a sinistra)

G

D

gmvs

RI

R*

RG

S

S

D

ix

vx

ix

vx

RS //ro

gmvs

Osserviamo che, poichè vg=0, il generatore gmvgs eroga verso il Drain gmvs.

RO

vx

R S // ro // R *

ix

Per il calcolo di R* colleghiamo il generatore di prova vx direttamente al terminale di Source come

in figura a destra

i x g m vs g m v x R *

RO R S // ro //

vx

1

ix g m

1

393

gm

Per il calcolo del guadagno AV facciamo nuovamente riferimento al circuito di piccolo segnale

completo (RS,T=RS//ro//RL=1.54k)

RIN

G

D

gmvgs

RI

S

RG

vo

vi

RS,T

AV

v o v g v gs vo

vi

vi v g v gs

vg

R IN

vi R IN R I

v gs

g m RS ,T

R IN

1

AV

0.76

v g v gs v s v gs g m v gs RS ,T

v

1

g

R

R

R

1

g

R

g

m S ,T

IN

I

m S ,T

v

g v R

o m gs S ,T g m RS ,T

v gs

v gs

Soluzione p.1.4

Il modello equivalente AC della rete a medie-basse frequenze è

Il dimensionamento delle capacità deve essere fatto imponendo una frequenza di taglio inferiore

fL=100Hz. La relazione tra fL e le capacità può essere ottenuto in modo approssimato utilizzando il

metodo delle costanti di tempo in corto-circuito

fL

1

2

1

1

RCAG C AG RCAS C AS

dove RCAG, RCAS sono le resistenze viste da CAG, e CAS rispettivamente.

Per il calcolo di RCAG i) assumiamo che, nella banda di interesse, la capacità CAS sia di valore

sufficientemente grande da poter essere sostituita con un corto-circuito; ii) passiviamo il generatore

di tensione indipendente vi (sostituiamolo con un corto-circuito); iii) applichiamo un generatore di

prova vx al posto di CAG. Otteniamo la rete

La resistenza vista da CAG è data dal rapporto tra vx e la corrente ix che vx stesso deve erogare

RCAG

vx

R I R IN 800 .1kΩ

ix

Per il calcolo di RCAS i) assumiamo che, nella banda di interesse, la capacità CAG sia di valore

sufficientemente grande da poter essere sostituita con un corto-circuito; ii) passiviamo il generatore

di tensione indipendente vi (sostituiamolo con un corto-circuito); iii) applichiamo un generatore di

prova vx al posto di CAS. Otteniamo la rete

La resistenza vista da CAS è data dal rapporto tra vx e la corrente ix che vx stesso deve erogare

RCAS

vx

R L RO 10 .39 kΩ

ix

Imponiamo uno dei 2 poli al valore della fL e l’altro una decade più in basso in modo che il limite di

banda inferiore sia definito da un polo dominante. Per limitare i valori della capacità scegliamo di

porre il polo relativo a CAS (resistenza vista più bassa) a fL e quello relativo a CAG una decade più in

basso

C AS

1

153nF

2f L RCAS

C AG

10

19.9nF

2f L RCAG

Soluzione p. 1.5

netlist amplificatore CD

VDD 1 0 20

R2 1 2 1e6

R1 2 0 4e6

RS 3 0 2e3

CAG 2 5 19.9n

CAS 3 4 153n

M1 1 2 3 3 mosmodel W=10u L=11u

.model mosmodel NMOS KP=400e-6

+VTO=1 LAMBDA=0.01

RI 5 6 100

RL 4 0 10e3

VI 6 0 AC 1 SIN(1 0.1 10k)

.OP

.AC DEC 100 1 1e7

.FOUR 10k V(4)

.TRAN 0.01m 0.2m

.PROBE V(4)

.END

1

VDD

R2

CAG

2

5

R1

RI

VI

6

M1

CAS

3

4

RS

RL

0

Soluzione p.2

Il generatore V1 tende a polarizzare direttamente D1, mentre V2 tende a polarizzare inversamente

D1. Non è possibile quindi a priori preferire una regione di funzionamento nella ipotesi sullo stato di

D1. Sia V1 che V2 tendono a polarizzare direttamente D2, quindi in questo caso è ragionevole partire

con l’ipotesi D2 ON.

Partiamo con l’ipotesi (D1 OFF, D2 ON) invece che (D1 ON,

D2 ON) poichè la rete da risolvere è più semplice.

Sostituiamo quindi D1 con un circuito aperto e D2 con il

modello equivalente in conduzione diretta (figura).

Per vedere se l’ipotesi è corretta, dobbiamo vedere se

VD1≤VON=0.6V e ID2≥0. Calcoliamo quindi VD1 e ID2.

I D2

ID1

R3

VD1

+

R2

+

RS

V2

V1

ID2

VD2

VON

-

V2 VON

538 .4μA 0

R2 R3 RS

V D1 V1 V2 I D 2 R2 1.27 V VON

Hp non verifi cata!

Ricominciamo quindi facendo l’ipotesi (D1 ON, D2 ON).

Sostituiamo D1 e D2 con il modello equivalente in

conduzione diretta (figura)

Per vedere se l’ipotesi è corretta, dobbiamo vedere se ID1≥0

e ID2≥0. Calcoliamo quindi ID1 e ID2. Possiamo utilizzare il

teorema di Millman per calcolare la VAB

V AB

R1

R1

A

VD1

ID1

V1 VON V AB

I

445μA 0

D

1

R

R

1

S

ipotesi verificat a

V

V

AB

ON

I

624μA 0

D 2

R3 RS

R3

R2

VON

+

V1 VON V2

VON

R RS

R2 R3 RS

1

1 .9 V

1

1

1

R1 RS R2 R3 RS

RS

V1

+

RS

V2

ID2

B

VD2

VON

-

Poichè le ipotesi su entrambi i diodi risultano verificate, lo stato dei diodi è effettivamente (D1 ON,

D2 ON) ed il loro punto di lavoro è

I D1 445μA

Q1 :

VD1 VON I D1 RS 644.5mV

I D 2 624μA

Q2 :

VD 2 VON I D 2 RS 662 .4mV