Seconda Università degli Studi di Napoli

C.d.L. in Ingegneria Elettronica

corso di Elettronica 2

aa. 2000 / 01

prof. Luigi Zeni

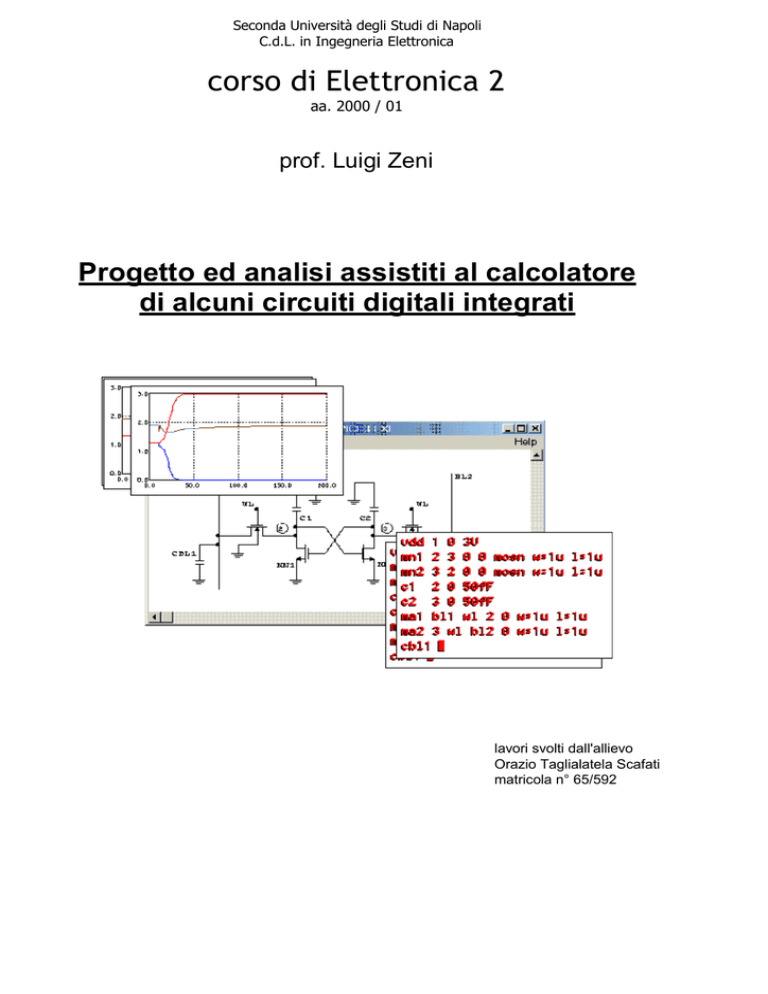

Progetto ed analisi assistiti al calcolatore

di alcuni circuiti digitali integrati

lavori svolti dall'allievo

Orazio Taglialatela Scafati

matricola n° 65/592

Nello sviluppare i lavori presenti, sono stati utilizzati i seguenti programmi per SO Microsoft© Windows:

WinSpice v1.02.03

un porting freeware dello Spice3F4 dell'Università di Berkeley

compatibile con PSpice e senza limitazioni.

http://www.willingham2.freeserve.co.uk/winspice.html

Atlantis Ocean Mind v1.0

un word processor con funzioni di spell checking

con cui sono stati scritti e corretti i testi dei lavori

http://www.rssol.com/en/

EditPlus 2 v.210c

un potente editor testuale con cui sono

state scritte le netlist Spice

http://www.editplus.com/

Ultimate Paint v1.91f

un editor grafico con cui sono stati ritoccati ed aggiunti

commenti ai plot prodotti da WinSpice.

http://www.ultimatepaint.com

FidoCAD v0.96

un semplice ma efficace programma di CAD con

cui sono stati disegnati gli schemi circuitali.

http://antani.virtualave.net/fidocad.html

Indice

Analisi di un invertitore NMOS con carico a svuotamento.....................................pag. 6

Descrizione del circuito

" 6

Analisi statica

Caratteristica di trasferimento:

Potenza statica dissipata in funzione della tensione di ingresso:

" 7

" 7

" 8

Analisi dinamica

Ritardo nella transizione alto->basso in uscita

Ritardo nella transizione basso->alto in uscita

Valutazione della potenza dissipata media

"

"

"

"

Analisi dinamica con effetto di substrato non nullo:

" 14

9

10

11

13

Analisi di un invertitore CMOS e applicazione al progetto di una rete

complessa...................................................................................................................................pag. 15

Descrizione del circuito

" 15

Analisi statica

Caratteristica di trasferimento per l'invertitore CMOS simmetrico

Potenza statica dissipata

" 16

" 16

" 17

Analisi dinamica

Valutazione dei tempi di propagazione

Valutazione della potenza dinamica media dissipata dall'invertitore

" 18

" 19

" 20

Analisi dell'invertitore CMOS con area minima

" 21

Applicazione al progetto di una rete complessa

Dimensionamento dei transistori

Analisi dinamica

Analisi con effetto di substrato non nullo

Progetto ad area minima

"

"

"

"

"

23

24

25

27

27

Progetto di un flip-flop RS in tecnologia CMOS........................................................pag. 29

Cenni di teoria e progetto circuitale

" 29

Analisi dinamica

Valutazione dei tempi di commutazione

Considerazioni sulla potenza media dissipata:

" 31

" 32

" 33

Analisi di un invertitore ECL.............................................................................................pag. 34

Descrizione del circuito

" 34

Analisi statica

Caratteristiche di trasferimento a T= 27°C

Analisi con una batteria per la generazione della tensione di riferimento

Potenza statica dissipata al variare della tensione di ingresso

Caratteristiche di trasferimento a T= 47°C

Analisi con una batteria per la generazione della tensione di riferimento

Potenza statica dissipata

"

"

"

"

"

"

"

36

36

37

38

39

41

42

Analisi dinamica

Valori teorici

Risultati della elaborazione numerica

Singolo stadio non caricato

Singolo stadio con capacità di carico

Doppio stadio

"

"

"

"

"

"

43

43

44

44

46

48

Analisi di un invertitore TTL.............................................................................................pag. 50

Descrizione del circuito

" 50

Analisi statica

Caratteristica di trasferimento e considerazioni sulle regioni di funzionamento dei ...

Potenza statica dissipata

Caratteristica di ingresso

Caratteristiche di uscita e fan-out della porta

Stato di ingresso basso

Stato di ingresso alto

"

"

"

"

"

"

50

53

54

55

55

56

Analisi dinamica

Previsioni teoriche

Risultati dell'elaborazione numerica

Elaborazione con differenti tempi di transito

"

"

"

"

58

58

59

60

Progetto e confronto di alcuni tipi di celle di memoria RAM in tecnologia

CMOS..........................................................................................................................................pag.61

Descrizione dei vari tipi di cella elementare e dell'amplificatore di lettura

sense amplifier

cella 6T (memoria statica):

cella 1T (memoria dinamica)

cella 4T (memoria dinamica)

"

"

"

"

"

61

61

62

63

64

Operazione di lettura

Fase di precarica e punto di lavoro iniziale

Fase di accesso alla cella (sensing)

Accesso alla cella 6T

Accesso alla cella 1T

Accesso alla cella 4T

Confronto tra i vari tipi di celle

"

"

"

"

"

"

"

65

65

68

68

69

69

70

Operazione di scrittura

Scrittura nella cella 6T

Scrittura nella cella 1T

" 71

" 71

" 72

Valutazione della potenza dissipata dalle varie celle

Accesso in lettura alla cella 6T

Accesso in scrittura alla cella 6T

Accesso in lettura alla cella 1T

Accesso in scrittura alla cella 1T

"

"

"

"

"

73

73

74

75

75

Analisi di un invertitore NMOS

con carico a svuotamento

di Orazio Taglialatela Scafati

matricola n° 65/592

Descrizione del circuito

Lo schema circuitale cui si farà riferimento in questa prima sezione è quello relativo all'invertitore

NMOS con carico a svuotamento considerato in condizioni stazionarie (vale a dire senza alcun carico

connesso al nodo "out"):

L'associata netlist spice è la seguente, dove si è indicato con il simbolo "1" il nodo di

alimentazione:

*** descrizione del circuito

Vdd 1 0

5V

Vin

in

0

Mload 1

out out 0

NMOS1

Minv out in

0

0

NMOS2

L=2.15u

L=1u

W=1u

W=2.06u

*** analisi dc tra 0V e 5V

.dc

Vin 0 5 .05

*** descrizione dei modelli

.model NMOS1 NMOS(level=1, lambda=.02, vto=-3, kp=25e-6, cgso=200e-12

+ cgdo= 200e-12, cgbo=200e-12)

.model NMOS2 NMOS(level=1, lambda=.02, vto=1, kp=25e-6, cgso=200e-12

+ cgdo= 200e-12, cgbo=200e-12)

.end

Per ora si trascura l'effetto di substrato del transistore di carico (gamma= 0.0 per default).

Analisi statica

- Caratteristica di trasferimento:

out = .286V @ Vin= 5.0V

deriv(out) = -1.05 @ Vin=1.6V

deriv(out) = -0.956 @ Vin= 2.7V

In base ai risultati ottenuti è ragionevole assumere per questo invertitore i seguenti livelli logici ed

i relativi margini di rumore:

Vol= 0.29V

Voh= 5V

Vil= 1.6V

Vih= 2.7V

NMl= 1.31V NMh= 2.3V

laddove i calcoli manuali davano:

Vol= 0.25V

Voh= 5V

Vil= 1.46V

Vih= 2.53V

NMl= 1.20V NMh= 2.39V

- Potenza statica dissipata in funzione della tensione di ingresso:

potenza dissipata nello stato alto in uscita: Pdiss= 0 mW @ Vin= 0.29V

potenza dissipata nello stato basso in uscita: Pdiss = Vdd * Id = 0.286 mW @ Vin= 5.0V

Ovviamente la potenza statica dissipata nello stato logico alto in uscita è nulla, poiché il

transistore di switch è spento a tale valore di tensione in ingresso. Viceversa nello stato logico basso in

uscita si ha una dissipazione di ca. 0.29 mW.

Il tratto quasi orizzontale della curva è relativa alla saturazione del MOSFET di carico, e la lieve

pendenza è dovuta all'effetto di modulazione del canale. Senza tale effetto si avrebbe

Pdiss= 0.26 mW @ Vin= 5.0V

Analisi dinamica

Si farà riferimento al seguente schema circuitale, con un secondo stadio posto in cascata

all'invertitore già studiato:

La netlist associata è

invertitore NMOS con carico a svuotamento - doppio stadio

*** descrizione del circuito

Vdd

1

0

5V

Vin

in

0

pulse(0.29V, 5V, 10n, .1n, .1n, 20n, 40n)

***** primo stadio

Mload1

1

2

Minv1 2

in

0

2

0

0

NMOS2

NMOS1

L=1u

L=2.15u W=1u

W=2.06u

***** secondo stadio

Mload2

1

out out 0

Minv2 out 2

0

0

NMOS2

NMOS1

L=1u

L=2.15u W=1u

W=2.06u

*** analisi dinamica

.tran .01n 50n 0.001n

*** descrizione dei modelli

.model NMOS1 NMOS(level=1, lambda=.02, vto=-3, kp=25e-6, cgso=200e-12

+ cgdo= 200e-12, cgbo=200e-12)

.model NMOS2 NMOS(level=1, lambda=.02, vto=1, kp=25e-6, cgso=200e-12

+ cgdo= 200e-12, cgbo=200e-12)

.end

Per lo studio del comportamento dinamico di questo oggetto, si limiterà l'analisi ad un impulso in

ingresso di ampiezza pari a 20ns:

- ritardo nella transizione alto->basso in uscita

facendo riferimento al fronte di salita della Vin abbiamo il seguente diagramma temporale:

ritardo nella transizione alto->basso: 0.036ns

- ritardo nella transizione basso->alto in uscita:

ritardo nella transizione basso->alto: 0.12ns

Si può notare come la transizione alto->basso in uscita avvenga ca. 3.33 volte più velocemente

della transizione basso->alto. Questo è dovuto alle correnti più forti che attraversano la gate del

transistore Minv2 durante la fase di salita del segnale in ingresso.

Questo effetto può essere amplificato sostituendo il secondo stadio con una capacità di valore

abbastanza elevato, ad esempio di 0.1pF:

invertitore NMOS con carico a svuotamento - doppio stadio

*** descrizione del circuito

Vdd

1

0

5V

Vin

in

0

pulse(0.29V, 5V, 10n, .1n, .1n, 20n, 40n)

***** primo stadio

Mload1

1

2

Minv1 2

in

0

2

0

***** secondo stadio

C1

2

0

0.1pF

*** analisi dinamica

.tran .01n 50n 0.001n

0

NMOS2

NMOS1

L=1u

L=2.15u W=1u

W=2.06u

In questo caso, come si nota dal diagramma temporale riportato, i ritardi in entrambe le transizioni

sono notevolmente degradati, fermo restando la maggiore rapidità nella prima commutazione:

In particolare, si trovano per questo invertitore i seguenti valori:

Thl = 0.68 ns

Tlh = 4.4 ns

in questo caso la transizione di salita è ca. 6.5 volte più lenta di quella di discesa.

E' da notare come i risultati manuali davano i seguenti valori:

Thl = 0.45 ns

Tlh = 4.6 ns

Nel caso della commutazione in discesa si constata un errore percentuale di circa il 30%. Si è

imputato questo errore al fatto di aver trascurato nei calcoli manuali la corrente che attraversa il

transistore Mload durante la fase di scarica del condensatore. Questa corrente infatti provoca un

leggero aumento del ritardo nella commutazione alto->basso, come l'elaborazione numerica ha

manifestato. Essendo comunque il ritardo in gioco in questa commutazione molto più piccolo di quello

relativo alla commutazione in salita, è ragionevole trascurare questo aspetto.

- Valutazione della potenza dissipata media

L'espressione della potenza media totale dissipata da una porta NMOS operante a frequenza f con

un duty cycle del 50% è la seguente:

PDISS = <PS> + <PD> = <PS> + f C VDD2

A causa del termine di potenza statica, questa non dipende proporzionalmente dalla frequenza. Se

però quest'ultima diviene sufficientemente elevata può essere lecito trascurare il primo termine della

somma rispetto al secondo, in modo che valga la diretta proporzionalità.

Il termine di potenza statica media teorico per un duty cycle del 50% è dato da

<PS> = 1/2 VDD IDL = ( .29 / 2) mW = 0.145 mW

mentre quello per la potenza dinamica è dato da

< PD > = f C VDD2 = 25 ∗ 10-14 ∗ f

dove si è supposto una capacità di carico di 0.01pF. Il valore teorico di frequenza per cui tali contributi

si equivalgono è dato da

f= 580 MHz

Questo valore di frequenza è troppo alto per permettere un adeguato assestamento dei livelli logici

in uscita all'invertitore, per cui alle frequenze di utilizzo il solo contributo importante alla potenza

media dissipata è il termine statico.

Per analizzare numericamente questo aspetto, si è posto in ingresso alla porta un generatore di

onda quadra con duty cycle del 50%, operante a differenti frequenze, ed estendendo opportunamente il

tempo finale di calcolo:

Vin

in

0

pulse(0.29V, 5V, 0, .01n, .01n, 1/(2f), 1/f )

* con f freq di funzionamento e 1/(2f) ampiezza dell'impulso (duty cycle = 50%)

Andando a calcolare la <PDISS> mediante il comando print -mean(v(1)*vdd#branch) si

ottengono i seguenti risultati (i pedici "num" sono ad indicare il risultato di un'elaborazione numerica):

a f = 0.5 MHz: <PDISS>num = 0.140 mW

f C VDD2 = 0.125 µW -> <PS>num =<PDISS>num - f C VDD2 = .140 mW

a f = 1 MHz: <PDISS>num = 0.137 mW

f C VDD2 = 0.25 µW -> <PS>num = .137 mW

a f = 25 MHz: <PDISS>num = 0.142 mW

f C VDD2 = 6.25 µW -> <PS>num == .136 mW

Si nota come numericamente il termine in potenza statica abbia una dipendenza dalla frequenza di

utilizzo quasi nulla, come era lecito aspettarsi.

I risultati dell'elaborazione numerica sono in soddisfacente accordo con quelli teorica, ma l'errore

cresce all'aumentare della frequenza. Ciò è dovuto all'approssimazione di ritenere nel calcolo manuale

della potenza statica dissipata livelli logici perfettamente assestati sui valori 0.29V e 5V e tempi di

commutazione nulli, trascurando così i processi di carica e scarica della capacità. Nei circuiti reali,

invece, all'aumentare della frequenza questi ultimi diventano sempre più marcati, dando luogo a

discrepanze sempre più grandi con i risultati teorici.

Analisi dinamica con effetto di substrato non nullo:

Finora si è trascurato l'effetto di substrato che caratterizza il transistore di carico, inevitabilmente

presente qualora si realizzi la porta in tecnologia integrata. Per prevedere questo aspetto, nella netlist

spice è necessario modificare il modello del transistore Mload includendo un parametro γ non nullo

(per default è 2Φ = 0.6 ):

.model NMOS1 NMOS(level=1, lambda=.02, vto=-3, gamma=0.5, kp=25e-6, cgso=200e-12

+ cgdo= 200e-12, cgbo=200e-12)

Ponendo di nuovo una capacità di carico di 0.1pF, si ottengono i seguenti valori per i ritardi in

entrambe le transizioni:

Thl= 0.68 ns

Tlh= 5.5 ns

E' interessante notare come per la scarica del condensatore il ritardo sia pressoché rimasto

invariato, come era infatti prevedibile dato che il transistore di carico gioca un ruolo trascurabile in

questa transizione. Viceversa l'effetto di substrato pesa qualora si consideri la fase di carica del

condensatore, essendo qui il solo transistore Minv a fornire la corrente necessaria alla commutazione,

che risulta però ridotta rispetto al caso di assenza di effetto bulk durante tutto il processo.

Dal seguente diagramma temporale in cui sono stati sovrapposti i risultati delle due elaborazioni

eseguite con e senza effetto di body, si può notare come la fase di discesa è sostanzialmente invariata

mentre quella di salita è leggermente rallentata dalla presenza di un γ non nullo:

Analisi di un invertitore CMOS e applicazione al

progetto di una rete complessa

di Orazio Taglialatela Scafati

matricola n° 65/592

Descrizione del circuito

Il circuito invertitore in tecnologia CMOS che si analizzerà è il seguente, considerato in

condizioni stazionarie:

L'associata net list Spice è la seguente:

Vdd

Vin

MP out

MN out

1

in

in

in

**analisi dc

.dc

Vin

0

0

1

0

5V

1

0

PMOS1 W=5u

NMOS1 W=2u

0

5

0.01

L=1u

L=1u

**descrizione dei modelli

.model

NMOS1 NMOS(level=1, lambda=.02, vto=1, kp=25e-6, cgso=200e-12

+ cgdo=200e-12, cgbo=80e-12)

.model

PMOS1 PMOS(level=1, lambda=.02, vto=-1, kp=25e-6, cgso=200e-12

+ cgdo=200e-12, cgbo=80e-12)

Il transistore a canale p è caratterizzato da un parametro Kp' circa il 2.5 volte più piccolo del

corrispondente Kn' per quello a canale n. Per avere un invertitore simmetrico (con KR= K n/Kp=1) si è

fissato un rapporto d'aspetto W/L per il PMOS 2.5 volte più grande di quello relativo al NMOS.

Questa struttura non risente di effetto di substrato, essendo qui possibile connettere i source di

entrambi i transistori ai propri morsetti di body.

Analisi statica

- Caratteristica di trasferimento per l'invertitore CMOS simmetrico:

si sono messe in evidenza le diverse regioni di funzionamento del circuito:

1. per Vin < VTN = 1V, il transistore NMOS è spento

2. per Vin > VTN e Vout > Vin + | VTP |= Vin + 1V, l'NMOS è in saturazione e il PMOS è in triodo

3. per Vin - VTN = Vin - 1V < Vout < Vin + | VTP | = Vin + 1V, entrambi i MOS sono in saturazione

4. per Vout < Vin - VTN = Vin - 1V, l'NMOS è in triodo e il PMOS in saturazione

5. per Vin > VDD + VTP = VDD - 1V, il transistore PMOS è spento

Dall'analisi della caratteristica di trasferimento è immediato stabilire i seguenti valori per i livelli

logici:

VOL= 0 V

VOH= 5 V

in modo da poter sfruttare per questa porta la massima separazione tra i valori di tensione

permessa dall'alimentazione. Analizzando il vettore deriv(out), è immediato trovare i seguenti valori

per VIL e VIH, ed i corrispondenti margini di rumore:

VIL= 2.09 V VIH= 2.91 V

NML = NMH= 2.09 V

Questo risultato è praticamente coincidente con i quello dei calcoli manuali. Si noti che la curva di

trasferimento è perfettamente simmetrica rispetto alla bisettrice Vout = Vin (in virtù del fatto che KR =

Kn/Kp = 1), e di conseguenza i margini di rumore sono uguali tra loro e pari a circa VDD/2.

- Potenza statica dissipata:

Dal seguente grafico della corrente erogata dall'alimentazione in funzione della tensione

d'ingresso è possibile constatare come questa in condizioni statiche (quando l'ingresso VIN è stabile su

0V o su 5V) sia nulla, dal momento che uno dei due transistori è spento. Di conseguenza la potenza

dissipata in condizioni statiche è nulla.

Nel range di valori di ingresso 1.0V < VIN < 4.0V, invece, entrambi i transistori conducono, ed

una corrente non nulla riesce a chiudersi da alimentazione a massa, la quale ha un valore massimo in

VIN = VDD/2 = 2.5V, pari a circa 60 µA, come di può notare dal seguente diagramma:

E' da sottolineare che questo grafico è derivato da un'analisi in continua; pertanto in condizioni

dinamiche, a seguito di una variazione di VIN da un livello all'altro, questa corrente di "corto circuito"

in generale assumerà valori di picco inferiori a 60 µA, come si può constatare nella seguente sezione.

In effetti, questo diagramma mostra punto per punto i valori massimi della corrente di corto

circuito, raggiungibili in condizioni stazionarie o quasi-stazionarie (cioè quando l'ingresso varia così

lentamente da far praticamente assestare punto per punto l'uscita al valore statico dato dalla

caratteristica di trasferimento).

La corrente di corto circuito è responsabile di un contributo alla potenza dinamica dissipata

qualora l'ingresso vari gradualmente tra i due livelli logici. Come si vedrà nella successiva sezione,

questo può essere dell'ordine del 20-30% della potenza dissipata nei processi di carica/scarica della

capacità di carico.

Analisi dinamica

Nello studio dell'invertitore CMOS considerato in condizioni dinamiche, vi si applicherà come

carico un secondo invertitore caratterizzato dagli stessi parametri del primo:

e la netlist sarà modificata come segue:

invertitore CMOS

**descrizione del circuito

Vdd

Vin

1

in

0

0

5V

pulse(0V, 5V, 10n, .1n, .1n, 20n, 40n)

*****primo stadio

MP1

2

in

MN1

2

in

1

0

1

0

PMOS1 W=5u

NMOS1 W=2u

L=1u

L=1u

****secondo stadio

MP2

out

2

MN2

out

2

1

0

1

0

PMOS1 W=5u

NMOS1 W=2u

L=1u

L=1u

**analisi in transitorio

.tran

.01n 50n

0

.01n

L'analisi è estesa in modo da includere un impulso di ampiezza 20ns nel segnale in ingresso,

sufficiente a far assestare l'uscita su entrambi i livelli logici.

- valutazione dei tempi di propagazione:

Dai seguenti diagrammi si evince come per l'invertitore simmetrico i transitori di salita e discesa

abbiano andamenti analoghi, dando luogo a tempi di propagazione pressoché coincidenti, pari a circa

0.06ns:

ritardo di propagazione = THL = TLH = 0.06ns

Per poter confrontare i risultati della elaborazione numerica con quelli manuali, si è sostituito il

secondo stadio con una capacità equivalente di 0.1pF:

**** secondo stadio

C1 out

0

.1pF

Per questo invertitore il tempo di propagazione è Tnum = TLH = THL = 0.70ns, mentre l'analisi

teorica fornisce un valore di

T = .325 C / Kn = .65ns

in soddisfacente accordo con i risultati forniti dal calcolatore.

- valutazione della potenza dinamica media dissipata dall'invertitore:

A tal fine si solleciterà il circuito con un'onda quadra oscillante tra i livelli 0V e 5V a differenti

frequenze:

Vin

in

0

pulse( 0V

5V

** con f frequenza di funzionamento

0

5n

5n

1/(2f)

1/f )

e si calcolerà la potenza dissipata media attraverso il comando print -mean(v(1) *

vdd#branch) (si ricorda che nel Berkeley Spice, la funzione mean() calcola la media dell'intero

contenuto del vettore argomento; il vettore vdd#branch è quello delle correnti entranti nel ramo di

alimentazione).

Si ricorda che la potenza media dissipata nei processi di carica/scarica della capacità di carico è

data dalla formula

PD' = f C V DD2

e dipende quindi linearmente dalla frequenza di lavoro.

Associata a questa vi è la potenza P D'' dissipata a causa della cosiddetta "corrente di corto

circuito", vale a dire la corrente che si chiude da alimentazione a massa quando i transistori sono

entrambi in conduzione a causa della transizione graduale della tensione in ingresso. Per poter

visualizzare questo effetto, si sono fissati i tempi di salita e discesa del segnale in ingresso a 5ns.

Nel seguente diagramma temporale si è riportata la corrente fornita dall'alimentazione, e si può

notare come accanto a dei forti impulsi di corrente necessari a caricare la capacità vi siano dei piccoli

spikes che rappresentano la corrente di corto circuito:

Di seguito sono riportati i risultati delle elaborazioni eseguite a varie frequenze e i relativi valori

deiprodotti ritardo-potenza calcolati come PDP = <PDISS> ∗ T, con T = 0.7ns:

a f = 1MHz → <PDISS>num = 3.2 µW, PDP = 2.24 fJ

PD' = f C VDD2 = 2.5 µW → PD'' = .7 µW (28% della PD')

a f = 5MHz → <PDISS>num = 16.0 µW, PDP = 11.2 fJ

PD' = f C VDD2 = 12.5 µW → PD'' = 3.5 µW (28% della PD')

a f = 10MHz → <PDISS>num = 31.7 µW, PDP = 22.2 fJ

PD' = f C VDD2 = 25 µW → PD'' = 6.7 µW (26.8% della PD')

(la teoria prevede un upper bound per il prodotto ritardo-potenza di C V DD2 / 5 = 500 fJ)

Si nota come la potenza dissipata per effetto della corrente di corto circuito si mantenga intorno al

26-28% della potenza dissipata per effetto della carica/scarica della capacità.

Analisi dell'invertitore CMOS con area minima

Volendo seguire ora un progetto ad area minima si possono stabilire degli uguali rapporti d'aspetto

per i due transistori. In questo modo la simmetria del circuito risulterà sbilanciata poiché il MOSFET a

canale n sarà caratterizzato da un parametro KN > KP e quindi avrà una maggiore capacità di assorbire

corrente rispetto a quello a canale p.

Fissando i rapporti d'aspetto (W/L)N = (W/L)P = 2/1, si ottiene la seguente curva di trasferimento:

La caratteristica risulta spostata verso sinistra, ed in particolare assume il valore VDD/2 per V IN =

2.16V. Questo è dovuto al fatto che l'NMOS riesce ad assorbire la stessa corrente del PMOS con un

valore più basso di tensione ai capi.

Andando a valutare i tempi di risposta della porta caricata con una capacità di 0.1pF, si nota come

il transitorio di discesa risulti leggermente più rapido rispetto a quello di salita:

In particolare si trovano i seguenti valori per THL e TLH:

THL = 0.69 ns

TLH = 1.71 ns

dando luogo ad un rapporto THL / TLH = 0.403, in ottimo accordo con i risultati teorici, che stabiliscono

un valore di

THL / T LH = KP / KN = ( (W/L) P / (W/L)N ) / 2.5 = 1 / 2.5 = 0.400

dove si è posto KN' / KP' = 2.5.

Applicazione al progetto di una rete complessa

Come applicazione dei risultati ottenuti finora, si è sviluppato il progetto di una rete in tecnologia

CMOS, implementante una funzione booleana di 5 variabili:

~Y = A ( B + C D ) + E

( dove il simbolo ~ rappresenta l'operatore booleano NOT )

applicando le regole di De Morgan, si trova l'espressione della Y in funzione dei complementi

delle variabili di ingresso:

Y= ( ~A + ~B ( ~C + ~D ) ) ~E

La prima espressione fornisce immediatamente la struttura topologica della rete di pull-down,

mentre la seconda quella della rete di pull-up. In definitiva la struttura circuitale è la seguente, avendo

numerato i nodi interni da 1 a 6 ( 1 = alimentazione, 4 = uscita):

- dimensionamento dei transistori:

Per ottenere gli stessi tempi di risposta dell'invertitore fondamentale studiato precedentemente,

qualora questa struttura venga caricata da una capacità di 0.1pF, è necessario dimensionare

opportunamente i transistori in maniera che i processi di carica/scarica della capacità di carico

avvengano con livelli di corrente comparabili ai precedenti.

1. Per la rete di pull-down abbiamo che il percorso costituito dal maggior numero di transistori

accesi è quello relativo alla configurazione di ingressi ABCDE = 10110, in modo che i transistori A,

C, D si troveranno ad essere in serie. Se fissiamo per questi lo stesso rapporto d'aspetto W/L, allora la

tensione ai capi di ognuno sarà all'incirca 1/3 della tensione di uscita vY per la maggior parte del tempo

della fase di scarica (quando i 3 transistori opereranno in regione di triodo), per cui è necessario al fine

di assicurare gli stessi livelli di corrente di scarica dell'invertitore fondamentale, fissare un W/L pari a

3 volte quello del transistore di pull-down di quest'ultimo:

(W/L)NA = (W/L)NC = (W/L)ND = 3 (2/1) = 6/1

E' da sottolineare l'approssimazione di aver considerato per tutti e tre i transistori delle tensioni

vGS = 5V, come per il MOSFET-N dell'invertitore fondamentale. In realtà, i transistori A e C sono

caratterizzati da tensioni vGS < 5 V; in particolare è

vGS,A = 5V - vDS,D - v DS,C

vGS,C = 5V - vDS,D

A rigore, quindi, bisognerebbe scegliere per A e C dei rapporti d'aspetto leggermente più grandi in

modo da compensare la ridotta capacità di questi di condurre corrente. Trattandosi di una fase di

scarica, comunque, è lecito supporre che per la maggior parte del tempo la tensione vY sia

sufficientemente piccola da rendere trascurabile questo aspetto.

Il percorso A-B invece è costituito da soli due transistori, di cui abbiamo già il rapporto di aspetto

del primo. Per il transistore B basterà allora assicurare (approssimando come già fatto prima la vGS,A a

5V durante tutta la scarica) che

1/(W/L)NA + 1/(W/L)NB = 1/(W/L)Nfond

dove (W/L)fond è il rapporto d'aspetto del NMOS relativo all'invertitore fondamentale: (W/L)Nfond =

2/1. Si ottiene quindi

(W/L)NB = 3/1

Per il transistore E basterà porre

(W/L) NE = (W/L) Nfond =2/1

poiché la scarica nella configurazione ABCDE = 00001 avviene con le stesse modalità dell'invertitore

fondamentale.

Per le restanti configurazioni di ingressi la scarica avverrà più velocemente di quella

dell'invertitore fondamentale poiché si avranno gruppi di transistori in parallelo, e la corrente di

scarica risulterà più alta a parità di tensione in uscita.

2. Dimensioniamo ora lo stadio di pull-up allo stesso modo:

(W/L)PE = (W/L)PB = (W/L)PC = (W/L)PD = 3 (W/L) Pfond = 3 (5/1) = 15/1

1/(W/L)PA + 1/(W/L)PE = 1/(W/L)Pfond = 1/5 → (W/L)PA = 7.5/1

- analisi dinamica:

Usando gli stessi modelli per i transistori NMOS e PMOS usati per l'invertitore fondamentale, si

ottiene la seguente netlist spice, dove si è fissata la configurazione di ingressi ABCE = 1010, e

sollecitando l'ingresso D con un'onda quadra (questa configurazione di ingressi rappresenta il caso

peggiore per il circuito poiché ad ogni transizione si troveranno ad essere tre transistori in serie sia

nella rete di PMOS che in quella di NMOS) e ponendo una capacità di carico di 0.1pF:

Vdd

1

0

****** rete di pull-up

MPA

2

MPB

2

MPC

3

MPD

3

MPE

1

****** rete di pull-down

MNA

4

MNB

5

MNC

5

MND

6

MNE

4

** segnali di ingresso

VA

A

0

VB

B

0

VC

C

0

VD

D

0

VE

E

0

5V

A

B

C

D

E

4

3

4

4

2

1

1

1

1

1

PMOS1

PMOS1

PMOS1

PMOS1

PMOS1

W=7.5u

W=15u

W=15u

W=15u

W=15u

L=1u

L=1u

L=1u

L=1u

L=1u

A

B

C

D

E

5

0

6

0

0

0

0

0

0

0

NMOS1

NMOS1

NMOS1

NMOS1

NMOS1

W=6u

W=3u

W=6u

W=6u

W=2u

L=1u

L=1u

L=1u

L=1u

L=1u

5V

0V

5V

pulse(0 5 10n .1n .1n 10n 20n)

0V

I modelli utilizzati sono gli stessi usati per lo studio dell'invertitore fondamentale. E' da notare

come in questa rete, a differenza di quanto accadeva per l'invertitore, i transistori MPA, MPB, MPC,

MPD e MNA, MNC soffrano di effetto di substrato non nullo. Questo causa un degrado delle

prestazioni del circuito in termini di tempi di risposta. Questo aspetto verrà analizzato in seguito.

Ecco i risultati dell'elaborazione avendo sollecitato l'ingresso D con un'onda quadra:

Si ottengono i seguenti tempi di commutazione nella configurazione ABCDE = 101x0 (con "x"

segnale variabile):

THL 101x0 = 0.82ns

TLH 101x0 = 0.93ns

E' da notare come questi siano quasi coincidenti tra loro ed entrambi prossimi al ritardo

dell'invertitore elementare, Tfond = 0.7ns. Le sottili discrepanze, comunque, sono dovute alle

approssimazioni di ritenere transistori sempre operanti in regione lineare e con vGS = 5V. Ecco infatti

come varia nel tempo la tensione vGS ad esempio del transistore MNA durante la fase di accensione,

cioè durante la scarica della capacità (da 10 a 20ns):

Inoltre anche lo spegnimento è graduale, e ciò implica che una certa corrente attraversa il

transistore anche quando questo dovrebbe essere spento. In condizioni di non conduzione, la vGS del

transistore MNA si assesterà sul valore V TN = 1V, al limite di accensione.

- analisi con effetto di substrato non nullo:

In questa struttura i transistori MPA, MPB, MPC, MPD e MNA, MNC risentono di effetto di

substrato che degrada le prestazioni del circuito in termini di tempi di risposta. In particolare, ponendo

un parametro gamma= 0.5 per entrambi i tipi di transistori, si ottengono i seguenti tempi di risposta:

THL 101x0 = 0.90ns

TLH 101x0 = 1.02ns

Poiché nella transizione di salita che in quella di discesa si troveranno due transistori a risentire di

effetto body, questi due ritardi sono molto prossimi tra loro, ma entrambi maggiori del caso a gamma

nullo.

- progetto ad area minima

Nel progetto portato avanti finora, l'ingombro totale in termini di area occupata dal circuito era di

A = ( 15 ∗ 4 + 7.5 ) µm 2 + ( 6 ∗ 3 + 3 + 2 ) µm 2 = 67.5 µm2 + 23 µm2 = 90.5 µm 2

E' possibile ridurre drasticamente l'area occupata seguendo un approccio ad area minima, in cui si

sceglie per tutti i transistori del circuito un rapporto d'aspetto (W/L) = 2/1. L'area totale che verrà

occupata sarà in questo caso pari a

Amin = 10 ∗ 2 µm2 = 20 µm2

circa 5 volte più piccola del circuito precedente. Si è supposto una feature size minima di 1µm2 .

Questa riduzione di area occupata causerà una riduzione delle proprietà di conduzione dei

transistori, dando luogo a tempi di risposta più grandi. In particolare, per la rete di pull-down sarà

lecito aspettarsi nel caso peggiore (3 transistori in serie) un tempo di scarica pari a circa 3 volte quello

dell'invertitore fondamentale (che ricordiamo essere Tfond = 0.7ns; come al solito si suppone una

capacità di carico di 0.1pF):

THL = 3 ∗ 0.7 ns = 2.1 ns

Allo stesso modo abbiamo un aumento del ritardo anche in fase di carica, che è possibile calcolare

essere nel caso peggiore dell'ordine di:

TLH = 3 (KN/KP) Tfond = 3 ∗ 2.5 ∗ 0.7 ns = 5.25 ns

(poiché abbiamo 3 volte il ritardo dell'invertitore ad area minima).

Come al solito, andando a simulare questo circuito con la configurazione di ingressi ABCDE =

101x0, con "x" segnale oscillante a frequenza 25MHz, si ottiene il seguente diagramma temporale:

I tempi di ritardo trovati sono:

THL 101x0 = 2.03ns

TLH 101x0 = 5.13ns

in soddisfacente accordo con i risultati teorici. Anche qui valgono le stesse considerazioni fatte in

relazione ai tempi di ritardo per l'invertitore ad area minima.

Progetto di un flip-flop RS in tecnologia CMOS

di Orazio Taglialatela Scafati

matricola n° 65/592

Cenni di teoria e progetto circuitale

Il progetto che si svilupperà è quello di un flip flop RS a NOR incrociati. Si tratta di un tipico

esempio di circuito retroazionato in maniera tale da mantenere una certa uscita per un ingresso

cosiddetto "neutro". In questo caso l'ingresso neutro è rappresentato dagli ingressi RS = 00, che lascia

le uscite inalterate:

In condizioni di equilibrio, è /Q = NOT(Q).

Nella teoria delle reti logiche, questa macchina è configurata come asincrona, non avendo bisogno

di un segnale esterno di clock di sincronizzazione per riuscire a mantenere uno stato stabile. La tabella

degli stati per questa macchina è la seguente:

I pallini indicano stati stabili, vale a dire stati in cui la macchina resta indeterminatamente al

persistere di quei particolari ingressi. Lo stato q00 (relativo alla coppia di uscita Q /Q = 0 0) è uno stato

instabile attraverso cui la macchina passa per poter arrivare ad uno stato stabile.

In tecnologia CMOS, lo schema circuitale del flip-flop RS a NOR incrociati è il seguente:

in cui si sono messe in evidenza le uscita delle due porte NOR con le etichette "out1" e "out2".

Per le dimensioni dei transistori ci rifacciamo all'invertitore fondamentale, che assicurava un ritardo

di 0.7ns su una capacità di carico di 0.1pF:

(W/L)P = 2 (5/1) = 10/1

(W/L)N = 2/1

Dal momento che ogni porta NOR costituente è caricata da una capacità di 0.1pF e dal gate di

un'altra porta logica avente una capacità equivalente ben inferiore a 0.1pF, ci si può aspettare per

l'intera macchina un ritardo complessivo paragonabile a quello dell'invertitore fondamentale.

La netlist spice che descrive questa macchina è la seguente, dove per comodità si è inserita la

singola porta NOR in un sottocircuito:

.subckt

NOR

in1

in2

alim

out

MP1

MP2

10

out

in1

in2

alim

10

alim

alim

PMOS1 W=10u L=1u

PMOS1 W=10u L=1u

MN1

MN2

out

out

in1

in2

0

0

0

0

NMOS1 W=2u

NMOS1 W=2u

L=1u

L=1u

.model

NMOS1 NMOS(level=1, lambda=.02, vto=1, kp=25e-6, cgso=200e-12

+ cgdo=200e-12, cgbo=80e-12)

.model

PMOS1 PMOS(level=1, lambda=.02, vto=-1, kp=10e-6, cgso=200e-12

+ cgdo=200e-12, cgbo=80e-12)

.ends

**** descrizione del circuito

Vdd 1

0

5V

X1 R

Q2

1

Q1

NOR

X2 Q1

S

1

Q2

NOR

C1 Q1

0

0.1pF IC=0V

C2 Q2

0

0.1pF IC=5V

V1 R

0

pulse(0V 5V 40n .1n .1n 20n 100n)

V2 S

0

pulse(0V 5V 10n .1n .1n 20n 100n)

Analisi dinamica

L'elaborazione fornisce i seguenti diagrammi temporali:

La rete inizialmente è a riposo con Q /Q = 0 1 (stato fissato per mezzo delle condizioni iniziali sui

condensatori di carico), poi viene sollecitata da un impulso all'ingresso S che la porta in 1 0 ed infine

un impulso in R la riporta in 0 1.

Si noti come per effetto della retroazione, questa macchina in condizioni di equilibrio riesca a

mantenere indefinitamente lo stato raggiunto, comportandosi a tutti gli effetti da elemento di memoria

(statica).

- valutazione dei tempi di commutazione

Di seguito sono mostrate in scala espansa le due commutazioni del flip-flop:

Si noti come queste siano praticamente coincidenti a patto di invertire i ruoli dei due segnali. I

tempi di risposta sono:

1) commutazione 01 → 00 → 10: la prima variabile a commutare è /Q, e si ha

T /Q HL = 0.75 ns

T Q LH = 1.9 ns

2) commutazione 10 → 00 → 01: la prima variabile a commutare è Q, e si ha

T Q HL = 0.75 ns

T /Q LH = 1.9 ns

Il ritardo sulla prima variabile che commuta coincide praticamente con quello dell'invertitore

fondamentale, come era auspicabile. Quello sulla seconda variabile è pari all'incirca al doppio, poiché

questa riesce ad evolvere solo dopo la quasi completa commutazione della prima variabile. E' da dire

che i valori ottenuti sono leggermente più grandi di quelli attesi poiché l'effettiva capacità equivalente

che carica ogni porta NOR è maggiore di 0.1pF, dovendosi considerare anche il contributo (peraltro

piccolo) dell'altra porta.

In definitiva il ritardo della macchina nel suo complesso valido per entrambe le uscite lo si può

assumere pari alla media dei due ritardi (assumendo come consuetudine un duty-cycle del 50%):

T = ( T 01 → 10 + T 10 → 01 ) / 2 = 1.3 ns

Qualora la rete venisse inavvertitamente sollecitata da un segnale RS = 11, questa si porterebbe

nello stato di uscita Q /Q = 00, con un tempo paragonabile a quello della commutazione più veloce, dal

momento che in queste condizioni commuterebbe una variabile soltanto.

- considerazioni sulla potenza media dissipata:

Si è eseguita l'analisi in transitorio sollecitando gli ingressi R,S con segnali alternativamente attivi a

varie frequenze. Una prima stima teorica prevede per la potenza media dissipata un valore di

<PDISS> = 2 f C VDD2

poiché in un periodo bisogna considerare il processo di carica e scarica di due capacità equivalenti

(qui fissate pari a 0.1pF).

I valori riscontrati dall'elaborazione numerica sono (il pedice "num" sta ad indicare l'output di

un'elaborazione numerica, per distinguere il valore da quello teorico):

a f = 5MHz:

a f = 12.5MHz:

a f = 25MHZ:

<PDISS>num = 34.2µW

<PDISS>num = 89.3µW

<PDISS>num = 155µW

laddove

laddove

laddove

2 f C VDD2 = 25µW

2 f C VDD2 = 62.5µW

2 f C VDD2 = 125µW

Gli scostamenti dai valori teorici non superano il 30% della <PDISS>num e sono dovuti a due motivi:

• presenza di correnti di corto circuito

• le capacità equivalenti all'uscita delle porte NOR sono leggermente maggiori di 0.1pF

Analisi di un invertitore ECL

di Orazio Taglialatela Scafati

matricola n° 65/592

Descrizione del circuito

Il circuito cui si farà riferimento è il seguente:

L'uscita V o1 è quella invertente, mentre Vo2 è la non invertente. La tensione di riferimento Vrif è

generata dal seguente circuito, in cui sono presenti due transistori bipolari connessi a diodo:

Questo circuito per la generazione della tensione di riferimento fornisce un'adeguata

compensazione alle variazioni di temperatura e di tensione di alimentazione, ed è necessario a causa

dell'elevatissima sensibilità della porta ECL. Inoltre lo stadio emitter-follower (componenti Q5 ed R5)

funge da buffer tra la cascata R3 - Q6 - Q7 - R4 e gli invertitori collegati al terminale Vrif.

La tensione di riferimento nominale per i valori scelti dei componenti è di -1V, avendo supposto

una caduta di tensione sulle giunzioni base-emettitore pari a 0.7V.

La netlist spice associata a questo oggetto è la seguente:

invertitore ECL

** descrizione dell'invertitore

Vin

Vee

in

0

0

1

5.2V

R1 o1

R2 o2

Rc1

Rc2

Ree

1

1

0

0

2

18k

18k

3

4

1

1.85k

2k

11.7k

Q1

Q2

Q3

Q4

in

rif

3

4

2

2

o1

o2

npn1

npn1

npn1

npn1

3

4

0

0

** descrizione del riferimento di tensione

R3 0

R4 7

R5 rif

5

1

1

1k

11.7k

25k

Q5 0

Q6 5

Q7 6

5

5

6

rif

6

7

npn1

npn1

npn1

Il modello npn1 è relativo al transistore commerciale CA3045. Si può agire sulla temperatura del

circuito attraverso la direttiva .option temp=xx (il valore di default per questo parametro è 27°C

ovvero 300K).

Analisi statica

Caratteristiche di trasferimento a T= 27°C

L'analisi dc di questo circuito alla temperatura T= 27°C mostra una debolissima dipendenza della

tensione di riferimento dalla Vin dovuta alla corrente di base non nulla del transistore Q2:

Si assumerà la tensione di riferimento pari al punto medio tra i valori negli stati di ingresso alto e

basso: Vrif = (-1.005 - 1.002) / 2 = -1.003V, praticamente pari al valore nominale di -1V.

Analizzando i risultati numerici ottenuti, si assumeranno i seguenti livelli logici di tensione:

VOL= -1.29V

VOH= -0.73V

Il punto medio tra questi due valori è

( VOL + VOH ) / 2 = -1.01V

praticamente coincidente con V rif = -1V, che si troverà quindi al centro dell'escursione logica.

L'ampiezza dell'escursione logica per questo circuito è pari a

∆V = VOH - VOL = 560 mV

ed è molto piccola se confrontata con le ampiezze tipiche dei circuiti MOS, che sono dell'ordine

dei Volt. Questo è il motivo dell'elevata sensibilità del circuito ECL e della necessità di un regolatore

di tensione per compensare le eventuali derive della tensione di riferimento e di alimentazione.

I valori trovati analizzando il vettore deriv(o1) di V IL e VIH ed i relativi margini di rumore sono i

seguenti:

VIL= -1.08V

NML = VIL - VOL = 0.210V

VIH= -0.922V

NMH= VOH - VIH = 0.192V

Teoricamente si erano previsti dei valori NM L = NMH = 0.22V.

analisi con una batteria per la generazione della tensione di riferimento (T= 27°C)

Supponiamo ora di sostituire al circuito di generazione della tensione di riferimento una batteria di

valore Vrif = -1V:

** circuito per la generazione della tensione di riferimento

Vrif

rif

0

-1V

Si hanno i seguenti livelli di tensione e i margini di rumore:

VOL = -1.29V

V IL= -1.07V V IH= -0.919V V OH= -0.73

NML= 0.220V NMH=0.190V

Anche in questo cosa l'ampiezza dell'escursione logica è di 560 mV, dato che i livelli logici di

tensione non sono cambiati.

potenza statica dissipata al variare della tensione di ingresso (T=27°C - circuito con regolaz. di

tensione)

A T= 27°C si ottiene il seguente diagramma della potenza statica dissipata al variare della

tensione di ingresso, dato dal prodotto di VEE per la corrente erogata dall'alimentazione:

I valori di potenza statica nei due stati logici sono

PSL = 6.38 mW @ Vin = -1.29V

PSH = 6.51 mW @ Vin = -0.73V

e supponendo un duty-cycle per l'onda in ingresso del 50%, si ottiene una potenza media di

<PS> = ( PSH + PSL ) / 2 = 6.44 mW

Per ottenere la potenza dissipata dal solo invertitore, si considerano le correnti che circolano nei

vari rami di questo:

Per un duty-cycle del 50%, i valori medi delle correnti erogate dall'alimentazione sono:

<I(R EE)> = 309 µA

<I(R1)> = <I(R2)> = 232 µA

E la potenza media dissipata dal solo invertitore è di

<PS>0 = VEE ∗ ( <I(REE)> + <I(R1 )> + <I(R2 )> ) = 4.02 mW

Si noti come le potenze in gioco in questo caso siano molto più grandi delle potenze statiche

dissipate dai circuiti NMOS (dell'ordine dei decimi di mW) e dai circuiti CMOS (esattamente zero).

Caratteristiche di trasferimento a T= 47°C

Le stesse analisi sono ora compiute aumentando la temperatura di 20°C, fino al valore T1 = 47°C.

La tensione di riferimento ha in questo caso il seguente andamento in funzione di V in:

Il punto medio tra i valori negli stati di ingresso basso e alto è Vrif' = (-0.978 - 0.974) / 2 = 0.976V, in aumento di 24mV rispetto al valore -1V. E' da notare che l'analisi teorica aveva previsto per

questa tensione un aumento di 1.5mV/K ∗ 20K = 30mV.

Le caratteristiche di trasferimento sono le seguenti:

I valori dei livelli logici sono in questo caso:

VOL' = -1.26V

V OH' = -0.7V

il punto medio sarà

( VOL' + V OH' ) / 2 = -0.98 V = Vrif'

La tensione di riferimento si troverà ancora una volta al centro dell'escursione termica, come era

auspicabile in virtù della regolazione di tensione fornita dal circuito di generazione di V rif.

L'ampiezza dell'escursione logica è ancora di

∆V= VOH' - VOL' = 560 mV

Per quanto riguarda i margini di rumore si ha:

V IH' = -0.890V

VIL' = -1.06V

NML' = 0.200V NMH'= 0.190V

è da notare come questi siano rimasti quasi inalterati dopo un aumento di temperatura di 20°C. In

una rappresentazione visiva ecco quanto accade:

L'aumento di temperatura ha provocato una pari traslazione (numericamente di 24mV in salita) di

tutti i valori notevoli della caratteristica di trasferimento, lasciando praticamente inalterati i margini di

rumore. In effetti le caratteristiche di trasferimento restano simmetriche intorno al punto Vrif,

qualunque valore questo assuma, a patto che tutti i livelli di tensione restino confinati nell'intervallo (VEE, 0V).

analisi con una batteria per la generazione della tensione di riferimento (T= 47°C)

Con una batteria di riferimento, a T 1= 47°C si hanno le seguenti caratteristiche di trasferimento:

Si nota come queste siano leggermente sbilanciate rispetto al valore di -1V; in particolare si

trovano i seguenti valori notevoli:

VOL'= -1.26V

V IL'= -1.08V V IH'= -0.915V V OH'= -0.7V

NML '= 0.180

NMH'= 0.215

L'ampiezza dell'escursione logica è ancora una volta pari a ∆V' = VOH' - VOL' = 560 mV. Infatti

rispetto al caso con circuito di compensazione della temperatura, i livelli logici non sono cambiati,

mentre è cambiata solo la simmetria intorno al punto centrale dell'escursione logica.

Questo lo si può notare constatando come il margine di rumore NML sia diminuito rispetto al

valore che aveva a 27°C e quello NMH sia aumentato; il punto medio tra VOL' e VOH' è

( VOL' + VOH' ) / 2 = -0.98V

e non è più coincidente con Vrif. Inoltre si ha che

Vo1 = -0.959V @ Vin = -1V

Vo2 = -0.982V @ Vin = -1V

mentre con il circuito di compensazione delle derive termiche era sempre

Vo1 = Vo2 = Vrif @ Vin = (VOL + VOH) /2 = V rif

E' immediato notare la asimmetria dal seguente profilo dei livelli di tensione:

Questo sbilanciamento è dell'ordine delle decine di mV, ma può comportare ugualmente un

problema dato che l'escursione logica è molto ristretta per la logica ECL.

potenza statica dissipata (T= 47°C - circuito con regolaz. di tensione)

I valori di potenza statica dissipata dal circuito nei due stati logici sono

PSL' = 6.46mW

PSH' = 6.58mW

per una potenza media pari a

<PS>' = (P SL' + PSH') / 2 = 6.52mW

Dal confronto con il valore che questa aveva a T= 27°C, il coefficiente di temperatura di <P S> può

essere assunto pari a 4µW/K.

Analisi dinamica

valori teorici

L'analisi teorica approssimata prevede per i ritardi della porta dei valori di

THL = TLH = 0.69 RC CT

dove R C è la resistenza di collettore sul ramo di interesse, e CT è la somma delle capacità di

svuotamento associate alle giunzioni base-collettore CCB e collettore-substrato CCS che insistono sul

nodo di interesse:

sul ramo di Q 1 si avrà CT1= CCB1 + CCB3 + CCS1

sul ramo di Q 2 si avrà CT2= CCB2 + CCB4 + CCS2

A rigore, queste capacità di svuotamento dipendono dalla tensione inversa applicata alla giunzione

stessa, ma in via semplificativa le si possono considerare costanti e coincidenti con i valori a

polarizzazione nulla.

Per il modello di transistore bipolare usato finora si sono fissati i seguenti valori:

CCB =0.992pF, CCS = 0F

quindi useremo il valore

CT = 2 CCB + CCS = 1.98pF

Si avranno allora per le tensioni sui collettori di Q1 e Q2 dei ritardi teorici approssimativamente

pari a

TP1 = 0.69 ∗ 1.85∗103 ∗ 1.98 ∗ 10-12 = 2.52ns per la v C1

TP2 = 0.69 ∗ 2∗103 ∗ 1.98 ∗ 10-12 = 2.73ns per la v C2

supponendo che gli inseguitori di emettitore seguano istantaneamente le tensioni sui collettori,

questi ritardi si rifletteranno inalterati sulle due uscite vo1 e vo2.

risultati della elaborazione numerica

• singolo stadio non caricato

Di seguito sono riportate le forme d'onda dell'ingresso applicato e delle uscite:

Ed ecco in scala espansa le commutazioni della porta:

Si noti la presenza degli spikes sull'uscita invertente in concomitanza delle variazioni della

tensione di ingresso, dovuti all'accoppiamento tra Vin e VC1 (e quindi tra Vin e Vo1 ) attraverso la

capacità CCB1 . Questi sono assenti nella uscita non invertente poiché non esiste percorso diretto tra

l'ingresso e l'uscita Vo2.

I ritardi di propagazione trovati sono:

per la tensione vo1: THL1 = 3.2ns, TH1 = 4.2ns

per la tensione vo2: THL2 = 2.9ns , TLH2 = 1.9ns

Per quanto detto a proposito della motivazione della presenza degli spike su Vo1 , si assume

chequesti raggiungano il loro valore di picco in un tempo circa pari alla durata della salita o discesa

del segnale in ingresso Vin (scelto pari a 1ns). Dopodiché le fasi di scarica e carica vere e proprie

partono da questi valori di picco, che sono maggiori di V OH e minori di VOL:

Questo è congruente con i risultati numerici, che mostrano dei ritardi di commutazione sulla uscita

invertente di poco più di 1ns più grandi di quelli sulla uscita non invertente.

singolo stadio con capacità di carico

Caricando l'uscita invertente Vo1 con capacità di diversi valori, si ottengono i seguenti tempi di

risposta per questa uscita:

capacità da 1pF:

THL = 3.6ns

TLH = 4.4ns

THL/TLH= 0.818

capacità da 2pF:

THL = 4.3ns

TLH = 4.6ns

THL/TLH=0.934

capacità da 3pF:

THL = 5.4ns

TLH = 4.7ns

THL/TLH=1.15

capacità da 4pF:

THL = 6.7ns

TLH = 4.9ns

THL/TLH=1.37

capacità da 8pF:

THL = 11.9ns

TLH = 5.3ns

THL/TLH=2.24

Si nota come all'aumentare della capacità il ritardo nella transizione in discesa sull'uscita

invertente aumenta molto più velocemente di quella in salita. Per valori di capacità inferiori a circa

3pF le commutazioni possono ritenersi sufficientemente simmetriche mentre dai 4pF in su la

transizione in discesa comincia a farsi notevolmente più lenta di quella in salita, la quale

approsimativamente resta invariata.

La seguente sovrapposizione di diagrammi temporali rende visibilmente apprezzabile questo

aspetto:

Il motivo di questo comportamento è immediatamente spiegabile studiando l'andamento della

tensione VBE3 del transistore Q3, costituente lo stadio di uscita per il segnale invertente:

Durante la fase di scarica della capacità di carico CL, il transistore Q3 è interdetto poiché la

costante di tempo R1 CL sul nodo di emettitore è più grande di quella RCCT sul nodo di base

(supponendo una CL sufficientemente alta), per cui la tensione VB3 diminuisce più velocemente della

VE3 e Q3 si spegne. In queste condizioni, l'unico modo che ha CL per scaricarsi è attraverso la

resistenza R1 e la costante di tempo associata è R1CL. Durante la fase di carica invece, il transistore Q3

fornisce una corrente sufficientemente indipendente dalla capacità di carico, ed il transitorio di salita

avviene sostanzialmente con la costante di tempo RCCT < R1 CL.

• doppio stadio

A questo punto, si è caricata l'uscita invertente dell porta ECL con una seconda porta con uguali

parametri e collegata allo stesso circuito di riferimento di tensione della prima:

Per convenienza, nella netlist Spice si è inclusa la porta ECL in un sottocircuito:

** invertitore ECL

.subckt ECL_gate in

R1

o1

alim

R2

o2

alim

Rc1

0

3

Rc2

0

4

Ree

2

alim

rif o1 o2 alim

18k

18k

1.85k

2k

11.7k

Q1

Q2

Q3

Q4

.ends

2

2

o1

o2

*****

Vin

Vee

X1

X2

3

4

0

0

in

rif

3

4

npn1

npn1

npn1

npn1

descrizione del circuito

10

0

pulse( -1.29, -0.73, 10n, 1n, 1n, 50n, 1u )

0

1

5.2V

10

20

30

31

1

ECL_gate

30

20

o

o1

1

ECL_gate

** riferimento di tensione

R3

0

5

1k

R4

7

1

11.7k

R5

20

1

25k

Q5

0

5

20

npn1

Q6

5

5

6

npn1

Q7

6

6

7

npn1

****

Applicando in ingresso il seguente impulso, con tempi di salita e di discesa pari a 1ns:

si ottengono le seguenti risposte sui nodi di uscita del primo e del secondo stadio

Si noti la presenza di un doppio spike nella uscita del secondo stadio, dovuto al fatto che ad uno

spike all'ingresso di questo stadio corrisponde uno spike in uscita nello stesso verso, ed inoltre un

secondo spike di verso opposto è dovuto all'accoppiamento tra in e out del secondo stadio.

I ritardi di commutazione trovati sono:

sulla uscita del primo stadio: T HL1 = 3.3ns, TLH1 = 3.6ns

sulla uscita del secondo stadio: TLH2 = 6.4ns, THL2 = 6.8ns

ovviamente i ritardi sulla uscita del secondo stadio sono approssimativamente pari al doppio di

quelli sulla uscita del primo.

Analisi di un invertitore TTL

di Orazio Taglialatela Scafati

matricola n° 65/592

Descrizione del circuito

L'invertitore TTL standard è mostrato di seguito; come è noto, esso è composto da tre stadi: quello

di ingresso (transistore Q1, che funge da booster per Q3), quello invertente (transistore Q3 e resistori

RC e RE), quello di uscita (stadio totem-pole composto dai transistori Q 2 e Q4, più un diodo D1 che

assicura l'interdizione di Q4 nello stato basso in uscita, e un resistore RS che limita la corrente iniettata

nel collettore di Q4 qualora l'uscita fosse accidentalmente corto-circuitata a massa):

Dato che anche in condizioni statiche la porta TTL assorbe al suo ingresso una corrente non

trascurabile, per una corretta analisi questo circuito deve essere opportunamente caricato da una

seconda porta, in modo da far sì che i transistori che formano lo stadio totem-pole abbiano un corretto

comportamento alternante (quando uno conduce, l'altro si spegne e viceversa).

La seguente netlist Spice descrive il circuito caricato da una seconda porta TTL identica alla

prima:

Invertitore TTL

Vcc

1

0

Vin

in

0

*** primo stadio

Q11

4

3

Q12

out

6

Q13

5

4

Q14

7

5

5V

in

0

6

8

npn1

npn1

npn1

npn1

R1B

R1C

R1E

R1S

1

1

6

1

3

5

0

7

4k

1.6k

1k

130

D1

8

out

diode

*** secondo stadio

Q21

24

23

Q22

29

26

Q23

25

24

Q24

27

25

out

0

26

28

R2B

R2C

R2E

R2S

1

1

26

1

23

25

0

27

4k

1.6k

1k

130

D2

28

29

diode

npn1

npn1

npn1

npn1

I nodi del secondo stadio seguono la numerazione in figura, mentre quelli del secondo stadio sono

numerati da 23 a 29. I nodi di ingresso e di uscita sono indicati rispettivamente con in e out.

Analisi statica

Caratteristica di trasferimento e considerazioni sulle regioni di funzionamento dei transistori

Eseguendo l'analisi dc da 0 a 5V, otteniamo la seguente caratteristica di trasferimento, che mostra

il tipico andamento a due spezzate della porta TTL ed i relativi modi di funzionamento dei transistori

I livelli di tensione notevoli per questa porta sono:

VOL= 0.058V

V IL= 0.72V

VIH= 1.73V

VOH= 3.65V

I livelli V IL, V1 e VIH sono relativi ai seguenti modi di funzionamento dei transistori Q2 e Q3:

• nella regione VIL < Vin < V1, il transistore Q2 è interdetto e Q 3 funziona da amplificatore a

emettitore comune con una resistenza di emettitore RE (in questo caso il transistore Q4 lavora

anch'esso in regione attiva e funge da emitter -follower).

• nella regione V1 < Vin < VIH, entrambi i transistori Q2 e Q3 funzionano da amplificatori ad

emettitore comune e l'amplificazione complessiva è data dal prodotto delle amplificazioni (per cui

la pendenza della caratteristica è maggiore).

Diagramma delle tensioni VBE2 e VBE3 in funzione di V in:

Per alti valori di Vin entrambi i transistori sono saturati con VBE SAT2= 1.04V, VBE SAT3= 0.90V.

Potenza statica dissipata

Al fine di determinare la potenza dissipata dalla porta TTL in condizioni statiche, è stata eseguita

una seconda analisi dc della porta non caricata.:

I valori di potenza statica dissipata nei due stati logici sono:

PH = 4.99 mW @ Vin = 0.058V

PL = 15.5 mW @ Vin = 3.65 V

Supponendo un duty-cycle del 50%, si ha la seguente potenza media dissipata:

<P> = (PH + PL ) / 2 = 10.2 mW

E' da notare come la potenza abbia un picco di circa 100mW (!) nel range di valori di tensione per

cui i transistori Q2 e Q3 si trovano entrambi in regione attiva.

Caratteristica di ingresso

E' stata trovata la caratteristica di ingresso I in(Vin) = -I E1(Vin) della porta per diversi valori di βR:

Si noti come per ingresso basso la porta eroghi una corrente indipendente da βR (Q1 è infatti in

saturazione diretta), mentre per ingresso alto assorbe una corrente altamente dipendente da βR:

teoricamente, se si trascura la dipendenza delle tensioni VBC1, VBE2, VBE3 dalla corrente iniettata in

base a Q3, si ottiene un valore per la corrente di base di Q1 pari a (avendo usato per V BE2,SAT e VBE3,SAT

i valori trovati nella sezione precedente, e VBC1= 0.7V poiché Q 1 opera in zona attiva inversa per

ingresso alto):

IB1 = (VCC - (VBE1 + VBE3,SAT + VBE2,SAT) ) /RB = (5V - (.7V + .9V + 1.04V)) / 4kΩ

IB1= 0.59mA

Quindi

-IE1 = βR IB1 = 0.59mA ∗ βR

Caratteristiche di uscita e fan-out della porta

Dato che la porta TTL è interessata al suo ingresso da una corrente non trascurabile in entrambi

gli stati logici, vogliamo stabilire quanto una eventuale corrente di carico Iout della porta influisca sulla

sua tensione di uscita Vout .

A tal fine si è considerata la porta nei suoi due stati di ingresso e si è eseguita una analisi dc

assumendo come variabile di sweep la corrente di carico Iout . Le simulazioni si riferiscono al caso

βR=0.25.

Dai risultati della sezione precedente si trovano i seguenti valori per la corrente di ingresso della

porta TTL nei due stati di ingresso:

Iin = -0.884 mA @ Vin = V OL = 0.058V

Iin = 0.141mA @ Vin = VOH = 3.65 V

• stato di ingresso basso

Se si fissa Vin = V OL = 0.058V si ottiene la seguente curva di uscita della porta TTL:

Si nota come all'aumentare della corrente di carico, la tensione di uscita per Vin=0.058V

diminuisca rispetto al suo valore di 3.65V. Poiché Q2 in questo stato è spento, la corrente di uscita Iout

è direttamente erogata dal transistore Q1 operante in zona attiva, e

Vout = RC Iout / (βF+1) + VBE1 + V D1

Se si considera una caduta trascurabile su RC, si ha che la tensione di uscita è legata alle tensioni

di giunzioni pn polarizzate direttamente; di conseguenza si ha una dipendenza molto debole della

tensione di uscita dalla corrente Iout (come si può evincere dal grafico in alto, per cui la tensione Vout

ha una variazione di circa 1V per un aumento di un fattore 100 su Iout).

Assumendo accettabile un valore di tensione Vout tale che la giunzione BE del transistore Q1 della

generica porta a valle resti inversamente polarizzata, e che la corrente di base di quest'ultimo abbia una

dipendenza trascurabile da Vout (per cui VB1= 2.64V), si deve assicurare che

→

Vout > 2.64V

Iout < 11.5mA

Se si assume che ogni porta assorba una corrente di 0.141mA, si trova il fan-out della porta TTL

nello stato alto in uscita:

0.141mA ∗ N < 11.5 mA →

N ≤ 81

I calcoli manuali avevano fornito un valore da non superare per N di 185. Questa discrepanza è

dovuta all'approssimazione di ritenere nei calcoli manuali delle tensioni VBE4 e VD1 costanti con Iout e

pari a 0.7V. Questa approssimazione porta a risultati molto grossolani, dato l'ampio range di

variabilità di Iout nel caso in esame (da 0.141mA a 11.5mA).

• stato di ingresso alto

Nello stato basso in uscita, ogni porta a valle eroga una corrente di 0.884mA, e questa ha una

dipendenza non trascurabile dalla tensione Vout , come si evince dal grafico presentato nella precedente

sezione. Questo rende ancora meno preciso il calcolo manuale del fan-out nello stato alto in ingresso.

La caratteristica di uscita in questo stato è la seguente:

Si noti come questo andamento sia proporzionale a quello del βFOR del transistore Q2; infatti

βFOR2 = IC2 / IB2 = Iout ( Vout ) / I B2

dove si è supposto I B2 indipendente da V out.

Se si assume 0.15V come valore della tensione bassa in uscita da non superare per questa porta,

allora dal grafico si evince che deve essere

I out < 10.2mA

Tornando ora al diagramma della corrente assorbita dalla singola porta in funzione della sua

tensione si ingresso, si nota che

IE1 = 0.988mA @ Vin = 0.15V

per cui deve essere

N ∗ 0.988mA < 10.2mA →

N ≤ 10

Questo mostra come il fan-out sia sostanzialmente legato alla degradazione dell'uscita nello stato

basso, essendo qui l'uscita molto più sensibile alle variazioni della corrente I out rispetto al caso

precendente di uscita alta.

Analisi dinamica

Previsioni teoriche

Durante la transizione basso → alto in uscita, i transistori Q2 e Q3 devono entrambi uscire dalla

condizione di saturazione, e di conseguenza sono soggetti ad un certo tempo di storage. Ma mentre lo

spegnimento del transistore Q3 è agevolato dalla presenza di Q1 (che assorbe durante questa fase una

corrente considerevole dalla base di Q3), il transistore Q2 può solo scaricarsi attraverso il resistore RE

con una corrente di base relativamente bassa, e ciò implica un tempo di storage maggiore:

Se si assume come nella sezione precedente una corrente IB1 ≅ 0.59mA per lo stato alto in

ingresso, si trova che nel momento in cui l'ingresso diviene basso, i transistori Q2 e Q3 vengono

scaricati da delle correnti di base pari a

I BR3 = - 0.59mA * βF = -23.6mA

IBR2 = - VBE2 SAT / RE = -1.04mA

da cui si può prevedere un tempo di immagazzinamento per Q3 trascurabile rispetto a quello di Q2

(dalle espressioni analitiche per il tempo di storage tS si trova infatti che tS2≅ 4ns e tS3≅ 0.2ns).

Una volta smaltite le cariche in eccesso nelle basi di Q2 e Q 3, può partire la fase di salita vera e

propria, per la quale si può prevedere un ulteriore ritardo t* necessario per il caricamento della

capacità equivalente sul morsetto di uscita.

Nella transizione alto → basso in uscita, invece, lo spegnimento del transistore Q 4 (che deve

passare dalla regione diretta attiva alla interdizione) è agevolato dalla corrente abbastanza elevata

assorbita dal collettore di Q3 e la commutazione in discesa avviene più velocemente di quella in salita.

Risultati dell'elaborazione numerica

Per valutare numericamente la risposta dinamica dell'invertitore TTL caricato da una seconda

porta, lo si è sottoposto ad un impulso di durata 50ns:

I tempi di risposta sono stati trovati essere pari a T HL = 3.2ns, TLH = 6.9ns

tempo medio di propagazione: T = ( THL + TLH ) / 2 = 5-05 ns

prodotto ritardo-potenza PDP = <P> T = 10.2 mW ∗ 5-05 ns = 51.5 pJ

Questo è un valore per il PDP davvero notevole rispetto ad altre porte logiche viste, essenzialmente a

causa dell'elevata potenza statica dissipata dalla porta.

Come ci si aspettava, il transitorio di discesa è più veloce di quello di salita, e durante quest'ultima

fase lo spegnimento di Q3 è più veloce di quello di Q2, come si può capire osservando il diagramma

temporale delle correnti che vengono pompate fuori dalle basi dei due transistori:

Si nota come all'atto dello spegnimento, |IB3 | abbia un picco di 8mA ed il relativo transitorio si

estingue prima di |IB2|, che ha un picco di soli 3mA.

Inoltre sappiamo che la carica da smaltire per il transistore Q2 per uscire dalla saturazione è

maggiore di quella di Q3 (Q2 si "spinge" in saturazione più di Q3, rispettivamente con βFOR2 = 0.483 e

βFOR3 = 3.42). Queste constatazioni ci spiegano il motivo per cui il transitorio di spegnimento di Q3 è

tanto più veloce di quello di Q2 da poter essere trascurabile rispetto a questo.

Elaborazione con differenti tempi di transito

Vediamo ora l'effetto sulla risposta dinamica di una variazione sui tempi di transito diretto e

inverso dei BJT; a tale scopo si è eseguita l'analisi in transitorio aumentando di 4 volte prima τF poi τR:

La discesa è influenzata poco dall'aumento di τF e τR, poiché in questa fase il transistore Q4 (che

passa dalla regione attiva alla interdizione) smaltisce le cariche accumulate in base con una costante di

tempo pari a τBF (tempo di ricombinazione diretto in base), agevolato dalla corrente di collettore di Q3.

L'aumento dei tempi di transito ha invece un effetto predominante sulla salita, poiché qui i

transistori Q2 e Q3 devono uscire dalla saturazione smaltendo le cariche in eccesso in base con una

costante di tempo τS legata a τF e τR. A parità di fattore di scala, inoltre, un aumento su τR pesa molto

di più di uno su τF, poiché quest'ultima è sempre trascurabile rispetto alla prima nell'espressione di τS.

Nel diagramma sono stati evidenziati per la commutazione più lenta tre intervalli di tempo:

• ∆1 è relativo allo smaltimento delle cariche in base a Q 3

• ∆2 >> ∆1 è relativo allo smaltimento delle cariche di Q2

• ∆3 è relativo all'intervallo di tempo in cui il transistore Q4 si spinge in saturazione, ed eroga una

corrente costante con Vout > VOH fino allo smaltimento delle cariche in base.

Progetto e confronto di alcuni tipi di celle di

memoria RAM in tecnologia CMOS

di Orazio Taglialatela Scafati

matricola n° 65/592

Descrizione dei vari tipi di cella elementare e dell'amplificatore di lettura

Si studieranno 3 tipi di celle di memoria RAM:

• cella 6T (di memoria statica)

• celle 1T e 4T (di memorie dinamiche)

ognuna considerata insieme al rispettivo circuito di rilevazione di lettura (sense-amplifier). I modelli di

transistori NMOS e PMOS usati in tutta la trattazione sono i seguenti:

.model mosn

nmos(kp=2.5e-5 vto=.7 gamma=.5 lambda=.05 tox=20n

+ cgso= 4e-9 cgdo= 4e-9 cj=2.0e-4 cjsw= 5.0e-10)

.model mosp

pmos(kp=1.0e-5 vto=-.7 gamma=.75 lambda=.05 tox=20n

+ cgso= 4e-9 cgdo= 4e-9 cj=2.0e-4 cjsw= 5.0e-10)

L'alimentazione è stata scelta pari a 3V e si seguirà un approccio ad area impiegata minima.

sense-amplifier

Il sense-amplifier che si userà sarà un semplice latch ad invertitori CMOS con segnale di

attivazione di precarica, del tipo seguente:

Poiché di questo circuito in genere non interessano le variabili interne, esso verrà inserito nelle

netlist spice in forma di sottocircuito:

.subckt

MP1

BL1

MP2

BL2

MN1

BL1

MN2

BL2

MPC

BL1

.ends

SENSE_AMP

BL2

alim

BL1

alim

BL2

0

BL1

0

BL2

PC

alim

alim

alim

0

0

0

BL1

mosp

mosp

mosn

mosn

mosn

BL2

w=10u

w=10u

w=10u

w=10u

w=10u

PC

l=1u

l=1u

l=1u

l=1u

l=1u

Per rendere più sensibile e veloce questo amplificatore, si sono usati dei transistori con W/L=

10/1.

cella 6T (memoria statica):

In figura sono mostrati lo schema logico e quello circuitale della cella elementare 6T.

L'informazione è mantenuta per effetto della retroazione dei due invertitori CMOS, e l'accesso in

lettura e scrittura avviene attivando la word-line WL:

CBL1 e CBL2 sono le capacità equivalenti delle bit-line viste dalla cella. Queste possono avere

valori anche abbastanza elevati (dell'ordine dei decimi di pF o dei pF), poiché connettono insieme un

numero anche molto alto di celle. Alla coppia di bit-line, poi, sarà connesso il sense-amplifier visto

prima.

Questo oggetto, comprensivo di sense-amplifier, è descritto dalla seguente porzione di netlist:

VDD

1

0

3V

MCP1

MCP2

MCN1

MCN2

MA1

MA2

2

3

2

3

BL1

BL2

3

2

3

2

WL

WL

1

1

0

0

2

3

1

1

0

0

0

0

X1 1

BL1

BL2

PC

SENSE_AMP

CBL1

CBL2

BL1

BL2

0

0

.5pF

.5pF

mosp

mosp

mosn

mosn

mosn

mosn

w=1u

w=1u

w=1u

w=1u

w=1u

w=1u

l=1u

l=1u

l=1u

l=1u

l=1u

l=1u

cella 1T (memoria dinamica)

Si tratta di una cella di memoria dinamica, cioè conserva l'informazione sotto forma di carica sul

condensatore CC. Questo schema come è noto, in condizioni di riposo soffre delle correnti di perdita

attraverso le giunzioni pn del MOSFET polarizzate inversamente, che porterebbero alla perdita della

informazione se non si rinfrescasse periodicamente la cella:

La porzione di netlist che descrive questa cella è la seguente:

VDD

MA

CC

M1

1

2

2

VDD

0

WL

0

PC

3V

BL1

50fF

2

X1

1

BL1

BL2

CBL1

CBL2

BL1

BL2

0

0

.5pF

.5pF

0

mosn

w=1u

l=1u

0

mosn

w=1u

l=1u

PC

SENSE_AMP

Si è incluso un transistore fittizio M1 il cui scopo è quello di caricare il condensatore CC ad un

valore iniziale fissato (nell'esempio la cella viene portata in un "1" logico).

Per poter utilizzare il sense-amplifier visto, si è supposta l'esistenza di una seconda bit-line BL2

alla quale non è connessa alcuna cella. Per rendere bilanciato il progetto, sarebbe anche possibile

prevedere una cella dummy connessa alla linea BL2, contenente l'informazione complementare a

quella della cella in esame.

L'utilizzo del sense-amplifier permette non solo di rilevare la presenza o l'assenza di carica sul

condensatore, ma anche di ripristinare il contenuto originario, effettuando l'operazione di rinfresco di

cui si è parlato.

cella 4T (memoria dinamica)

La cella 4T rappresenta un compromesso tra l'economicità della 1T e la velocità della 6T. Essa

sfrutta una coppia di MOSFET incrociati come nella 6T, ma l'informazione è contenuta in una coppia

di condensatori che fungono da carico. Questi conservano sia l'informazione affermata che la negata,

rendendo il circuito bilanciato:

La corrispondente porzione di netlist Spice è la seguente:

VDD

1

0

3V

MN1

MN2

MA1

MA2

22

3

BL1

BL2

3

2

WL

WL

0

0

20

3

C1

C2

21

3

0

0

50fF

50fF

MS1

MS2

1

0

PC

PC

CBL1

CBL2

X1

BL1

BL2

1

0

0

BL1

0

0

0

0

mosn

mosn

mosn

mosn

w=1u

w=1u

w=1u

w=1u

l=1u

l=1u

l=1u

l=1u

2

3

0

0

mosn

mosn

w=1u

w=1u

l=1u

l=1u

.5pF

.5pF

BL2

PC

SENSE_AMP

Analogamente a quanto fatto per la cella 1T, si sono aggiunti due transistori fittizi MS1 e MS2 che

portano la cella, durante la fase di precarica, in uno stato iniziale fissato (nell'esempio,in C1 è

memorizzato un "1", in C2 uno "0").

Operazione di lettura

Per poter leggere il dato dalla cella di memoria, è necessaria una operazione di precarica delle bitline. In questa fase il sense-aplifier viene portato in un punto di equilibrio instabile, ed al rilascio della

precarica un leggero sbilanciamento sulle bit-line lo porterà più o meno velocemente in uno stato

stabile.

Fase di precarica e punto di lavoro iniziale

All'attivazione della linea PC di precarica, il MOSFET M PC fornirà un percorso di corrente tra le

due uscite degli invertitori che costituiscono il latch del sense-amplifier. In un progetto bilanciato (i

due invertitori uguali tra loro), le due uscite v1 e v2 si porteranno ad un livello comune, annullando la

corrente che circola in MPC:

L'esistenza di questo livello comune è garantita dalla natura simmetrica dei due invertitori.

Rifacendoci alla caratteristica di trasferimento dell'invertitore CMOS abbiamo:

Poichè gli NMOS sono più conduttivi dei PMOS, si ha un punto di equilibrio in

v1 = v2= 1.32V < VDD/2