Università degli Studi di Cagliari

Dipartimento di Ingegneria Elettrica ed Elettronica

Laboratorio di Elettronica

Corso di Circuiti Integrati

Anno Accademico 2012/2013

Esercitazione 6

Progetto di un amplificatore a Due Stadi (di Miller) in tecnologia CMOS

0.35μm

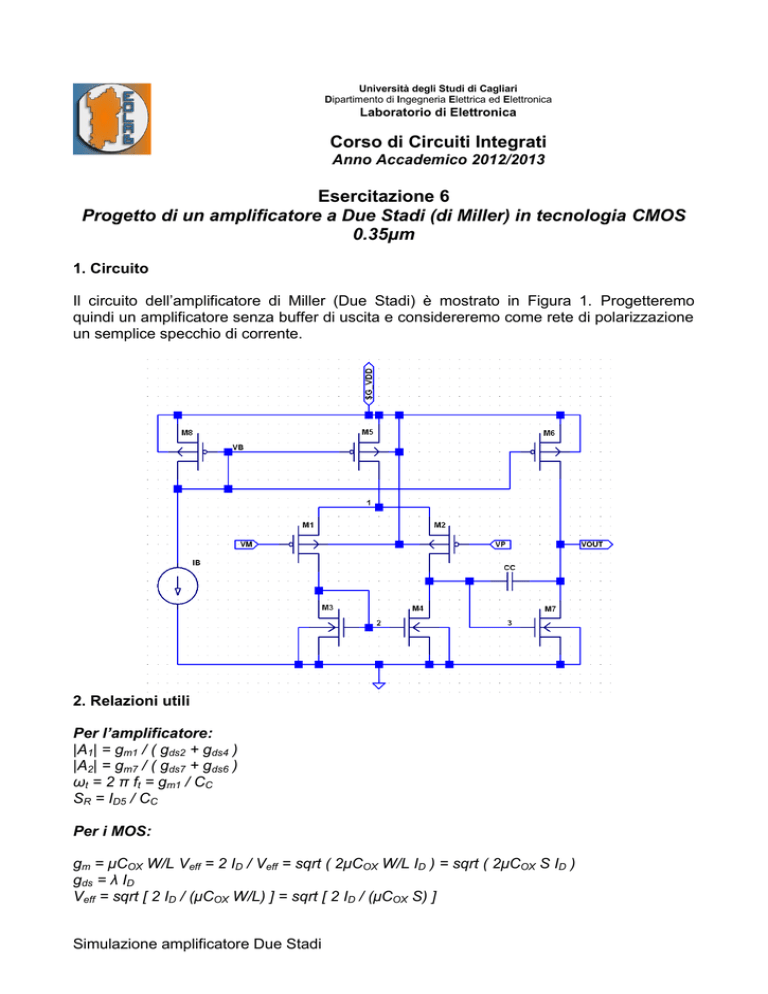

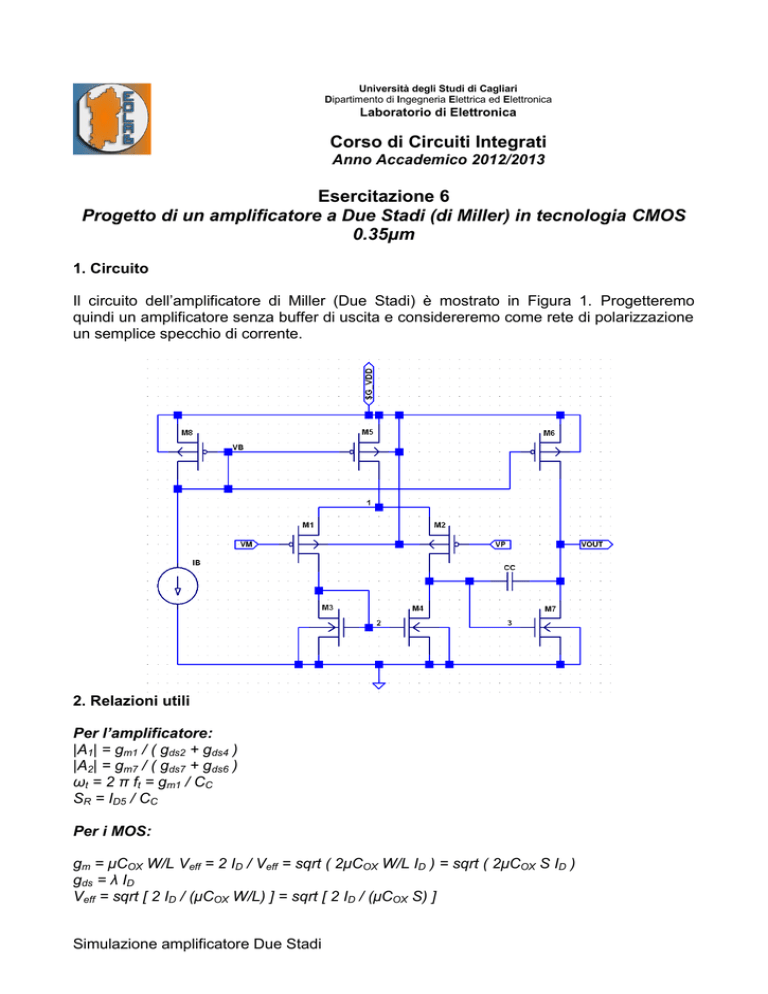

1. Circuito

Il circuito dell’amplificatore di Miller (Due Stadi) è mostrato in Figura 1. Progetteremo

quindi un amplificatore senza buffer di uscita e considereremo come rete di polarizzazione

un semplice specchio di corrente.

2. Relazioni utili

Per l’amplificatore:

|A1| = gm1 / ( gds2 + gds4 )

|A2| = gm7 / ( gds7 + gds6 )

ωt = 2 π ft = gm1 / CC

SR = ID5 / CC

Per i MOS:

gm = μCOX W/L Veff = 2 ID / Veff = sqrt ( 2μCOX W/L ID ) = sqrt ( 2μCOX S ID )

gds = λ ID

Veff = sqrt [ 2 ID / (μCOX W/L) ] = sqrt [ 2 ID / (μCOX S) ]

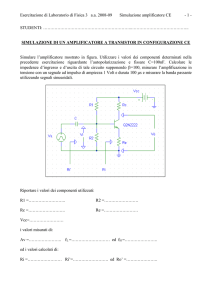

Simulazione amplificatore Due Stadi

3. Parametri

Il primo passo è l’identificazione dei parametri dei transistor, in particolare la uCox e la

VTH, per fare questo si simuli un circuito semplice, con uno specchio di corrente (di tipo P

e di tipo N) costituito da transistor a W/L unitario ma con L almeno pari a 1um e che copia

una corrente nota (dell’ordine dei microampere, ad esempio 10uA) e poi si ricavi la gm. Da

questa, dopo avere ottenuto il valore di VTH, si può ricavare il valore di uCox.

4. Specifiche

Si progetti un amplificatore con le seguenti caratteristiche:

Potenza statica dissipata

Slew-rate

Frequenza a guadagno unitario

Swing di tensione di uscita

Guadagno in continua

PSTAT = 66 μW

SR = 1E+07

ft = 10 MHz

2.5 V

A0 > 70 dB

5. Procedimento

1. Utilizzare MOS con lunghezza di canale pari a 1 μm (minima lunghezza di canale

per MOS non a canale corto).

2. Iniziare ad applicare la prima specifica (sulla potenza) per ricavare la corrente totale

erogata all’amplificatore (senza considerare il circuito di polarizzazione costituito da

M8 e IB). Scegliere poi come ripartire tale corrente sui due stadi (ad esempio si può

partire col suddividere metà della corrente al primo stadio e metà al secondo).

3. Applicare la seconda specifica (slew-rate) per ricavare il valore della capacità di

compensazione.

4. Applicare la terza specifica (frequenza di guadagno unitario) per ottenere la gm della

coppia differenziale. Conoscendo già la corrente ricavare le dimensioni della

coppia.

5. Applicare la quarta specifica (che impone la massima Veff) per ricavare le

dimensioni di M6 e M7 (quindi di M5, M8, M3, M4).

6. Verificare la quinta specifica (A0), ricavando il guadagno del primo e secondo stadio

e verificare quindi che i dimensionamenti ottenuti precedenti siano compatibili con

tale guadagno.

Simulazione amplificatore Due Stadi

PROGETTAZIONE

La progettazione di un amplificatore operazionale richiede il dimensionamento di un gran

numero di parametri, in particolare i W/L di tutti i MOS, il valore delle capacità e delle

resistenze, la corrente di polarizzazione ed altro.

Tali parametri vanno dimensionati in base alle specifiche fornite, che non sempre però

possono essere soddisfatte contemporaneamente. Non esiste un metodo di progettazione

univoco, con una sequenza preordinata di passi da seguire e che porterà sempre alla

realizzazione del progetto finale (come nel caso della progettazione digitale). A seconda

dell’applicazione finale bisogna focalizzare l’attenzione su alcune delle specifiche e

garantire per primo il soddisfacimento di tali vincoli per poi andare via via ad imporre gli

altri.

Nel nostro caso imporremo le specifiche nell’ordine in cui sono state fornite, ipotizzando

che le prime siano le più vincolanti e le più difficili da ottenere. Giunti all’ultima specifica

bisognerà verificare che tutti in vincoli siano stati rispettati. Se così non fosse, bisognerà

tornare sui propri passi e modificare quelle scelte di progetto discrezionali e ritentare.

Il metodo seguito NON è l’unico e non è sempre generalizzabile ma costituisce un buon

esempio di quale sia il processo di progettazione di un amplificatore.

1° specifica – Consumo di potenza statica

Il vincolo sulla potenza dissipata dall’amplificatore impone la massima corrente erogabile

ai due stadi dell’ampificatore:

Pstat = VDD ITOT = 66 μW

=>

ITOT = Pstat / VDD = 150 μA

Essendo ovviamente VDD = 3.3 V

ITOT è la corrente totale a disposizione di entrambi gli stadi, quindi la somma di ID3 e ID6

(abbiamo detto che la specifica riguardava solo la potenza dell’amplificatore). Ora

dobbiamo scegliere come distribuire questa corrente fra i due stadi. La scelta più

semplice, in questo momento, è quella di utilizzare metà della corrente per il primo stadio

e metà per il secondo. Questa scelta è però discrezionale, una scelta di tentativo che

facciamo in mancanza di altri vincoli specifici. Se, via via che aggiungiamo le specifiche, ci

risultasse impossibile soddisfarle tutte potremmo sempre tornare a questo punto e

cambiare la suddivisione della corrente (ad esempio potremmo dare più corrente al primo

stadio per aumentare la gm e meno al secondo per aumentare il guadagno).

Se scegliamo comunque di suddividere equamente le correnti risulterà:

ID5 = 10 μA

ID6 = 10 μA

2° specifica – Slew-rate

Il vincolo sullo slew-rate ci permette di determinare la capacità di compensazione CC, dato

che ormai conosciamo la ID5, infatti:

SR = ID5 / CC

=>

CC = ID5 / SR = 1 pF

CC = 1 pF

Simulazione amplificatore Due Stadi

3° specifica – Frequenza a guadagno unitario

Conoscendo CC, il vincolo sulla ft ci permette di calcolare la gm del primo stadio (gm1).

Dopodiché, ottenuta gm1 e conoscendo ID5 (quindi ID1 e ID2 che sono la metà di ID5)

possiamo determinare il dimensionamento di M1 e M2:

ωt = 2 π ft = gm1 / CC

=>

gm1 = sqrt [ 2 μp COX S1 ID1 ]

S1 = W1 / L1

=>

gm1 = ωt CC = 2 π ft CC = 62.8 E-06 [ A / V ]

=>

S1 = gm12 / ( 2 μp COX ID1 ) = 16 [ m / m ]

W1 = 16 L1

Poiché abbiamo supposto di dimensionare tutti i MOS con L = 1μm possiamo ricavare W1

e W2 (i due transistor della coppia sono uguali). Anche questa è una scelta discrezionale,

quindi potremmo tornare a questo punto e scegliere una L minore nel caso non fosse in

seguito possibile soddisfare le restanti specifiche.

W1 = W2 = 16 μm

4° specifica – Swing di uscita

Vogliamo uno swing di tensione in uscita di almeno 2V, il che vuole dire, supponendo di

centrare il segnale alla metà della tensione di alimentazione (VDD/2), imporre la minima e

massima tensione di uscita:

VOUT,max > VDD/2 + SWING/2 = 2.9 V

VOUT,min < VDD/2 – SWING/2 = 0.4 V

Il concetto dello swing d’uscita è illustrato meglio nella seguente figura:

I vincoli sulla minima e massima tensione di uscita impongono vincoli sulla V eff6 e la Veff7,

infatti sappiamo che l’amplificatore funzionerà correttamente finché sia M6 che M7 restano

in saturazione ossia:

VOUT,max = VDD – Veff6

VOUT,min = Veff7

=>

=>

Simulazione amplificatore Due Stadi

Veff6 = 0.4 V

Veff7 = 0.4 V

Da queste relazioni, e conoscendo la corrente ID6, è possibile ricavare le dimensioni di M6

e M7, infatti:

Veff6 = sqrt [ (2 ID6) / ( μp COX S6 ) ]

W6 = S6 L6 = S6 L = 5 μm

=>

S6 = (2 ID6) / (μp COX Veff62) = 5

Veff7 = sqrt [ (2 ID7) / ( μn COX S7) ]

W7 = S7 L7 = S7 L = 1.25 μm

=>

S7 = (2 ID7) / (μn COX Veff72) = 1.25

La conoscenza di W6 mi permette anche di conoscere W5 e W8, infatti conosco il rapporto

fra le correnti dei MOS e so di conseguenza anche il rapporto fra le loro W visto che i due

MOS hanno la stessa tensione di gate:

ID5 / ID6 = W5 / W6

ID8 / ID6 = W8 / W6

In questo caso semplicemente W5=W6 visto che le due correnti sono uguali (per nostra

scelta). Stesso discorso si può fare per W8, imponendo quindi che la corrente ID8 (I B) sia

uguale a quella di M6. Si potrebbe ovviamente fare una scelta diversa, prendere ad

esempio IB = ID8 = 1μA e poi moltiplicare per 10 tale valore per ottenere i 10μA di M6 ed

in tal caso W8 dovrebbe essere 10 volte più piccolo di W6. Per semplicità sceglieremo

W8=W6

Dalla conoscenza di W7 possiamo invece risalire a W3 e W4, che sono uguali fra loro

visto che si tratta di uno specchio di corrente.

Sappiamo infatti che M3 e M7 hanno praticamente la stessa tensione di gate, dato che il

primo stadio è simmetrico e quindi, per tensione di ingresso differenziale nulla, deve

risultare che ID1=ID2 ossia:

ID3 = ID5

In tale condizione sarà anche che VDS3 = VDS4, ma poiché M3 è connesso a diodo:

VDS4 = VDS3 = VGS3 = VG3

Poiché il drain di M4 è connesso al gate di M7:

VG7 = VD4 = VG3

Se M3 e M7 hanno stessa tensione di gate allora:

ID3 / ID7 = W3 / W7

Sappiamo che M7 conduce la corrente di M6 ossia 10μA, mentre M3 conduce metà della

corrente di M5 ossia 5μA dunque:

W3 = (ID3/ID7) W7 = 0.5 W7 = 0.6 μm

W6 = W5 = W8 = 5 μm

W7 = 1.25 μm

W3 = W4 = 0.6 μm

Simulazione amplificatore Due Stadi

5° specifica – Guadagno in continua

In realtà il circuito è già completamente dimensionato, di conseguenza resta fissato anche

il suo guadagno. Ora dobbiamo verificare che il guadagno ottenuto rientri nella specifica.

In caso affermativo abbiamo terminato la bozza del progetto e possiamo passare alle

simulazioni per verificare il funzionamento, altrimenti bisognerà tornare indietro e

modificare alcune delle scelte nell’ottica di aumentare il guadagno (ad esempio diminuire

la corrente del secondo stadio, oppure aumentare la gm1).

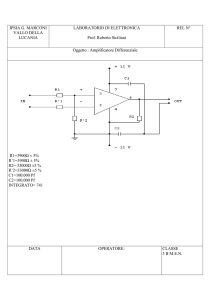

Guadagno del primo stadio:

A1 = gm1 (rds2 // rds5) = gm1 / (gds2 + gds4 )

Conosciamo già gm1, possiamo calcolare gds2 e gds4 conoscendo la corrente e la L dei due

MOS:

gds2 = λ ID2 = 0.07 μ-1

gds4 = λ ID5 = 0.215 μ-1

A1 = 220

Guadagno del secondo stadio:

A2 = gm7 / (gds6 + gds7)

gm7 = sqrt [ 2μnCOX S7 ID7 ] = 50 E-06 A/V

gds6 = λ ID6 = 0.14 μ-1

gds7 = λ ID7 = 0.43 μ-1

A2 = 88

Guadagno dell’amplificatore:

A0 = A1 A2 = 19360 = 86 dB

La specifica sul guadagno è soddisfatta senza dovere fare modifiche al circuito.

Simulazione amplificatore Due Stadi

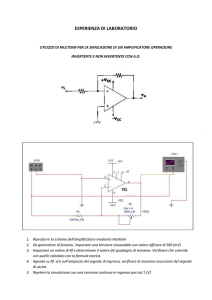

SIMULAZIONE

Tutti i file per la simulazione si trovano nella directory SPICE .

Gli schematici utilizzati sono 3:

opamp

bias

tb_opamp

- Schematico dell’amplificatore vero e proprio

- Schematico del circuito di polarizzazione

- Testbench per la simulazione

Il testbench dovrà ovviamente includere gli altri due schematici di cui è quindi necessario

disegnare il simbolo.

Risposta in frequenza

Per calcolare la risposta in frequenza bisogna fare un’analisi in AC. Bisognerà quindi

mettere un generatore di tensione continua sul morsetto negativo che imponga la tensione

di modo comune (VCM). Come tensione di modo comune scegliamo una tensione pari a

VDD/2 in modo da avere la tensione di ingresso al centro del range di tensioni. Sul

morsetto positivo metteremo un generatore che abbia una componente in continua pari

ancora a VDD/2 ed una componente in AC pari a 1. In questo modo, visto che il guadagno

è il rapporto fra l’uscita e l’ingresso, essendo l’ingresso unitario, l’uscita V OUT rappresenta

direttamente il guadagno. Graficando in modulo e fase VOUT si ottengono i diagrammi di

Bode dell’amplificatore.

Abbiamo ottenuto un guadagno di circa 72dB, una frequenza di guadagno unitario molto

maggiore dei 10MHz desiderati. Apparentemente, abbiamo quindi rispettato tutte le

specifiche. Il guadagno è minore di quello previsto perché le resistenze rds2, rds4, rds6 e rds7

Simulazione amplificatore Due Stadi

sono minori di quanto calcolato (questo perché la formula usata per le gds è molto

approssimata), mentre le gm1 e gm7 risultano molto simili a quelle desiderate.

La frequenza di guadagno unitario è molto maggiore di quanto atteso perché in

progettazione non abbiamo tenuto conto della presenza dello zero che, come si vede

chiaramente dal grafico, rallenta la pendenza del guadagno stesso. Finché il diagramma

segue la pendenza di -20dB/decade si vede che il punto di attraversamento dovrebbe

essere correttamente 10MHz, ma non appena lo zero fa sentire la sua influenza la

pendenza rallenta e la curva va ad intersecare l’asse più lontano.

Controllando il diagramma della fase si può facilmente verificare che la fase diventa

inferiore a -180° prima che il guadagno diventi inferiore a 1, di conseguenza l’amplificatore

è instabile. Risolveremo questo problema nella prossima esercitazione.

Simulazione amplificatore Due Stadi